## A Carrier-Based Neutral Voltage Modulation Strategy for Seven Level Cascaded Inverters under Unbalanced Dc Sources

## B.Sagar Kumar & B .Pranith Kumar

Assistant Professor Electrical & Electronics Engineeringvaageswari College Of Engineering Karimnagar

**ABSTRACT:***This specific project offers a pulse* widthmodulation technique to achieve balanced line-to-line output voltages and maximize this modulation index inside the linear modulation range the place that the output voltage could be linearly adjusted inside the multilevel cascaded inverter (MLCI) running under unbalanced dclink conditions. Here we are implementing seven level cascade inverter. In these conditions, this linear modulation variety is lowered, and an important output voltage difference may happen as voltage references increase. So that you can analyze these effects, the voltage vector living space for MLCI can be evaluated in depth. From this analysis, the theory behind this output voltage difference is defined, and the ideal linear modulation variety considering the unbalanced dc-link problem is evaluated. After that will, a neutral voltage modulation tactic is proposed to obtain output voltage balancing and also to lengthen the linear modulation range around the greatest reachable point theoretically. In this proposed method, too large of any dclink difference precludes this balancing of the output voltages. This limitation is also discussed. Both this simulations plus the experiments for just a

seven-level phase shifted modulated MLCI pertaining to electric vehicle traction engine drive show that the proposed method will be able to balance line-to-line productivity voltages and also to maximize the linear modulation range beneath unbalanced dc-link disorders.

Keywords: Harmonic Injection, Multilevel Cascaded Inverters (Mlcis), Neutral Voltage Modulation (NVM), Phase-Shifted (PS) Modulation, Space Vector Pulse Width Modulation (PWM) (SVPWM).

**INTRODUCTION** Multilevel L inverters enable the synthesis of a sinusoidal output voltage from several steps of voltages. For this reason, multilevel inverters have low dv/dt characteristics and generally have low harmonics in the output voltage and current. In addition, the switching of very high voltages can be achieved by stacking multilevel inverter modules [1]–[3]. Due to these advantages, multilevel inverters have been applied in various application fields Among various topologies [6]–[10]. for multilevel inverters, the multilevel cascaded inverter (MLCI) structure is one of the prominent topologies because of its simple

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

structure for modularization and fault-tolerant capability. Therefore, MLCIs are used for many applications, such as dynamic voltage restorer, static synchronous compensator (STATCOM), high-voltage energy storage device, photovoltaic medium-voltage inverters, drives, electric vehicle (EV) traction drives. In MLCI applications, a modulation strategy to generate gating signals is very crucial to achieve highperformance control. Regarding this issue, many studies have been conducted, and they are roughly categorized into multilevel selective harmonic elimination pulse width modulation (PWM) (SHEPWM), multilevel carrier-based PWM, and multilevel space vector PWM (SVPWM) methods. Generally, a carrier-based PWM or SVPWM is preferred in applications such as motor drives, where dynamic properties are very important, whereas SHEPWM is preferred in some highpower static power conversion applications. an SVPWM method has been studied to cover the over modulation range in the multilevel inverter. To reduce the common-mode voltage, a multilevel SVPWM has been proposed in . The series SVPWM method has been reported to easily implement SVPWM for the MLCI an SVPWM is proposed for hybrid inverters consisting of neutral point clamp and H-bridge inverters to improve output voltage quality and efficiency. In the proposed

method, the neutral voltage reference, which considers a zero sequence voltage to compensate the output voltage imbalance, and an offset voltage to extend the linear modulation range are easily obtained through simple arithmetic calculations. In the proposed method, too large of a dc-link imbalance precludes the output voltages from being balanced. This limitation is also discussed. In addition, a faulttolerant operation is naturally covered, because the MLCI undergoing an unbalanced dc-link condition can be considered as an MLCI operating under a faulty condition on switch modules. Compared to the existing methods, the proposed strategy is very simple to implement, compensates the output voltage imbalance in real time, and maximizes the voltage utilization of the dc links. Therefore, if this scheme is applied to applications such as EV traction drive systems, the dynamic characteristics can be greatly improved. This paper is organized as follows. In Section II, the voltage vector space.

**II. MULTILEVEL INVERTER** In response to the growing demand for high power inverter units, multilevel inverters have been attracting growing attention from academia as well as industry in the recent decade. Among the best known topologies are the H-bridge cascade inverter, the capacitor clamping inverter

(imbricated cells), and the diode clamping inverter. As reported in the literature, the Hbridge cascade inverter has been used in several practical instances for broadcasting amplifier [4], plasma [3], industrial drive [6] as well as STATCOM [7] applications etc. The main limitation of the H-bridge cascade inverter consists in the provision of an isolated power supply for each individual H-bridge cell when power transfer is demanded. real For STATCOM application, where the isolated supplies are not required, the power pulsation at twice output frequency occurring with the dc link of each H-bridge cell necessitates oversizing of the dc link capacitors. The capacitor clamping inverter, though the three-level scheme of which was published in the early 1980's [8], had been rarely discussed until the introduction of the —imbricated cells [9]. The individual clamping capacitor needs only to smooth the switching frequency ripple voltage and the required capacity for each clamping capacitor is therefore small. However, as the number of level increases, such problems as thermal designing, low-inductance designing, as well as insulation designing of the system will become critical. Medium voltage drives using four-level capacitor clamping inverter has recently been available on the market. The diode clamping inverter, as shown in Fig. 5, published by

different researchers in the early 90's can be deemed as the extension of the neutral-pointclamped (NPC) inverter introduced in the early 80's . Unlike the NPC inverter which has been extensively used today in industrial drives, tractions as well as FACTS systems, the diode clamping inverter is right under investigation. In addition to the dc link unbalance problem identified in the other problems with the diode clamping inverter.

**III. PROPOSED MODULATION TECHNIQUE** The maximum synthesizable voltage in the linear modulation range was evaluated under the unbalanced dc links. In this section, a method is proposed to realize the maximum modulation index in the linear modulation range under these conditions.

A. Traditional Offset Voltage Injection Method The offset voltage injection scheme is a popular technique in three-phase half-bridge inverter applications. The theory behind this is that an offset voltage is incorporated with phase voltage references to implement various PWM schemes in carrier-based PWM by using the fact that line-to-line voltages are applied to a threephase load [43], [44]. For example, the offset voltage v \*sn isinjected to the phase voltage references v \* as, v \*bs, and v \*cs to implement carrier-based SVPWM as in

## International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

$$\begin{split} v^*_{sn} &= \frac{v^*_{\max} + v^*_{\min}}{2} \quad v^*_{\max} = \max\left(v^*_{as}, v^*_{bs}, v^*_{cs}\right) \\ v^*_{\min} &= \min\left(v^*_{as}, v^*_{bs}, v^*_{cs}\right). \end{split}$$

(1)

Then, the pole voltage references v \* an, v \* bn, and v \* cn, which will be converted to PWM duty references, are

$$v_{an}^{*} = v_{as}^{*} - v_{sn}^{*} \quad v_{bn}^{*} = v_{bs}^{*} - v_{sn}^{*} \quad v_{cn}^{*} = v_{cs}^{*} - v_{sn}^{*}.$$

(2)

However, the aforementioned technique may not maximize the linear modulation range in MLCI undergoing unbalanced dc-link conditions.

**B. Proposed NVM Method** If the dc links in an MLCI are unbalanced and the traditional offset voltage injection methods are utilized, the three-phase output voltages may become distorted as the phase voltage reference approaches V 1 ph-max. This is because the traditional methods are not considering unbalanced dc-link conditions. Therefore, even if a phase can synthesize an output voltage reference in the linear modulation range, the other phases can be saturated or go into the ove modulation region. In this situation, a neutral voltage can be produced by the saturated or over modulated phase.

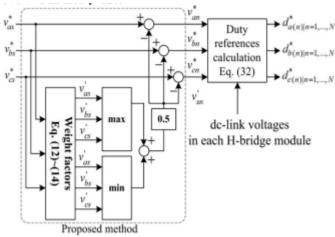

Fig.1. Implementation of the NVM method.

In order to resolve this issue and to synthesize the output voltage to V 1 phmax in the linear modulation range, the NVM technique is proposed in this paper. Fig1 shows the concept of the proposed NVM technique. Here, a neutral voltage between the two neutral points n and s in Fig. 1 is modulated to compensate the output voltage imbalance caused by unbalanced dc-link conditions. To do this, first, the weight constant Kw is defined as

$$K_w = \frac{V_{dc\_mid} + V_{dc\_min}}{2}.$$

(3)

By using (12), the weight factors are calculated as

$$K_{w_{a}} = \frac{K_{w}}{V_{dc_{a}}}$$

$K_{w_{a}} = \frac{K_{w}}{V_{dc_{a}}}$   $K_{w_{a}c} = \frac{K_{w}}{V_{dc_{a}c}}$  (4)

Where, Kw\_a ,Kw\_b, and Kw\_c represent the weight factors for phases a, b, and c, respectively. Next, the weight factors areTo

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

reduce the common-mode voltage, a multilevel SVPWM has been proposed. The series SVPWM method has been reported to easily implement SVPWM for the MLCI. An SVPWM is proposed for hybrid inverters consisting of neutral point clamp and H-bridge inverters to improve output voltage quality and efficiency. As with two-level inverters, it is also possible to implement carrier-based SVPWMs which are equivalent to traditional SVPWMs by injecting a common offset voltage to the threephase references. Some methods to calculate the offset voltages to achieve the optimal space vector switching sequence are addressed. The performances of a carrier-based PWM and an SVPWM are compared, and a PWM scheme is proposed to obtain an optimal output voltage in the multilevel inverter. On the other hand, MLCIs require separated dc links. Therefore, if there is one or more faults present in the dc links in each phase, or if the voltage magnitudes of the dc links are unequal, the output voltage of the MLCI can be unbalanced without proper compensation. To resolve this issue, some studies have been conducted. It is shown that the available modulation index is reduced under faulty conditions switch modules in on multilevel inverters. compensation and algorithms are proposed for phasedisposition PWM and phase-shifted (PS) PWM cases. For a

STATCOM application, a zero sequence voltage to decouple a three-phase MLCI into three single-phase MLCIs is applied as well as zero average active power techniques to operate the MLCI under unbalanced source or load conditions. Reference explains why the optimum angles and modulation indexes are necessary to obtain maximum balanced load voltages in the MLCI undergoing a fault on switching modules. A neutral voltage shifting technique has been introduced for balancing the state of charge in the MLCI-based battery energy storage system. A duty cycle modification method has been proposed to compensate an output voltage imbalance caused by single-phase power fluctuations. Reference has shown that a zero sequence component helps to obtain the maximum balanced output voltages in a fault condition. An offset voltage injection technique is studied to balance the output voltage of the MLCI, but the use of an integrator in the compensation method may reduce dynamic characteristics in applications such as EV motor drives. Recently, the multilevel multiphase feed forward space vector modulation technique called MFFSVM is proposed to compensate the voltage imbalances in MLCIs. In this paper, a carrier-based PWM strategy to balance line to line output voltages and to maximize the linear modulation range where the output voltage can

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

be linearly controlled in the MLCI operating under unbalanced dc-link conditions is proposed. In unbalanced dc-link conditions, the maximum synthesizable voltage in each phase is not uniform. Consequently, the linear modulation range is reduced, and a significant output voltage imbalance may occur as output voltage references increase. In order to analyze the imbalance effect, the voltage vector space for the MLCI is evaluated in detail. From this analysis, the theory behind the output voltage imbalance explained, and the maximum is linear modulation range considering unbalanced dc sources is evaluated. After that, a neutral voltage modulation (NVM) strategy is proposed to achieve output voltage balancing as well as to extend the linear modulation range up to the maximum reachable point in theory. In the proposed method, the neutral voltage reference, which considers a zero sequence voltage to compensate the output voltage imbalance, and an offset voltage to extend the linear modulation range are easily obtained through simple arithmetic calculations. In the proposed method, too large of a dc-link imbalance precludes the output voltages from being balanced. This limitation is also discussed. In addition, a faulttolerant operation is naturally covered, because the MLCI undergoing an unbalanced dc-link condition can be considered as an MLCI

operating under a faulty condition on switch modules. Compared to the existing methods, the proposed strategy is very simple to implement, compensates the output voltage imbalance in real time, and maximizes the voltage utilization of thedc links. Therefore, if this scheme is applied to applications such as EV traction drive systems, the dynamic characteristics can be greatly improved.

**CONCLUSION** The NVM technique for MLCIs under unbalanced dc-link conditions has been in this paper. In order to analyze the maximum synthesizable voltage of MLCIs, the voltage vector space has been analyzed using the switching function. From the analysis, the maximum linear modulation range was derived. The NVM technique is applied to achieve the maximum modulation index in the linear modulation range under an unbalanced dc-link condition as well as to balance the output phase voltages. Compared to the previous methods, the proposed technique is easily implemented and improves the output voltage quality under unbalanced dc-link conditions. Both simulations and experimental results based on the IPM motor drive application verify the effectiveness of the method.

## REFERENCES

[1] J. Rodriguez, J.-S. Lai, and F. Z. Peng, —Multilevel inverters: A survey of topologies, controls, and applications, IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002. [2] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, —Medium-voltage multilevel converters—State of the art, challenges, and requirements in industrial applications, IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2581– 2596, Aug. 2010. CHO et al.: CARRIER-BASED NVM STRATEGY FOR MLCIS UNDER UNBALANCED DC SOURCES 635

[3] J.-S. Lai and F. Z. Peng, —Multilevel converters—A new breed ofpower converters, IEEE Trans. Ind. Appl., vol. 32, no. 3, pp. 509–517, [4] M. May/Jun. 1996.

[4] Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, —A surveyon cascaded multilevel inverters, IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

[5] J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. León, R. C. Portillo, M. A. M. Prats, and M. A. Perez, —Multilevel converters: An enabling technology for high-power applications, Proc. IEEE, vol. 97, no. 11, pp. 1786–1817, Nov. 2009.

[6] G. Bergna, E. Berne, P. Egrot, P. Lefranc,A. Arzande, J.-C. Vannier, and M. Molinas,—An energy-based controller for HVDC

modular multilevel converter in decoupled double synchronous reference frame for voltage oscillation reduction, IEEE Trans. Ind. Electron., vol. 60, no. 6,pp. 2360–2371, Jun. 2013.

[7] Z. Shu, N. Ding, J. Chen, H. Zhu, and X. He, —Multilevel SVPWM with DC-link capacitor voltage balancing control for diode-clamped multilevel converter based STATCOM, IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1884– 1896, May 2011.

[8] J. Chavarria, D. Biel, F. Guinjoan, C. Meza, and J. J. Negroni, —Energybalance control of PV cascaded multilevel grid-connected inverters under level-shifted and phase-shifted PWMs, IEEE Trans. Ind. Electron., vol. 60, no. 1, pp. 98–111, Jan. 2013.

[9] G. Buticchi, E. Lorenzani, and G. Franceschini, —A five-level single-phase grid-connected converter for renewable distributed systems, IEEE Trans. Ind. Electron., vol. 60, no. 3, pp. 906–918, Mar. 2013.

[10] J. A. Munoz, J. R R. Espinoza, C. R. Baier,

L. L. Morán, E. E. Espinosa, P. E. Melín, and D.

G. Sbárbaro, —Design of a discrete-time linear control strategy for a multicell UPQC, IEEE

Trans. Ind. Electron., vol. 59,no. 10, pp. 3797–3807, Oct. 2012.