# R UIR

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

# An Efficient Of Graphbased Solution For Transitor Network Generation

K.Mounika & T. Sathyanarayana

M.Tech Scholor Cmr Engineering College, Rangareddy, T.S, India. Associate Professor, Cmr Engineering College, Rangareddy, T.S, India.

mounikakola12@gmail.com & Satyant234@gmail.com

#### ABSTRACT

Transistor organize streamlining is of unique enthusiasm for effective advanced circuit outline. In this unique circumstance, a diagram based answer for double system age is proposed. The calculation can create arrangement parallel and scaffold topologies. This project proposes a novel technique to naturally create systems with insignificant transistor check, beginning irredundant total of-items articulation as the info. The technique can convey both seriesparallel (SP) and non-SP switch courses of action, enhancing speed, control dispersal, and zone of CMOS doors. This proposed design depicted an effective diagram based technique to create advanced transistor (switch) systems. The proposed design of this project will be intended to actualized and furthermore investigation the yield current, vield voltage, region utilizing Dsch31 and miniaturized scale wind.

#### 1. Introduction

Large-scale incorporation (VLSI) is the way toward making a coordinated circle (United States Intelligence Community) by consolidating a huge number of transistors into a solitary chip. VLSI started in the seventies when complex semiconductor and correspondence advancements were being created. The microchip is a VLSI gadget. Prior to the presentation of VLSI designing science

most Intelligence Community had a constrained band of capacities they could perform. An electronic visit may comprise of a C.P.U., Read-just memory, Random-get to memory and other paste rationale. VLSI lets IC originators ADHD these into one chip.

A die of VLSI integrated circuit

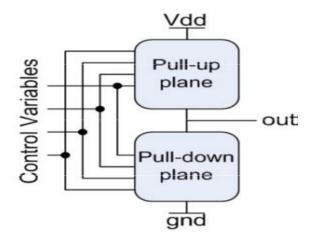

CMOS configuration is at present the most utilized and settled rationale style connected cutting edge industry by the microelectronics. This standard, otherwise called reciprocal arrangement/parallel (named here as CSP) rationale style, is a game plan of arrangement and parallel transistors in two rationale planes: isolated pull-up pulldown ones. Fig. 1 shows the CSP rationale style. The real favorable position of the CSP rationale is low affectability to commotion, great execution and low power utilization [1].

A similar procedure is improved the situation parallel interconnections, bringing about arrangement courses of action. Recalling that the CMOS style gives a refute rationale work.

#### International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

IN VLSI advanced outline, the flag defer proliferation, control dissemination, and range of circuits are firmly identified with the quantity of transistors (switches). Consequently, transistor course of action improvement is of uncommon intrigue when outlining standard cell libraries and custom doors.

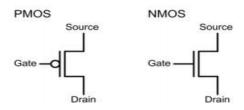

innovation, they are spoken to by the NMOS transistor (coordinate switch) and the PMOS transistor (corresponding switch). Figure outlines the emblematic documentation of these components, and Figure exhibits some rationale systems speaking to self-assertive rationale work.

Standard CMOS logic style ('CSP')

#### **Rationale Switches:**

A few distinct techniques have been proposed actualizing switch systems. subsequent systems may exhibit diverse properties, which are not portrayed extensively in the writing. The essential component to execute systems is the switch. This component can be called as immediate switch, when it leads by applying a '1' rationale esteem in its control terminal, or correlative switch, when it directs by applying a '0' rationale esteem in its control terminal. these components, By forming conceivable to assemble courses of action. known as rationale systems, to permit the interconnection between two unique terminals as per a given rationale work that this system speaks to. Depending of the innovation utilized, these switches can be actualized as physical gadgets. In the right now CMOS

PMOS and NMOS transistors.

Arbitrary logic functions.

# 2. Literature Survey:

The proposition of standard-cell configuration is to diminish the usage exertion by reusing a library of cells. The benefit of this approach is that the cells just should be planned and confirmed once for a given innovation, and they can be reused commonly, consequently amortizing the outline cost. The inconvenience is that the obliged idea of the library, particularly because of the set number of cells, lessens the likelihood of tweaking the plan (RABAEY, 2005). As per Scott (1994),

## **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

the nature of an orchestrated plan in light of standard-cells relies upon three primary parts: (a) the union instrument, the place and course devices, and (c) the objective cell library. Picking the correct cell library may significantly affect the attributes of a circuit (VUJKOVIC, 2002; SECHEN, 2003). Cell library is a limited arrangement of rationale cells that executes distinctive Boolean capacities with various drive qualities and topologies.

Generally, the innovation mapping strategies depend on static preportrayed libraries pointing postponement, zone and power enhancements. Every cell in the library is completely portrayed through numerous reproductions, bringing about an arrangement of exact data about the conduct of the phone. As indicated by Sechen (2003), the plan and portrayal expenses of a library are costly. In this manner, business libraries are normally made out of couple of hundred combinational cells and successive components (locks and flip-flops) for which designs have been enhanced for a specific innovation. Therefore, fashioners are confined to utilize these cells in their circuits. A case of an outstanding and broadly utilized scholastic library is exhibited in Appendix A. Innovation mapping is the system of communicating a given Boolean system as far as rationale cells or entryways. Regularly, the target work points the ideal utilization of all doors in the library to execute a circuit with basic way defer not as much as an objective esteem and least zone.

# 3. Switch Network Synthesis Method

# 3.1 Proposed Technique:

Switch based innovations, for example, CMOS, FinFET [6], and carbon nanotubes [7], can exploit such a change. In this manner,

productive calculations to naturally create enhanced transistor systems are very valuable for planning advanced coordinated circuits (ICs). A few techniques have been introduced in the writing for creating and improving transistor systems. Most customary arrangements depend on calculating Boolean articulations, in which just series—parallel (SP) relationship of transistors can be acquired from figured structures [8]- [11]. Then again, chart based strategies can discover SP furthermore non-SP (NSP) courses of action with potential lessening in transistor tally [12]-[15]. Notwithstanding the endeavors of past works, there is as yet a space for enhancing the age of transistor systems.

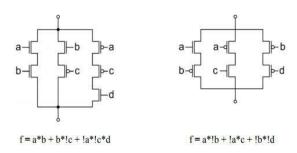

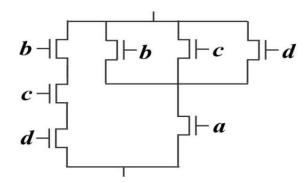

Fig: SP solution from factored form

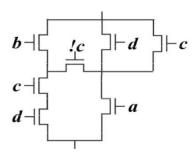

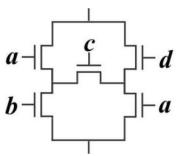

For example, consider a given capacity spoke to by the accompanying condition:  $F = a \cdot b + a \cdot c + a \cdot d + b \cdot c \cdot d$ . (1) For this capacity, factorization strategies can convey the SP arrange appeared in Fig. 1(a), containing seven transistors. Existing diagram based strategies, thusly, can give the NSP arrangement appeared in Fig. 1(b), likewise with seven transistors. Be that as it may, the ideal game plan made out of just five transistors, as appeared in Fig. 1(c), isn't found by any of these techniques [8] – [15].

### International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

Fig: NSP from existing graph-based generation methods

Fig: Optimum NSP solution

In this work, the objective is to deliver a smaller transistor organize for a given capacity. superior Boolean For comprehension of the proposed strategies, some transient definitions are introduced in the accompanying. An exacting is a variable of a Boolean capacity f or its supplement, e.g. c or!c, while a 3D shape is a result of literals. An irredundant whole of-item (ISOP) is an entirety of-item (SOP) where either an exacting or 3D square can't be evacuated without changing the capacity of Boolean articulation. An arrangement parallel system (SP) is where the transistors are in either arrangement or in parallel plans. It can likewise contain both arrangement and parallel courses of action joined. A nonarrangement parallel system (NSP) is where the transistors have a scaffold association amongst arrangement and parallel game plans.

To streamline the talks in the accompanying segments just the Pull Down system is considered. The consolidating of transistors upgrades the transistor includes decrease rationale entryways along these lines lessening the power dissemination. Thus, the transistor combining is connected to the non-basic circuit ways.

The contribution of the strategy is a Spice net list depiction. This portrayal is converted into a multigraph portrayal with a specific end goal to be controlled. The calculation to produce the double diagram is performed in three fundamental advances: pressure, double chart age, and decompression.

Pressure In the pressure step, every one of different edges joining a similar two vertices (parallel edges) are converged in single edges. Similarly, the edges interfacing vertices with 2-degree (arrangement edges) are converged in single edges.

Notice this consolidation operation causes the concealment of the 2-degree vertex. This system is just permitted if the vertex isn't an extraordinary vertex (Vdd/Gnd and Output). It is done until the point when no edge compressions are watched. This progression is done to rearrange the grouping of the calculation. On the off chance that the first transistor organizes is an arrangement/parallel execution this pressure will bring about a diagram with just a single edge. It implies that it isn't important to utilize the following stage to get the double execution, since the arrangement is minor (as displayed some time arrangement/parallel through affiliation). On the off chance that the quantity of edges from the subsequent compacted diagram is not the same as one, it means the

## **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

first transistor arrange is a nonseries parallel usage the proposed strategy includes two principle modules:

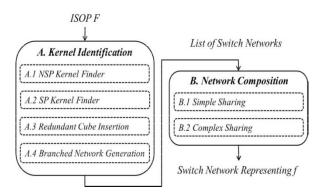

- 1) Kernel Identification and

- 2) Switch system arrangement.

The previous gets an ISOP F and recognizes individual NSP and SP switch systems, speaking to sub elements of f. The last forms those systems into a solitary system by performing rationale sharing. They gave yield is an enhanced switch organize speaking to the objective capacity f. The execution stream of the technique is displayed in Fig. 3.

#### Algorithm

# Algorithm 1 Pseudocode of the Kernel Identification Module

- 1: kernelIdentification (F)

- 2: S ← Ø

- 3:  $S \leftarrow S \cup NSPKernelFinder(F)$

- 4:  $F_1 \leftarrow \text{removeImplementedCubes}(F, S)$

- 5:  $S \leftarrow S \cup SPKernelFinder(F_1)$

- 6:  $F_2 \leftarrow \text{removeImplementedCubes}(F_I, S)$

- 7:  $S \leftarrow S \cup \text{redundantCubeInsertion}(F_2)$

- 8:  $F_3 \leftarrow \text{removeImplementedCubes}(F_2, S)$

- 9:  $S \leftarrow S \cup \text{branchedNetworkGeneration}(F_3)$

- 11: return S

- 12: end

#### 3.2 Kernel Identification:

Amid the piece distinguishing proof module, a middle of the road information structure called bit is utilized to scan for conceivable SP and NSP systems.  $\in$  A bit of an ISOP F with m 3D shapes is an undirected diagram G = (V, E), where vertices in  $V = \{v1, v2, ..., vm\}$  speak to particular 3D squares of F. An edge  $e = (vi, vj) E, I_=j$ , exists if and jus he portion structure, it is conceivable to decide the relationship among shapes of F so t if  $vi \cap vj = 0$ . Such edge e = 0 is marked  $vi \cap vj = 0$ . Utilizing t

as to perform rationale sharing. Along these lines, each progression of the portion recognizable proof module means to extricate pieces from F that prompts upgraded switch check. The part recognizable proof module is separated in four stages, as exhibited in Fig. 3 (left) and in Algorithm 1. Each progression is in charge of discovering switch systems speaking to sub function the objective capacity f.

**Execution flow of the proposed method**

# 4. Software Description

The MICROWIND programming enables the creator to reproduce and plan an incorporated circuit at physical portrayal level. Microwind3 binds together schematic passage, design based test system, SPICE extraction of schematic, Verilog extractor, format arrangement, on design blend flag circuit reenactment, cross sectional and 3D watcher, net rundown extraction, BSIM4 instructional exercise on MOS gadgets and close down relationship to convey unmatched outline execution and fashioner profitability. The bundle contains a library of normal rationale and simple ICs to see and reproduce. Microwind3 incorporates every one of the summons for a veil editorial manager and additionally, you can access Circuit Simulation by squeezing only one single key.

### International Journal of Research

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

The electric extraction of your circuit is consequently performed and the simple test system produces voltage and current bends immediately.

The instrument includes full altering offices, different perspectives, and an on-line simple test system. The microwind programming has following sections in it. The Microwind software allows the designer to simulate and design an integrated circuit at physical description level. Microwind3 unifies schematic entry, pattern based simulator, SPICE extraction of schematic, Verilog extractor, layout compilation, on layout mixsignal circuit simulation, cross sectional & 3D viewer, netlist extraction, BSIM4 tutorial on MOS devices and sign-off correlation to deliver unmatched design performance and designer productivity.

#### **DSCH Software:**

The most popular version of this product among our users is 2.7. The name of the program executable file is Dsch2. The present document introduces the design simulation of CMOS integrated circuits, in an attractive way thanks to user-friendly PC tools DSCH and MICROWIND. The lite version of these tools only includes a subset of available commands. The lite version is freeware, available on the web site. Program is a logic editor and simulator.DSCH is used to validate the architecture of the logic circuit before the microelectronics design is started.DSCH provides a user-friendly environment for hierarchical logic design, and fast simulation with delay analysis, which allows the design and validation of complex logic structures. DSCH also features the symbols, models and assembly support for 8051 and18f64 microcontrollers. DSCH also includes an interface to Win SPICE.

# 5. Result Analysis

**Series-Parallel Super Gate Simulation**

Above outline appears, super gate plan of Boolean condition ( $a \cdot b + a \cdot c + a \cdot d + b \cdot c \cdot d$ ). Chart is planned in DSCH 3.5 form and blended in micro wind 3.5 renditions. Initial 6 transistors are in on positions, seventh one is in off position Non-Series Parallel Super Gate Simulation Above diagram shows, super gate design of Boolean equation ( $a \cdot b + a \cdot c + a \cdot d + b \cdot cd$ ). Diagram is designed in DSCH 3.5 version and synthesized in microwind3.5 version. First p-mos transistors is in off positions, ningth one is in off position, while remaining all are in on positions.

#### LAYOUTS:

Voltage v/s Time

Above recreation chart appears, super gate outline of Boolean condition (a • b + a • c + a• d + b • c • d). Outline is planned in DSCH 3.5

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

form and blended in microwind3.5 rendition. a, b, c, d factors are considered as data sources, out1,out2,out3,out4 can be taken as yields and staying all are halfway outcomes.

# 6. Applications and Future Enhancement

## **Applications**

- 1) IC Designing

- 2) Military Applications

- 3) Bio-Medical Applications

- 4) Tele Communications

#### **Future Enhancement:**

Be that as it may, the value of the technique isn't completely acknowledged a direct result probabilistic the way reenactment approximates spatial connections of signs within the sight of deferrals. As an improvement, we utilize super gate allotments (encasing reconvergent fanouts) coordinated Boolean capacities (TBF) to acquire the double change probabilities that effectively manage glitches and sifting as they influence control estimation. Upgraded comes about on ISCAS'85 benchmarks may indicate noteworthy enhancements in estimation precision as the normal estimation mistake on add up to control utilization stays under 5%. Most existing probabilistic methodologies of dynamic power estimation expect a zero-defer model and disregard the transient flag advances, in particular, glitches or risks.

In this technique, it has been stretched out to incorporate genuine postpones in order to consider glitch control. Progress thickness approach included glitch control expecting that no two signs travel all the while. Probabilistic recreation (CREST) and labeled probabilistic reenactment (TPS) utilize likelihood waveforms to factually display the

flag action that likewise incorporates the glitch action. A noteworthy shortcoming in these methodologies is that in spite of the fact that glitches are viewed as, the glitch separating impact is occasionally considered, which alludes to the way that glitches with heartbeat width not as much as the entryway inertial deferral will be "sifted" out by the door. Glitch sifting impact can change the hub action drastically and has critical effect on the power estimation. As of late, another measure of double change likelihood was proposed, prompting a more precise glitch separating labeled probabilistic strategy in the reenactment (TPS). In any case, it was additionally demonstrated that the value of the strategy completely new was not acknowledged because of the constraint of the hidden probabilistic reenactment procedures.

#### Conclusion

It is realized that the lessening in transistor tally enhances the circuit execution and zone of advanced circuits. This project exhibited a chart based way to deal with produce advanced transistor systems. As showed through test comes about, the proposed technique gave noteworthy lessening in transistor tally to accomplish reduced systems. At the point when the correct factorization is obscure or can't be effectively discovered, the proposed diagram based approach has a tendency to give preferred outcomes over the current related procedures. The proposed strategy brings about a lessening of transistor tally when contrasted with past methodologies and ready to convey connect systems.

This project portrayed an effective chart based strategy to create streamlined transistor (switch) systems. Our approach produces more broad courses of action than the typical SP affiliations. Trial comes about showed a

# **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

significant decrease in the quantity of transistor expected to actualize rationale systems, when contrasted and the ones produced by existing related methodologies. It is realized that the transistor include minimization CMOS doors may enhance the execution, control dispersal, and zone of computerized ICs. In a general perspective, the proposed strategy produces proficient switch courses of action very valuable to be investigated by various IC advancements in view of switch hypothesis.

#### **References:**

- [1] Y.- T. Lai, Y.- C. Jiang, and H.- M. Chu, —BDD deterioration for blended CMOS/PTL rationale circuit synthesis, in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), vol. 6. May 2005, pp. 5649–5652.

- [2] H. Al-Hertani, D. Al-Khalili, and C. Rozon, —Accurate add up to static spillage current estimation in transistor stacks, in Proc. IEEE Int. Conf. Comput. Syst. Appl., Mar. 2006, pp. 262–265.

- [3] T. J. Thorp, G. S. Yee, and C. M. Sechen, —Design and union of dynamic circuits, IEEE Trans. Large Scale Integr. (VLSI) Syst., vol. 11, no. 1, pp. 141–149, Feb. 2003.

- [4] A. I. Reis and O. C. Andersen, —Library sizing, U.S. Patent 8 015 517, Jun. 5, 2009.

- [5] R. Roy, D. Bhattacharya, and V. Boppana, —Transistor-level enhancement of advanced outlines with flex cells, Computer, vol. 38, no. 2, pp. 53–61, Feb. 2005.

- [6] M. Rostami and K. Mohanram, —Dual-vth free entryway FinFETs for low power rationale circuits, IEEE Trans. Comput.- Aided Design Integr. Circuits Syst., vol. 30, no. 3, pp. 337–349, Mar. 2011.

- [7] M. H. Ben-Jamaa, K. Mohanram, and G. De Micheli, —An proficient entryway library for ambipolar CNTFET logic, IEEE Trans. Comput.- Aided Design Integr. Circuits Syst., vol. 30, no. 2, pp. 242–255, Feb. 2011.

- [8] M. C. Golumbic, A. Mintz, and U. Rotics, —An change on the intricacy of figuring readonce Boolean functions, Discrete Appl. Math., vol. 156, no. 10, pp. 1633–1636, May 2008.

- [9] E. M. Sentovich et al., —SIS: A framework for successive circuit synthesis, Dept. Choose. Eng. Comput. Sci., Univ. California, Berkeley, Berkeley, CA, USA, Tech. Rep.UCB/ERL M92/41, May 1992.