#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

### A Framework for Applying Same Filter to Different Signal Processing System

S Divva & G Santosha

- 1.Pg Scholar, Department of ECE, Vaagdevi College of Engineering, Bollikunta Warangal, Telangana

- 2. Assistant Professor, Department of ECE, Vaagdevi College of Engineering, Bollikunta Warangal, Telangana

#### **ABSTRACT:**

The primary challenge is the fact individual's codes should minimize the delay and area penalty. One of the codes which have been considered for memory protection is Reed-Solomon (RS) codes. This limits using ECCs in high-speed recollections. It has brought to using simple codes for example single error correction double error recognition (SEC-DED) codes. However, as technology scales multiple cell upsets (MCUs) be common and limit using SEC-DED codes unless of course they're coupled with interleaving. To prevent data corruption, error correction codes (ECCs) are broadly accustomed to safeguard recollections. ECCs introduce a delay penalty in being able to access the information as encoding or deciphering needs to be carried out. An identical issue happens in some kinds of recollections like DRAM which are typically arranged in modules made up of several products. In individual's modules, the security against a tool failure instead of isolated bit errors can also be desirable. In individual's

cases, one option is by using more complex ECCs that may correct multiple bit errors. These codes derive from non-binary symbols and for that reason can correct multiple bit errors. Within this paper, single symbol error correction codes according to Reed-Solomon codes that may be implemented with low delay are suggested and evaluated. The outcomes show that they'll be implemented having a substantially lower delay than traditional single error correction RS codes.

Keywords: Error correction codes, reedsolomon codes, DRAM memory module, soft errors.

#### I. INTRODUCTION

ECCs then adds additional parity check bits to every memory word so that errors could be detected and remedied. These extra bits lessen the effective capacity from the memory. Errors could be caused for instance by radiation caused soft errors affecting a number of memory cells

# R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

and alter their values. Data corruption brought on by errors is really a serious problem in recollections other kinds of failures cause permanent damage so that the unit no more provides correct data. To make sure that information is not corrupted when failures occur, error correction codes (ECCs) are broadly utilized in recollections. Other overheads created by the ECC would be the encoding and deciphering circuitry. This circuitry comes with an impact also around the delay because the data needs to be encoded when writing in to the memory and decoded when studying from this. When multiple errors affect cells which are physically close, out of the box the situation of radiation caused multiple cell upsets (MCUs), SEC-DED codes could be coupled with interleaving to make sure that the errors affect only one bit per logical word. Generally, the deciphering is much more complex compared to encoding and limits the rate from the ECC. Typically single error correction double error recognition (SEC-DED) codes are utilized to safeguard recollections. These codes possess a minimum Hamming distance of 4 so that single bit errors could be remedied while double errors are detected and never miscorrected. SEC-DED codes could be implemented having a relatively low area and delay overhead and a few optimizations happen to be suggested recently.

Multiple bit errors are a problem when SEC-DED codes are utilized. That's even the situation when a mistake causes the malfunction of the device inside a memory module. For the reason that situation, the term is split in sub-blocks as well as an ECC can be used for all of them [1]. Then your sub-blocks are interleaved within the products so that inside a device there's only one small given sub-block. However, using interleaving comes with an effect on the memory design and may increase area and power. For any memory module, using interleaving increases the amount of parity check bits needed, to supplement bits are needed per each one of the sub-blocks. Finally, when multiple errors come from independent error occasions, more effective ECCs are necessary to make sure the correction of errors. A large quantity of multiple bit ECCs happen to be suggested safeguard recollections. Included in this are Bose-Euclidean Chaudhuri-Hocquenghem (BCH), Geometry, Difference Set, Orthogonal Latin Reed-Solomon codes. Squares and Solomon (RS) codes possess a distinct feature when in comparison using the other codes: they aren't binary. They will use symbols from the Galois Field so that each symbol is symbolized by multiple bits. Therefore a SEC RS code can correct multiple bit errors as lengthy because they affect just one symbol. This is extremely

# R UR

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

attractive for memory modules as when the amount of bits within the products match's individuals from the symbols within the RS code, failures in a single device could be remedied. Actually, because of this RS codes are generally accustomed to safeguard primary recollections in personal computers for space programs, for example individuals described [2]. Generally, the information that forms an RS code word is thought as polynomial coefficients with values of the Galois Field. The polynomial akin to a code word is really a multiple of the specific polynomial, known as generator polynomial g(x). Interested visitors can make reference to a textbook on error control codes for more particulars. Within the situation of SEC RS codes, the code word consists by appending two check symbols to some data word of k symbols. To define the SEC RS codes, normally the matrix representation is preferred, thus the symbols creating the code word are vectors of Galois Field elements. For binary codes, a code is determined utilizing a matrix H, known as parity check matrix. A code word is really a vector v. The encoding procedure for an information vector d is carried out beginning from the generator matrix G, by computing Gd, which helps to ensure that Hv. Because the SEC RS code is generally separable, the G matrix assumes the shape G, where Ik is really an

identity matrix and P is of dimension k x 2. Just like other advanced ECCs one problem for using RS codes in recollections may be the delay created by the deciphering. Within the situation of RS codes, several arithmetic procedures within the Galois Field are necessary to encode or decode a block. This produces a much bigger delay compared to traditional SEC-DED codes. To mitigate the outcome on delay when utilizing advanced ECCs, one choice is to do error recognition first and just when errors are detected go to the correction phase. As errors are rare, the typical delay will bond with those of the mistake free situation that is given when needed to do error recognition only. This really is reduced compared to time required for correction. However, despite this modification delay could be large because the error recognition here we are at RS codes could be significant. Within this paper, modifications to traditional RS codes to lessen the mistake recognition delay are presented. This reduction would effectively lessen the delay to gain access to the information once the pointed out plan of carrying out error recognition first and proceeding to another phases of deciphering only should there be errors can be used. The suggested schemes will also be implemented and in comparison with traditional RS codes [3]. The outcomes reveal that

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

significant reductions in delay could be accomplished using the suggested modifications.

#### II. EXISTED METHODOLOGY

Reed Solomon codes really are a subclass of non-binary BCH codes built with symbols from the Galois Field. An RS code has got the following parameters: maximum block length n q x 1, quantity of parity check symbols n x k 2. All individuals parameters are expressed when it comes to q-ary symbols. When t 1, the minimum distance is three and then the code can correct single symbol errors. These errors can impact multiple bits as lengthy as these fit in with exactly the same symbol. RS codes are generally expressed as RS(n, k, m). The syndrome vector may be used to identify errors the delay and complexity of syndrome computation is dependent around the values from the parity check matrix. However, there's a common extension from the SEC RS code In conclusion, the deciphering of SEC RS codes requires numerous complex procedures over GF(q) specifically for error correction where division and logarithm have to be implemented. Syndrome computation requires only multiplications and additions and it is delay is dependent around the values of each one of the rows within the H matrix.

| Code                               | Data bits | Parity Check Bits | GF(q)   |

|------------------------------------|-----------|-------------------|---------|

| SEC-RS(10,8,8)                     | 64        | 16                | 28      |

| SEC-RS <sub>mod1</sub> (10,8,8)    | 64        | 16                | 28      |

| 2xSEC-RS(10,8,4)                   | 64        | 16                | 24      |

| 2xSEC-RS <sub>mod1</sub> (10,8,4)  | 64        | 16                | 24      |

| SEC-RS(18,16,8)                    | 128       | 16                | 28      |

| SEC-RS <sub>mod1</sub> (18,16,8)   | 128       | 16                | $2^{8}$ |

| 2xSEC-RS <sub>mod2</sub> (19,16,4) | 128       | 24                | $2^{4}$ |

TABLE 1 Parameters of the Codes Evaluated

#### III. PROPOSED SYSTEM

Within this section, two modified SEC RS codes are given to lessen the delay for encoding as well for error recognition. The very first modification attempts to optimize the parity check matrix to lessen the delay for encoding and syndrome computation [4]. The 2nd combines the very first by having an extension of using RS codes for any given something of q to allow longer block measures. This cuts down on the encoding and deciphering delay further because the multiplications along with other arithmetic procedures are carried out on the simpler Galois Field. For any SEC-RS code, the computation from the parity check matrix is unbalanced. The multiplication from the first row from the matrix for any block r requires no multiplications around the Galois Field as the second requires n x 1 multiplications around the Galois Field. The very first suggested modification to RS codes attempts to balance the complexness of both

### R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

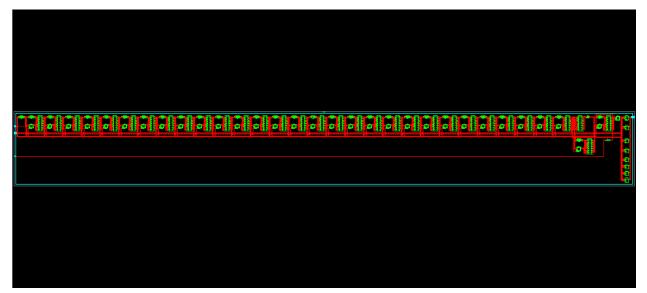

computations. With this particular modifications the computation of each one of the check symbols throughout the encoding process, as well as the syndrome symbols throughout the deciphering process, necessitates the same quantity of multiplications. This reduces the critical path and for that reason lowers the delay. The deciphering for that suggested codes is comparable to those of SEC RS codes. Component that impacts the delay of RS encoders and decoders is how big the Galois Field which is used to create the code. It's because the rise from the complexity from the arithmetic procedures for bigger Galois Fields. With this particular modification, the block length can depend on symbols. The extra row enables to be criminated between syndrome vectors that otherwise could have a similar syndrome value [5]. The deciphering takes again some evaluations, a division along with a logarithm. The suggested codes happen to be validated using random errors to make sure that all single symbol errors are remedied. The encoder and decoder akin to the above mentioned presented codes continues to be developed in VHDL and synthesized, and also the answers are presented the suggested modified RS codes are evaluated and in comparison with existing RS codes. To judge the delay and part of the different codes, these were implemented in Highdensity lipoprotein and synthesized for any 45 nm library.

#### **RESULTS:**

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

|                       |          |                  |              |              |              |              | 2,000,000 ps |

|-----------------------|----------|------------------|--------------|--------------|--------------|--------------|--------------|

| Name                  | Value    | 1,999,995 ps     | 1,999,996 ps | 1,999,997 ps | 1,999,998 ps | 1,999,999 ps | 2,000,000 ps |

| ▶ 🦝 mem12[7:0]        | 00000000 |                  |              | 00000000     |              |              |              |

| mem13[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem14[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem15[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem16[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem17[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem18[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem19[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem20[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| ▶ 🚮 mem21[7:0]        | 00000000 |                  |              | 00000000     |              |              |              |

| ▶ <b>I</b> mem22[7:0] | 00000000 |                  |              | 00000000     |              |              |              |

| ▶ 🐻 mem23[7:0]        | 00000000 |                  |              | 00000000     |              |              |              |

| ▶ 🐻 mem24[7:0]        | 00000000 |                  |              | 00000000     |              |              |              |

|                       |          | X1: 2,000,000 ps |              |              |              |              |              |

| mem25[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem26[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem27[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| mem28[7:0]            | 00000000 |                  |              | 00000000     |              |              |              |

| ▶ 🚮 mem29[7:0]        | 00000000 |                  |              | 00000000     |              |              |              |

| ▶ 🌃 mem30[7:0]        | 00000000 |                  |              | 00000000     |              |              |              |

|                       | 00000000 |                  |              | 00000000     |              |              |              |

| ▶ 🐻 mem31[7:0]        |          |                  |              | 11010101     |              |              |              |

#### IV. CONCLUSION

The good examples employed for evaluation match real designs generally utilized in memory modules. For individuals, the suggested codes enable significant delay reductions in encoding and deciphering delay. The codes happen to be implemented and evaluated. Within this paper, new codes according to modifications of single error correction Reed Solomon (SEC RS) codes happen to be suggested with the aim of reducing delay. This will make the modified codes attractive for top-speed recollections. Future work will think about the look at the suggested

codes to safeguard other kinds of memory like for good examples caches.

#### REFERENCES

[1] C. Wilkerson, A. R. Alameldeen, Z. Chishti, W. Wu, D. Somasekhar, and S. Lu, "Reducing cache power with low cost, multi-bit error-correcting codes," in Proc. 37th Annu. Int. Symp. Comput. Archit., Jun. 2010, pp. 83–93.

[2] G. C. Cardarilli, M. Ottavi, S. Pontarelli, M. Re, and A. Salsano, "Fault tolerant solid state mass memory for space applications," IEEE

## R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

Trans. Aerosp. Electron. Syst., vol. 41, no. 4, pp. 1353–1372, Oct. 2005.

[3] S. Liu, P. Reviriego, and J. A. Maestro, "Efficient majority logic fault detection with difference-set codes for memory applications," IEEE Trans. Very Large Scale Integr. Syst., vol. 20, no. 1, pp. 148–156, Jan. 2012.

[4] E. Ibe, H. Taniguchi, Y. Yahagi, K. Shimbo, and T. Toba, "Impact of scaling on neutron-induced soft error in SRAMs from a 250 nm to a 22 nm design rule," IEEE Trans. Electron. Devices, vol. 57, no. 7, pp. 1527–1538, Jul. 2010.

[5] S. Lin and D. J. Costello, Error Control Coding, 2nd ed. Englewood Cliffs, NJ, USA: Prentice-Hall, 2004.