# R UJR

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

### **Introduction to Reversible Logic Gates & Its Application**

#### 1. R.SRAVYA,2. MR.G.BABU

- 1.Pg Scholar, Department of ECE, Vaagdevi College of Engineering, Bollikunta Warangal, Telangana

- 2. Assosciate Professor, Department of ECE, Vaagdevi College of Engineering, Bollikunta Warangal, Telangana

ABSTRACT In current scenario, the reversible logic design attracting more interest due to its low power consumption. Reversible logic is very important in low-power circuit design. The important reversible gates used for reversible logic synthesis are Feynman Gate, Fredkin gate, toffoli gate, New Gate sayem gate and peres gate etc. This paper present a basic reversible gate to build more complicated circuits which can be implemented in ALU, some sequential circuits as well as in some combinational circuits. It also gives brief idea to build adder circuits using the basic reversible gate like peres gate and TSG gate. Keywords Low-power VLSI, Low-power CMOS design, reversible logic, quantum cost, reversible counters

1. INTRODUCTION Reversible logic has received great attention in the recent years due to their ability to reduce the power dissipation which is the main requirement in low power VLSI design. It has wide applications in low power CMOS and Optical information processing, computing, quantum computation hardware nanotechnology. Irreversible computation results in energy dissipation due to information loss. According to Landauer's research, the amount of energy dissipated for every irreversible operation is at least KTln2 joules, where

K=1.3806505\*10-23m 2 kg-2K -1 (joule/Kelvin-1) is the Boltzmann's constant and T is the temperature at which operation is performed [1]. The heat generated due to the loss of one bit of information is very small temperature but when the number of bits is more as in the case of high speed computational works the heat dissipated by them will be so large that it affects the performance and results in the reduction of lifetime of the components In 1973, Bennett showed that KTln2 energy would not dissipate from a system as long as the

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

system allows the reproduction of the inputs from observed outputs [2]. Reversible logic supports the process of running the system both forward and backward. This means that reversible computations can generate inputs from outputs and can stop and go back to any point in the computation history. A circuit is said to be reversible if the input vector can be uniquely recovered from the output vector and there is a one-to-one correspondence between its input and output assignments, i.e. not only the outputs can be uniquely determined from the inputs, but also the inputs can be recovered from the outputs Energy dissipation can be reduced or even eliminated if computation becomes Information-lossless

THE CONCEPT Reversibility in computing implies that no information about the computational states can ever be lost, so we can recover any earlier stage by computing backwards or un-computing the results. This is termed logical reversibility. The benefits of logical reversibility can be gained only after employing physical reversibility. Physical reversibility is a process that dissipates no energy to heat. Absolutely perfect physical reversibility is practically unachievable. Computing systems give off heat when voltage levels change from positive to negative: bits from zero to one. Most of the energy needed to make that change is given off in the form of heat. Rather than changing voltages to new levels, reversible circuit elements will gradually move charge from one node to the next. This way, one can only expect to lose a minute amount of energy on each transition. Reversible computing strongly affects digital logic designs. Reversible logic elements are needed to recover the state of inputs from the outputs. It will impact instruction sets and high-level programming languages as well. Eventually, these will also have to be reversible to provide optimal efficiency.

3. **MOTIVATION BEHIND REVERSIBLE LOGIC** High-performance chips releasing large amounts of heat impose practical limitation on how far can we improve the performance of the system. Reversible circuits that conserve information, by uncomputing bits instead of throwing them away, will soon offer the only physically possible way to keep improving performance. Reversible computing will also lead to improvement in energy efficiency. Energy efficiency will

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

fundamentally affect the speed of circuits such as nanocircuits and therefore the speed of most computing applications. To increase the portability of devices again reversible computing is required. It will let circuit element sizes to reduce to atomic size limits and hence devices will become more portable. Although the hardware design costs incurred in near future may be high but the power cost and performance being more dominant than logic hardware cost in today's computing era, the need of reversible computing cannot be ignored

### 4. REVERSIBLE LOGIC GATES A reversible logic gate is an n-input n-output logic device with one-to-one mapping. This helps to determine the outputs from the inputs and also the inputs can be uniquely recovered from the outputs. Also in the synthesis of reversible circuits direct fan-Out is not allowed as one-to-many concept is not reversible. However fan-out in reversible achieved circuits is additional gates. A reversible circuit should be designed using minimum number of reversible logic gates. From the point of view of reversible circuit design, there are many parameters for determining complexity and performance of circuits.

- The number of Reversible gates (N): The number of reversible gates used in circuit.

- The number of constant inputs (CI): This refers to the number of inputs that are to be maintained constant at either 0 or 1 in order to synthesize the given logical function.

- The number of garbage outputs (GO): This refers to the number of unused outputs present in a reversible logic circuit. One cannot avoid the garbage outputs as these are very essential to achieve reversibility.

- Quantum cost (QC): This refers to the cost of the circuit in terms of the cost of a primitive gate. It is calculated knowing the number of primitive reversible logic gates (1\*1 or 2\*2) required to realize the circuit.

#### 5.LITERATURE REVIEW

Energy loss is a vital thought in digital circuit style. a district of this downside arises from the technological non quality of switches and materials. the opposite a part of the matter arises from Landauer's principle that there's no resolution. Landauer's Principle [3] states that logical computations that don't seem to be reversible essentially generate k\*T\*ln(2) joules of warmth energy, wherever k is that the constant k=1.38xlO-

## R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

23 J/K, T is that the temperature at which the computation is performed. though this quantity of warmth seems to be little, Moore's Law predicts exponential growth of warmth generated attributable to data lost, which is able to be a clear quantity of warmth loss in next decade. Also by second law of natural philosophy any method that's reversible won't amendment its entropy. On thermo highoctane grounds, the erasure of 1 little bit of data from the mechanical degrees of system should be amid thermalization of associate degree quantity of k\*T\*ln (2) joules of energy. the knowledge entropy H is calculated for any chance distribution. equally the natural philosophy entropy S refers to natural philosophy possibilities specifically. so gain in entropy forever suggests that loss of knowledge, and zilch a lot of. Design that doesn't lead to data loss is termed reversible. It naturally takes care of warmth generated attributable to data loss. Bennett [4] showed that zero energy dissipation would be attainable given that the network consists of reversible logic gates, so changeableness can become a vital property in future circuit style technologies.

**6.REVERSIBLE LOGIC**

Reversible logic may be a promising computing style paradigm that presents a way for constructing computers that manufacture chilling. Reversible no computing emerged as a results of the applying of quantum physics principles towards the event of a universal computer. the basics of reversible Specifically, computing are supported the link between entropy, heat transfer between molecules during a system, the chance of a quantum particle occupying a specific state at any given time, and also the quantum field theory between electrons once they are in dose proximity. the essential principle of reversible computing is that a bijective device with an even range of input and output lines can manufacture a computing surroundings wherever the electrodynamics of the system allow prediction of all future states supported illustrious past states, and also the system reaches each attainable state, leading to no chilling A reversible computer circuit is associate degree N-input Noutput logic device that has one to 1 mapping between the input and also the output. It not solely helps USA to see the outputs from the inputs however additionally helps USA to unambiguously recover the inputs from the outputs. Garbage outputs are those that don't

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

contribute to the reversible logic realization of the look. Quantum solid refers to the value of the circuit in terms of the value of a primitive gate. Gate count is that the range of reversible gates wont to understand the operate. Gate level refers to the amount of levels that are needed to understand the given logic functions. The following are the necessary style constraints for reversible logic circuits.

- 1. Reversible logic gates don't permit fanouts.

- 2. Reversible logic circuits ought to have minimum quantum price.

- 3. the look is optimized thus on manufacture minimum range of garbage outputs.

- 4. The reversible logic circuits should use minimum range of constant inputs.

- 5. The reversible logic circuits should use a minimum logic depth gate levels.

The basic reversible logic gates encountered throughout the look are listed below:

NOT Gate

The simplest Reversible gate is NOT gate and is a 1\*1 gate. The Reversible 1\*1 gate is NOT Gate with zero Quantum Cost is as shown in the Figure 1.

Figure 1. NOT gate

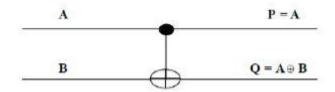

#### 2.2 Feynman / CNOT Gate

Controlled NOT (CNOT) gate is an example for a 2\*2 gate. The Reversible 2\*2 gate with Quantum Cost of one having mapping input (A, B) to output (P = A, Q = A B) is as shown in the Figure 2.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

Figure 2. Feynman/CNOT gate

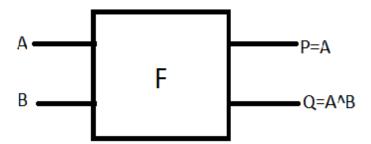

There are many 3\*3 Reversible gates such as F, TG, PG and TR gate.

#### **REVERSIBLE GATES**

There are many reversible gates such as Feynman, Toffoli, TSG, Fredkin, Peres, etc [3]. As the universal gates in boolean logic are Nand and Nor, for reversible logic, the universal gates are Feynman and Toffoli gates.

**Feynman Gate**: Feynman gate is a universal gate which is used for signal copying purposes or to obtain the complement of the input signal. The block diagram of Feynman gate is shown in fig.1

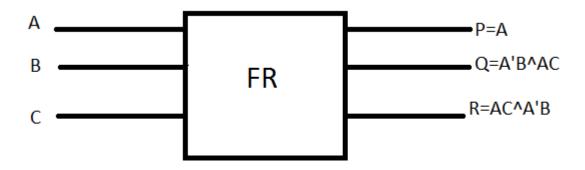

**Fredkin Gate**: It is a basic reversible 3- bit gate used for swapping last two bits depending on the control bit. The control bit here is A, depending on the value of A, bits B and C are selected at outputs Q and R. When A=0, (Q=B, R=C) whereas when A=1, (Q=C, R=B). Its block diagram is as shown in fig. 2:

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

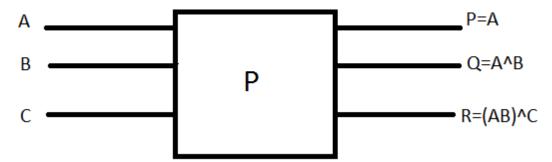

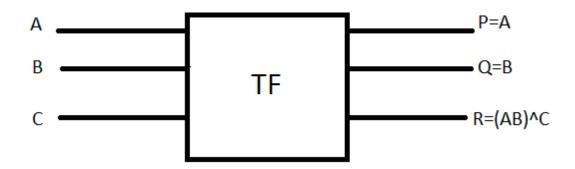

**Peres Gate**: It is a basic reversible gate which has 3- inputs and 3-outputs having inputs (A, B, C) and the mapped outputs (P=A, Q=A^B, R=(A.B)^C). The block diagram is as shown in fig. 3:

**Toffoli Gate**: Toffoli gate is a universal reversible gate which has three inputs (A, B, C) mapped to three outputs  $(P=A, Q=B, R=(A.B)^C)$ . The block diagram of Toffoli gate is shown in fig. 4:

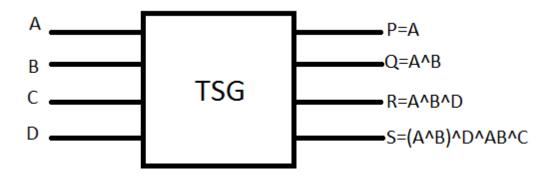

**TSG Gate**: TSG gate is a reversible gate which has four inputs (A, B, C, D) mapped to four outputs (P=A, Q=A^B, R=A^B^D, S=(A^B)^D^AB^C). The block diagram of TSG Gate is shown in fig. 5:

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

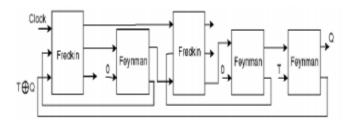

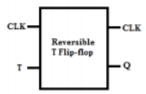

**Reversible Positive Edge Triggered T-Flip Flop** This section includes the construction of Master-Slave T FlipFlop using reversible gates. The truth table is shown in the Table 6. The design is shown in the Figure 11 [8]. The added Feynman gate as shown in figure to get the desired functionality of Q-1.

Figure 11: Reversible positive edge triggered T flip-flop

| CLK | T | $\mathbf{Q}_{t-1}$ | Q |

|-----|---|--------------------|---|

| 0   | 0 | 0                  | 0 |

| 1   | 0 | 0                  | 0 |

| 0   | 0 | 1                  | 1 |

| 1   | 0 | 1                  | 1 |

| 0   | 1 | 0                  | 0 |

| 1   | 1 | 0                  | 1 |

| 0   | 1 | 1                  | 1 |

| 1   | 1 | 1                  | 0 |

Table 6: positive edge triggered T flip-flop

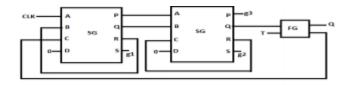

This construction is done can be done by replacing fredkin and Feynman gate by single sayem gate The reversible realization of T Flip-flop has two SG gates and one Feynman Gate is shown in fig 12[5].

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

Fig 12: Reversible Positive Edge Triggered T Flip-flop

Figure 13: reversible T flip flop

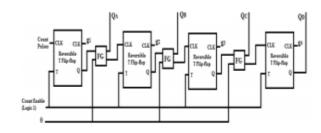

**PROPOSED 4-BIT ASYNCHRONOUS UP/DOWN COUNTER:** The reversible design of the asynchronous Up/Down Counter is shown in Fig. 14. The Up/Down operation of this reversible design is controlled by the control input UP/DOWN. When this control input is 1 the reversible design operates as an Up counter. When this control input is 0 the reversible design operates as a Down Counter

Fig 14: Proposed 4-bit Reversible Asynchronous down Counter

APPLICATIONS Reversible computing may have applications in computer security and transaction processing, but the main long-term benefit will be felt very well in those areas which require high energy efficiency, speed and performance .it include the area like 1. Low power CMOS.

2. Quantum computer. 3. Nanotechnology 4.

Optical computing 5. Design of low power arithmetic and data path for digital signal processing (DSP). 6. Field Programmable Gate Arrays (FPGAs) in CMOS technology for extremely low power, high testability and self-repair 7. **CONCLUSION** We have presented an approach to the realize the multipurpose binary reversible gates. Such

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

gates can be used in regular circuits realizing Boolean functions. In the same way it is possible to construct multiple-valued reversible gates having similar properties. The proposed asynchronous designs have the applications in digital circuits like a Timer/Counter, building reversible ALU, reversible processor etc. This work forms an important move in building large and complex reversible sequential circuits.

#### **REFERENCES**

- [1] Landauer, R., "Irreversibility and heat generation in the computing process", IBM J. Research and Development, 5(3): pp. 183-191, 1961.

- [2] Bennett, C.H., "Logical reversibility of Computation", IBM J.Research and Development, 17: pp. 525-532, 1973.

- [3] Thapliyal H, M. B.Sshrinivas." A New Reversible TSG Gate and Its Application for Designing Efficient Adder Circuits". Centre for VLSI and Embedded System Technologies International Institute of Information Technology, Hyderabad, 500019. India

- [4] Thapliyal H, M. B.Sshrinivas "Novel Reversible Multiplier Architecture Using Reversible TSG Gate" Computer Systems and Applications, 2006. IEEE International Conference on.

- [5] H.r.bhagyalakshmi, M.k.venkatesha," an improved design of a multiplier using reversible Logic gates" International Journal of Engineering Science and Technology Vol. 2(8), 2010, 3838-3845

- [6] Rangaraju H G, Venugopal U, Muralidhara K N, Raja K B "Low Power Reversible Parallel Binary Adder/Subtractor" International journal of VLSI design & Communication Systems (VLSICS) Vol.1, No.3, September 2010

- [7] Thapliyal H, Ranganathan N.," Design of Reversible Latches Optimized for Quantum Cost, Delay and Garbage Outputs" Centre for VLSI and Embedded System Technologies International Institute of Information Technology, Hyderabad, 500019, India.

- [8] V.Rajmohan, V.Ranganathan,"Design of counter using reversible logic" 978-1-4244-8679-3/11/\$26.00 ©2011 IEEE.

## R UR

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

[9] Abu Sadat md. Sayem, masashi ueda," Optimization of reversible sequential circuits" Journal of computing, Vol. 2, No. 6, June 2010, NY, USA, ISSN 2151-9617.

[10] Siva Kumar Sastry, Hari Shyam Shroff ,Sk.Noor Mahammad, V. Kamakoti" Efficient Building Blocks for Reversible Sequential Circuit Design" 1-4244-0173-9/06/\$20.00©2006IEEE.