# R BURR

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

## Fast and Energy-Efficient Carry Skip Adder working under a extensive series of Supply Voltage Levels

Nagalaxmi Bairapangu & Dr. S. K. Sinha

<sup>1</sup>Asst. Professor Department Of ECE<sup>2</sup>Professor Department Of ECE

Kommuri Pratap Reddy Institute Of Technology (KPRIT), Telangana, Hyderabad, India

nagalaxmibaira@gmail.com

**Abstract**: *In this paper, we introduce a carry skip* adder (CSKA) structure that has a higher speed yet bring down energy utilization contrasted and the tradition alone. The speed upgrade is accomplished by applying connection incrimination plans to enhance the proficiency of the customary CSKA (Conv-CSKA) structure. Likewise, rather than using multiplexer rationale, the proposed structure makes utilization of AND-OR-Invert (AOI) or potentially AND-Invert (OAI) compound doors for the skip rationale. The structure might be acknowledged with both settled stage size and variable stage measure styles, where in the last further enhances the speed and energy parameters of the adder. At long last, a hybrid variable latency augmentation of the proposed structure, which brings down the power utilization without significantly affecting the speed, is introduced. This expansion uses an adjusted parallel structure for expanding the slack time, and consequently, empowering further voltage diminishment. The proposed structures are surveyed by looking at their speed, power, and energy parameters with those of other addersusinga45-nm static CMOS innovation for a wide range of supply voltages. The outcomes that

are gotten utilizing HSPICE reproductions uncover, all things considered, 44% and 38% changes in the deferral and energy, separately ,contrasted and those of the Conv-CSKA. What's more, the power— defer item was the most minimal among the structures considered in this paper, while its energy— postpone item was practically the same as that of the Kogge— Stone parallel prefix adder with extensively littler territory and power utilization. Reproductions on the proposed hybrid variable latency CSKA uncover decrease in the power utilization contrasted and the most recent works in this field while having a sensibly high speed.

**Keywords**: Carry skip adder (CSKA), energy efficient, high performance, hybrid variable latency adders, voltage scaling.

#### I. INTRODUCTION

There are many chips away at the subject of improving the speed and energy of these units, which have been accounted for in [2]– [9]. Clearly, it is highly alluring to accomplish higher velocities at low-control/energy utilizations,

### R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

which is a test for the creators of universally useful processors. One of the viable strategies to bring down the power utilization of advanced circuits is to decrease the supply voltage because of quadratic reliance of the exchanging energy on the voltage. Also, the sub edge current, which is the principle spillage segment tin OFF gadgets, has an exponential reliance on the supply voltage level through the deplete actuated obstruction bringing down effect[10]. Depending on the measure of the supply voltage decrease, the operation of ON gadgets may live in the super edge, close limit, or sub edge locales. Working in the super edge area gives us bring down postponement and higher exchanging and spillage powers contrasted and the close/sub limit districts. In the sub limit area, the rationale entryway deferral and spillage control show exponential conditions on the supply and edge voltages. Besides, these voltages are (potentially) subject to process and natural varieties in the nano scale innovations. The varieties increment vulnerabilities in the a fore said performance parameters .what's more, the little sub edge current causes an expansive deferral for the circuits operating in the sub edge region[10]. As of late, the close limit locale has been considered as a district that gives a more attractive exchange off point amongst deferral and power dispersal contrasted and that of the sub edge one, since it brings about lower delay contrasted and the sub edge area and essentially brings down exchanging and spillage powers contrasted and the super edge

area. What's more, close edge operation, which utilizes supply voltage levels close to the edge voltage of transistors [11],experiences extensively less the procedure and natural varieties contrasted and the sub edge area. The reliance of the power (and performance) on the supply voltage has been the inspiration for outline of circuits with the element of dynamic voltage and recurrence scaling. In these circuits, to decrease the energy utilization, the framework may change the voltage (and frequency) of the circuit in light of the work stack requirement [12]. For these frameworks, the circuit ought to have the capacity to work under a wide range of supply voltage levels. Obviously, accomplishing higher rates at bring down supply voltages for the computational pieces, with the adder as one the primary parts, could be significant in the plan of high-speed, yet energy efficient, processors. Notwithstanding the handle of the supply voltage, pick between various adder one structures/families for improving force and speed. There are numerous adder families with various postponements, control utilization

#### II RELATED WORK

In this paper, given the alluring highlights of the CSKA structure, we have concentrated on diminishing its postponement by altering its usage in light of the static CMOS rationale. The fixation on the static CMOS begins from the want to have are liably operating circuit under a wide range of supply voltages in highly scaled advances [10]. The proposed change builds the speed

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

significantly while keeping up the low territory and power utilization highlights of the CSKA. Likewise, a modification of the structure, in light of the variable latency method, which thusly brings down the power utilization without extensively affecting the CSKA speed, is additionally exhibited. To the best of our insight, no work focusing on outline of CSKAs operating from the super limit locale down to close edge district and furthermore, the plan of(hybrid) variable latency CSKA structures have been accounted for in the writing. Subsequently, the commitments of this paper can be outlined as takes after.

Proposing a changed CSKA structure by consolidating the link and the incrimination plans to the ordinary CSKA (Conv-CSKA) structure for improving the speed and energy proficiency of the adder. The alteration furnishes us with the capacity to utilize easier carry skip rationales in view of the AOI/OAI compound entryways rather than the multiplexer.

- Providing an outline technique for developing an efficient CSKA structure in view of systematically articulations displayed for the basic way delay.

- 2) Investigating the effect of voltage scaling on the proficiency of the proposed CSKA structure (from the ostensible supply voltage to the close limit voltage).

- 3) Proposing a hybrid variable latency CSKA structure in light of the augmentation of the proposed CSKA, by supplanting a portion of

the center stages in its structure with a PPA, which is altered in this paper?

There is to this paper is sorted out as takes after. Segment II talks about related work on changing the CSKA structure for enhancing the speed and also earlier work that utilization variable latency structures for expanding the effectiveness of adders at low supply voltages. In Section III, the Conv-CSKA with settled stage measure (FSS) and variable stage size(VSS)is clarified, while Section IV portrays the proposed static CSKA structure. The hybrid variable latency CSKA structure is proposed

#### III CARRY SKIP ADDER

Altering CSKAs for Improving Speed. The ordinary structure of the CSKA comprises of stages containing chain of full adders (FAs) (RCA piece) and2:1multiplexer (carry skip rationale). The RCA squares are associated with each other through 2:1 multiplexers, which can be put in to at least one level structures [19]. The CSKA setup (i.e., the quantity of the FAs per arrange) greatly affects the speed of this kind of adder [23]. Numerous techniques have been proposed for finding the ideal number of the FAs [18] – [26]. The strategies introduced in [19] – [24] make utilization of VSSs to limit the deferral of adders in view of a solitary level carry skip rationale. In[25], some techniques to expand the speed of the multilevel CSKAs are proposed. The methods, be that as it may, cause range and power increment

### ®

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

extensively and less consistent format. The outline of a static CMOS CSKA where the phases of the CSKA have a variable sizes was recommended in [18]. In expansion, to bring down the engendering postponement of the adder ,in each stage, the carry look-ahead rationales were used. Once more, in that mind boggling design and in addition expansive power utilization and zone use. What's more, the plan approach, which was presented only for the 32-bit adder, was not general to be connected for structures with various bits lengths.

#### IV. EXPERIMENTAL RESULTS

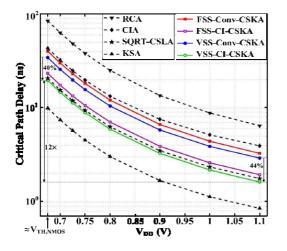

There with those of some different adders. Every one of the adders considered here had the span of 32 bits and were composed and recreated utilizing a 45-nm static CMOS innovation [38]. The

reenactments were performed utilizing HSPICE [40]in the room temperature of 25 °C. The ostensible supply voltage of the innovation was 1.1 V, and the limit voltages of Then MOS and pMOS transistors were 0.677 and 0.622V, separately. It ought to be noticed that, to separate the power utilization of the adders, 10000 uniform arbitrary jolts were infused to them .what's more ,for every adder structure in each supply voltage level, the infusion rate of the boosts was picked in light of the most extreme operating recurrence of the structure. In the accompanying Section VI-An Section VI-B, we initially focus concentrate the adequacy of the genius postured CI-CSKA structure and after that explore the proficiency of the proposed hybrid variable latency structure in light of the CI-CSKA

Fig.8. critical path delay of the adders versus the supply voltage.

#### **V.CONCLUSION**

In the proposed hybrid structure, the prefix system of the Brent– Kung adder [39] issued for developing the core stage (Fig.7). One the benefits

of the this adder contrasted and other prefix adders is that in this structure, utilizing forward ways, the longest carry is ascertained sooner contrasted and the middle of the road conveys,

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

which are processed by back ward ways. Likewise, the fan-out of adder is not as much as other parallel adders, while the length of its wiring is smaller [14]. Finally, it has a straightforward and general design. The inward structure of the stage p, including the adjusted PPA and skip rationale.

#### REFERENCES

- [1] i.koren, computer arithmetic algorithms ,2nded .natick ,ma,usa: akpeters,ltd.,2002.

- [2] r. zlatanovici, s. kao, and b. nikolic, "energy–delay optimization of 64-bit carry-look ahead adders with a240ps 90nm cmos design example, "ieee j. solid-state circuits,vol.44,no.2,pp.569–583, feb.2009.

- [3] mathew. m. a. anders. b. bloechel, t.nguyen, r. k. krishnamurthy, and s. borkar, "a 4-ghz [300-mw 64-bit integer execution alu with dual supply voltages in 90-nm cmos," ieeej.solid-state circuits,vol.40,no.1,pp.44–51,jan.2005.[4] v. g. oklobdzija, b. r. zeydel, h. q. dao, s. mathew, and r.krishnamurthy, "comparison of highperformance vlsi adders in the energy-

- [4] delay space, "ieee trans. very large scale integer.(vlsi) syst.,vol.13,no.6,pp.754–758,jun.2005.

- [5]b.ramkumarand h.m.kittur, "low-power and area-efficient carry select adder ," ieee trans .very large scale integr.(vlsi) syst.,vol.20, no.2,pp.371–375,feb.2012.

- [6] m.vratonjic, b.r.zeydel, and v.g.oklobdzija," low-and ultra low-power arithmetic units :design and comparison ,"in proc

.ieee int .conf.comput .design ,vlsi comput .process. (iccd),oct.2005, pp.249–252.c.nagendra , m.j.irwin, and r.m. owens, "area-time-power trade offs inparallel adders, "ieee trans .circuits syst .ii ,analog digit .signal process.,vol.43,no.10,pp.689–702,oct.1996.

- [7] y.he and c.-h. chang," apower-delay efficient hybrid carry- look ahead/carry-select based redundant binary to two's complement converter,"ieeetrans.circuitssyst.i,reg.papers,vol. 55,no.1, pp.336–346,feb.2008.

- [8] c.-h.chang,j.gu, and m.zhang,"are view of 0.18µm full adder performances for tree structured arithmetic circuits,"ieee trans.very large scale integr.(vlsi)syst.,vol.13,no.6,pp.686–695,jun.2005.

- [9] d.markovic, c.c.wang, l.p.alarcon,t.-t. liu, and j.m.rabaey, "ultra low-power design in near-threshold region," proc .ieee, vol.98, no.2,pp.237–252,feb.2010.