Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue-17 December 2017

# Conversion of Bigleveldsp Circuits Using Obfuscating

<sup>1</sup>Mr. S.Murali Krishna, <sup>2</sup>K.Mamatha & <sup>3</sup>Mr.Kothapalli.Saidulu.

<sup>1</sup>Professor, dept. of ECE, Bomma Institute of Technology and Science, KMM, AP <sup>2</sup>M-Tech, dept. of ECE, Bomma Institute of Technology and Science, KMM, AP <sup>3</sup>HOD, Associate professor, Bomma Institute of Technology and Science, KMM, AP

#### **Abstract**

This paper shows a unique way to cope with configuration muddled circuits for automatic flag making ready (DSP) programs making use of atypical state changes, a key-primarily based jumbling constrained nation system (FSM), and a reconfiguration. The objective is to devise DSP circuits which can be more difficult to discern out. High-level modifications of iterative data flow diagrams had been abused for region speedmanage tradeoffs. This is the primary enterprise to build up an define flow to apply atypical country adjustments that meet these tradeoffs in addition to at the equal time jumble the designs each basically and nearly. A few methods of operations are presented for jumbling wherein the yields are important from a flag dealing with attitude, but are practically inaccurate. Cases of such modes comprise a third-arrange superior channel that can likewise actualize a 6th request or 9th-arrange channel in a period multiplexed manner. The remaining two modes are critical but speak to nearly off base modes. Numerous crucial modes can be misused to reconfigure the channel arrange for diverse packages. Different modes may additionally evaluate to

nonmeaningful modes. A right key contribution to an FSM enacts a reconfiguration. The setup facts control one of a kind methods of the circuit operation. Useful muddling is proficient by way of requiring the use of the proper statement key and lay out facts. Wrong statement key neglects to empower the reconfiguration, and a wrong layout record actuates both a crucial but nonfunctional or nonmeaningful mode. Likelihood of actuating the proper mode is basically decreased prompting a jumbled DSP circuit. Auxiliary confusion is moreover done via the proposed manner by way of odd state adjustments. Exploratory effects reveal that the overhead of the proposed philosophy is little, whilst a solid obscurity is finished. For instance, the location overhead for a (31)the-set up IIR channel benchmark is just 17.7% with a 128piece setup key, where  $1 \le l \le eight$ , i.E., the request of this channel need to be different of three and may change from 3 to 24.

**Key words**: - Digital flag making ready (DSP), sensible jumbling, device safety, atypical kingdom adjustments, licensed innovation (IP)

# **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue-17 December 2017

coverage, muddling, reconfigurable define, fundamental obscurity.

#### INTRODUCTION

Advanced flag handling (DSP) assumes a primary component in various programs, for instance, video pressure, compact frameworks/PCs, sight and sound, wired and far-flung interchanges, discourse preparing, and biomedical managing. Be that as it is able to, as digital devices become regularly interconnected and inescapable in people' lives, security, reliable processing, and safety assurance have risen as imperative difficulties for the subsequent decade. It is classified that as tons as 10% of all reducing area items offered all around are fake which activates a preservationist appraise of\$one hundred billion of income misfortune. Hence, DSP framework architects want to present cautious attention to the security point of view of DSP circuits, since the enemy can without a whole lot of a stretch take inside the usefulness utilizing huge assaulting strategies. The trouble of gadget safety is a genuine fear that has caused a splendid deal of work on device counteractive movement of robbery and certified innovation (IP), which may be substantially grouped into two fundamental instructions: 1) verification primarily based technique and a couple of) muddling based totally method. The validation based methodologies contain bodily unclonable

capacities (PUFs)- based verification, superior watermarking, key-locking plan, and gadget metering. The concentrate of this paper is on confusion, that is a technique that adjustments a utility or a plan into one this is almost equal to the first but is altogether greater hard to figure out. Some equipment guarantee strategies are carried out via converting the human lucidness of the equipment portrayal dialect (HDL) code, or by means of encoding the source code in view of cryptographic systems. As of overdue, various equipment confusion plans have been suggested that trade the limited nation machine (FSM) portrayals to clutter the circuits. Be that as it could, to the quality of our insight, no jumbling based IP safety method has been proposed in particular for DSP circuits inside the writing. This paper, all of a sudden, affords outline of muddled DSP circuits through abnormal state changes which might be harder to parent out. From this point of view of view, a DSP circuit is greater relaxed, at the off threat that it's far tougher for the enemy to find its usefulness irrespective of whether or not the foe can bodily regulate the machine. At the give up of the day, an odd kingdom of security is carried out if the usefulness of a DSP circuit is intended to be escaped the foe.

#### 2.RELEGATED WORK

2.1Existing System

# **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue-17 December 2017

The various modes are produced in light of the selected exchange calculation, that is numerous for distinctive high-level modifications. It is tough to cowl a significant wide variety of existing odd country modifications on this paper. We certainly display a case in this paper to show off how to produce range modes. The proposed plan method can likewise be reached out to other bizarre state changes. Various leveled collapsing technique is a novel collapsing system that joins collapsing of M fell ranges to 1 equipment square and collapsing of N operations inner each place to an equipment useful unit. Two various leveled collapsing calculations are exhibited in, which contain modern interleaved collapsing (HIF) and hierarchical bordering collapsing (HCF). In this paper, we just cope with HCF, while it's far additionally cloth to HIF. The HCF change executes all operations of one region earlier than the beginning execution of operations of a subsequent segment. The peruser is alluded to for moreover subtle factors.

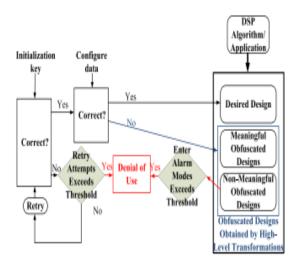

# 2.2Proposed System

The whole arrangement of the proposed jumbled DSP circuit. The reconfiguration may be empowered simply by means of the right statement key. Just the right con-discern information activates the coveted plan. A wrong design statistics initiates a muddled mode (either an important or nonmeaningful). The muddling

FSM and part of nonmeaningful range modes (i.E., we mean as alert modes) can each be used for security check cause. For instance, some undesired modes in Table I may be composed as alert modes by including another yield flag to the combinational cause. We can decorate the safety through mapping a bigger range of layout records to this alert mode, at the same time as preserving the little bit of beneficial arrange records to be generally little. In the event that the circuit consistently receives wrong introduction key or layout records whose quantity surpasses the predefined restriction, the foe is stored from additionally endeavors of the layout key by a refusal of utilization piece.

### 3.IMPLEMENTATION

#### 3.1 Attacks and Countermeasures:

The goal of the proposed approach is to guarantee the creator's IP could now not be stolen towards identifying. As a rule, a programmer endeavoring to decide the usefulness of a DSP circuit can fall lower back on both of the accompanying methods: 1) auxiliary research of the netlist to differentiate and disconnect the first outline from the jumbled plan or 2) simulation based identifying to determine usefulness of the plan. Our proposed jumbling strategy guarantees the device towards the principle form of assault (i.E., auxiliary examination) from two points of view: 1) primary obscurity by ordinary country change

# **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue-17 December 2017

and a pair of) reconciliation with confusion modes. As displayed in Section II, ordinary country changes activate auxiliary muddling at the HDL stage or door degree netlist. Without understanding the right arrangement of the switches, it is difficult for the foe to take in the usefulness of the primary define. Moreover, in spite of the fact that the muddling FSMs will be restricted, the confusion of design

switches cannot be isolated from the primary functionalities. Since the obscurity range modes are coordinated to the reconfigurator in the incorporated DSP circuit, the enemy can't evacuate the plan jumbling carried out via atypical country changes. What's more, significant range modes additionally make uncertainty while the enemy plays out the simple examination assaults.

#### 3.2 Measure of Obfuscation Degree:

Basic Obfuscation Degree: Manual assaults can be carried out with the aid of visible exam and simple investigation. In those types of guide assaults, the enemy wishes to dissect the RTL or door stage shape and further the designs. This is a feeble attack, as the foe has almost no possibility of creating a sense of the muddling plan for expansive DSP circuits. The muddling degree of the auxiliary confusion is reliant on a quantity of free switches (Ns), the time of switch instances after peculiar country changes (P), and the

quantity of institutions for each independent transfer (Cm). To assess the confusion diploma in opposition to these guide attacks, we propose a metric referred to as primary obscurity degree (SOD).

#### **3.3 Improving the Security by Key Encoding:**

In the proposed obscurity conspire, the important thing incorporates of two sections: 1) advent key and a pair of) set up statistics. Be that as it may, inside the situation that the foe has found a key that can effectively bypass the creation, however, remains in an off-base layout, the enemy will simply strive different arrange facts even as settling the statement key. This could debilitate the plan. An encoder could be brought to beautify the safety of the framework. The encoder could be a Hash work, an instantaneous grievance circulate enroll, or a PUF. By joining the encoder, the consumer key and the design key are by no means once more bit-to-bit mapped. Likewise, on the off risk that we make use of a PUF as the encoder, key affects should likewise stay far from in various chips. The PUFs can be applied to provide one in all a typical client keys for numerous DSP circuits in spite of the truth that they're altogether jumbled with a comparable arrangement key.

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue-17 December 2017

Fig 1 Architecture Diagram 4 RESULTS

## 4.1Experimental Results

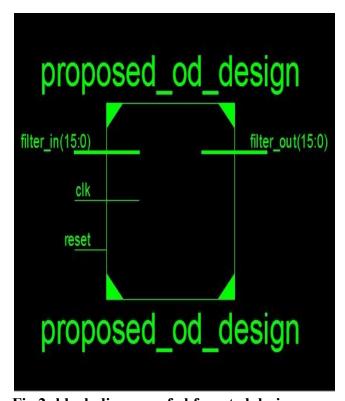

Fig 2: block diagram of obfuscated design.

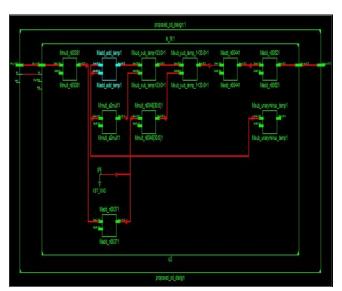

Fig 3: Rtl schematic diagram.

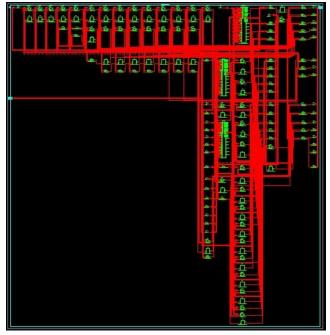

Fig 4:Ttl schematic diagram.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue-17 December 2017

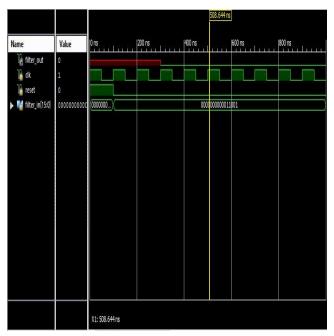

Fig 5:Simulation result.

#### **5.CONCLUSION**

This paper well-known shows a novel lowoverhead answer for define DSP circuits that are muddled each basically and practically by using the use of bizarre kingdom alternate systems. It is established that checking the identicalness of DSP circuits through using ordinary kingdom modifications might be tougher if some switches may be composed such which are difficult to observe. A covered reconfigurable transfer configuration is joined into the proposed configuration plan to decorate the security. A complete define stream is exhibited. In the proposed obscurity method, the range modes and the greater jumbling circuits may want to likewise be composed intentionally in mild of the extraordinary nation modifications. Contrasted

and different present muddling techniques, every other desired standpoint of the proposed method is the age of vital range modes from a flag coping with angle, for the reason that tremendous modes make vagueness to the foe with the stop purpose that it's far difficult for the foe to recognize the right usefulness from other variety modes. The trial comes about have exhibited the adequacy of the proposed philosophy. This paper, instantly, considers the security factor of view of strange kingdom modifications. Future paintings will check out the algorithmic part of diverse atypical for outline kingdom changes muddling. Progressing work incorporates the approval of the security exhibitions of vast modes nonmeaningful modes. We are likewise intrigued by means of tending to the attack strategies for DSP circuits. We imply to abuse the security factor of view of the proposed strategy by acting exceptional assaults to the jumbled DSP circuits. Future paintings may be coordinated towards constructing up a whole outline move that could produce the goal shape and jumbling range modes consequently in light of the particular utility execution necessity. A definitive goal is to build up a digital outline computerization combination apparatus that may consolidate an expansive wide variety of plan obscurity calculations in view of abnormal state changes for DSP framework plan.

### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue-17 December 2017

#### **6.REFERENCE**

[1] J. Guajardo, S. S. Kumar, G.-J.Schrijen, and P. Tuyls, "Brand and IPprotection with physicalunclonable functions," in Proc. IEEE Int. Symp.Circuits Syst., May 2008, pp. 3186–3189.

[2] G. E. Suh and S. Devadas, "Physical unclonable functions for deviceauthentication and secret key generation," in Proc. 44th Annu. DesignAutom. Conf., Jun. 2007, pp. 9–14.

[3] A. L. Oliveira, "Techniques for the creation of digital watermarks insequential circuit designs," IEEE Trans. Comput.-Aided Design Integr.Circuits Syst., vol. 20, no. 9, pp. 1101–1117, Sep. 2001.

[4] D. Kirovski, Y.-Y. Hwang, M. Potkonjak, and J. Cong, "Intellectualproperty protection by watermarking combinational logic synthesis solutions," in Proc. Int. Conf. Comput.-Aided Design, Nov. 1998,pp. 194–198.

[5] A. B. Kahng et al., "Watermarking techniques for intellectual propertyprotection," in Proc. 35th Annu. Design Autom. Conf., Jun. 1998,pp. 776–781.

[6] F. Koushanfar and Y. Alkabani, "Provably secure obfuscation of diversewatermarks for sequential circuits," in Proc. Int. Symp.Hardw.-OrientedSecurity Trust, Jun. 2010, pp. 42–47.

[7] J. A. Roy, F. Koushanfar, and I. L. Markov, "EPIC: Ending piracy ofintegrated circuits," in Proc. Conf. Design, Autom. Test Eur., Mar. 2008,pp. 1069–1074.

[8] W. P. Griffin, A. Raghunathan, and K. Roy, "CLIP: Circuit level ICprotection through direct injection of process variations," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 5, pp. 791–803, May 2012.

[9] Y. M. Alkabani and F. Koushanfar, "Active hardware metering forintellectual property protection and security," in Proc. USENIX SecuritySymp., Aug. 2007, pp. 291–306.

[10] T. Batra. (2005). Methodology for Protection and Licensing of HDL IP[Online]. Available: http://www.design-reuse.com/articles/12745

#### **Authors Profile's**

# MR. S.MURALI KRISHNAM.Tech(Ph.d)

He received B.E Degree in ECE from smania University, INDIA in 1991 M.Tech Degree in Electronics and Communication with specilization of instrumentation and Control systems in 2003 from JNTU Kakinada. He had 23 years of Academic Experience. At present working as professor in ECE department, BITS,

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue-17 December 2017

KMM, AP, INDIA. And pursueingPh.D from JNTUH in the field of Biomedical digital image processing,Email-d:

muralibhatta@gmail.com

#### **K.MAMATHA**

B-Tech in BOMMA Institute Of Technology And Science, Khammam, percentage is 69 %, year of completed APRIL 2014.M.tech[ECE] (Electronics And Communication Engineering), Bomma Institute of Technology and Science (BITS), Khammam, Mail

id:mamatha.kommu87@gmail.com

MR. KOTHAPALLI. SAIDULU

Head of the Department, Associate professor ECE, Bomma Institute of Technology and Science (BITS), Khammam.K.Saidulu received B.Tech degree in Electronics Communication Engineering from NCET, VIJAYAWADA, AP, INDIA IN 2001 and M.Tech In RADAR & Microwave from AUCE, VIZAG in 2006. Worked as Asst. Prof in Sri Kavitha Engineering College in 2004-2008,SRR Engineering College in 2014.Presently, he is working as Asso.Prof& as HOD in BITS,KMM,TS,INDIA.AndpursueingPh.D from JNTUH in the field of Antennas in Bomma Institute of Technology and Science (BITS), Khammam