# R IJR

## **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

## Closed Loop Control of PV fed High Voltage Gain DC-DC converter with Two-Input Boost-Stages

## Gujju Nooratham Reddy & M.V.S Prem Sagar

M.Tech student scholar Department of Electrical & Electronics Engineering BABA Institute of Technology and Sciences Visakhapatnam, A.P, India.

E-mail:gujju.gnr@gmail.com

Assistant Professor Department of Electrical & Electronics Engineering BABA Institute of Technology and Sciences Visakhapatnam, A.P, India.

E-mail:ajay3359@gmail.com

Abstract-DC-DC converter is a device which produces a dc output voltage when a dc input is given. If output voltage needed is higher than input voltage we go for boost converter. The conventional boost converter can be used for step up applications because of low conduction loss, simple structure and low cost. However, it is not suitable for high step-up applications. Generally conventional boost converters have been used to obtain higher output voltage than the input voltage. When these boost converters are operated for high ratios it leads to high voltage and current stress on the switch. Hence an interleaving technique of boost converter has been presented. This method of approach can be used in high power applications to produce high voltage gain when compared to the conventional boost converter. A simple dc-dc boost converter are unable to provide high step-up voltage gains due to the effect of power switches, rectifier diodes, and the equivalent series resistance of inductor and capacitors. In this paper proposes new dc-dc converter to achieve high voltage gain without an extremely high duty ratio. In the proposed converters, two inductors with the same level of inductance are charged in parallel during the switch -on period and are discharged in series during the switch-off period. In this converter mainly proposed converter. That is used for PV system. To achieve high-voltage conversion ratios, a new family of high-voltage-gain dc-dc power electronic converters has been introduced. The proposed converter can be used to draw power from two independent dc sources as a multiport converter or one source in an interleaved manner. They draw continuous input current from both the input sources with low current ripple which is required in many applications, e.g., solar. Several diode-capacitor stages are cascaded together to boost up the voltage which limits the voltage stresses on the switches, diodes, and capacitors.

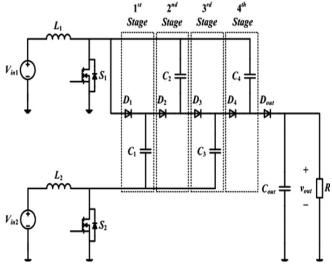

## II. Topology Introduction and Modes of Operation

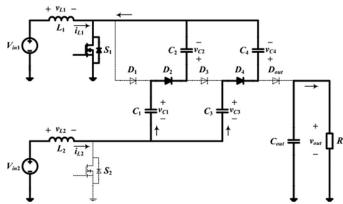

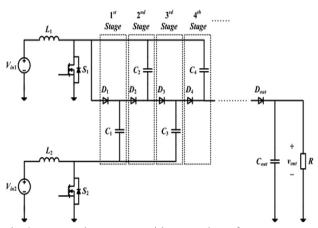

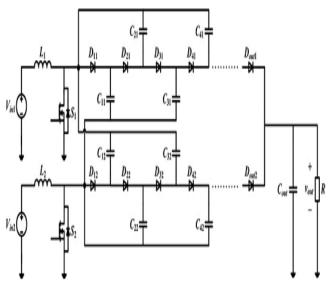

The proposed converter is inspired from a Dickson charge pump [20]. Diode-capacitor VM stages are integrated with two boost stages at the input. The VM stages are used to help the boost stage achieve a higher overall voltage gain. The voltage conversion ratio depends on the number of VM stages and the switch duty ratios of the input boost stages. Fig.1 shows the proposed converter with four VM stages. For simplicity and better understanding, the operation of the converter with four

multiplier stages has been explained here. Similar analysis can be expanded for a converter with N stages.

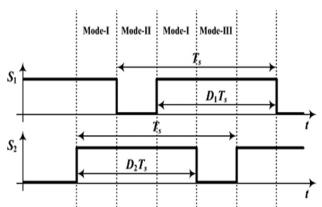

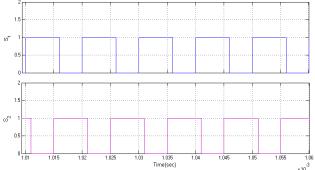

For normal operation of the proposed converter, there should be some overlapping time when both the switches are ON and also one of the switches should be ON at any given time (see Fig.2). Therefore, the converter has three modes of operation. The proposed converter can operate when the switch duty ratios are small and there is no overlap time between the conduction of the switches. However, this mode of operation is not of interest as it leads to smaller voltage gains.

Fig.1. Proposed high-voltage-gain dc-dc converter with four VM stages.

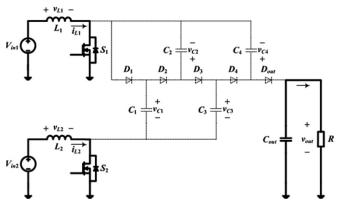

## A. Mode-I

In this mode, both switches S1 and S2 are ON. Both the inductors are charged from their input sources  $Vin_1$  and  $Vin_2$ . The current in both the inductors rise linearly. The diodes in different VM stages are reverse biased and do not conduct. The VM capacitor voltages remain unchanged and the output diode Dout is reverse biased (see Fig.3); thus, the load is supplied by the output capacitor Cout.

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

Fig.2. Switching signals for the input boost stage for the proposed converter.

Fig.3. Mode-I of operation for the proposed converter with four VM stages.

Fig.4. Mode-II of operation for the proposed converter with four VM stages.

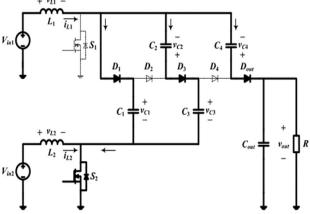

#### B. Mode-II

In this mode, switch S1 is OFF and S2 is ON (see Fig.4). All the odd numbered diodes are forward biased and the inductor current IL1 flows through the VM capacitors charging the odd numbered capacitors (C1,C3,...) and discharging the even numbered capacitors (C2,C4,...). If the number of VM stages is odd, then the

output diode Dout is reverse biased and the load is supplied by the output capacitor. However, if the number of VM stages is even, then the output diode is forward biased charging the output capacitor and supplying the load.

Fig.5. Mode-III of operation for the proposed converter with four VM stages.

In the particular case considered here, since there are four VM stages, the output diode is forward biased.

#### C. Mode-III

In this mode, switch  $S_1$  is ON and S2 is OFF (see Fig.5). Now, the even numbered diodes are forward biased and the inductor current  $IL_2$  flows through the VM capacitors charging the even numbered capacitors and discharging the odd numbered capacitors. If the number of VM stages is odd, then the output diode  $D_{out}$  is forward biased charging the output capacitor and supplying the load. However, if the number of VM stages is even, then the output diode is reverse biased and the load is supplied by the output capacitor.

## III. Voltage Gain of the Converter

The charge is transferred progressively from input to the output by charging the VM stage capacitors. For a converter with four stages of VM (see Fig.1), the voltage gain can be derived from the volt-sec balance of the boost inductors. For L<sub>1</sub>, one can write

$$\langle v_{L1} \rangle = 0 \tag{1}$$

Therefore, from Fig.4, it can be observed that the capacitor voltages can be written in terms of upper boost switching node voltage as

$$V_{C1} = V_{C3} - V_{C2} = V_{\text{out}} - V_{C4} = \frac{V_{\text{in}1}}{(1 - d_1)}$$

(2)

Where d1 is the switching duty cycle for  $S_1$ . Similarly, from the volt-sec balance of the lower leg boost inductor  $L_2$ , one can write the capacitor voltages (see Fig.5) in terms of lower boost switching node voltage as

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

$$V_{C2} - V_{C1} = V_{C4} - V_{C3} = \frac{V_{\text{in}2}}{(1 - d_2)}$$

(3)

Where  $d_2$  is the switching duty cycle for  $S_2$ .

From (2) and (3), the capacitor voltages for the proposed converter with four VM stages can be derived as

$$V_{C1} = \frac{V_{\text{in}1}}{(1 - d_1)} \tag{4}$$

Fig.6. Proposed converter with N number of VM stages.

$$V_{C2} = \frac{V_{\text{in}1}}{(1 - d_1)} + \frac{V_{\text{in}2}}{(1 - d_2)}$$

$$V_{C3} = \frac{2V_{\text{in}1}}{(1 - d_1)} + \frac{V_{\text{in}2}}{(1 - d_2)}$$

$$V_{C4} = \frac{2V_{\text{in}1}}{(1 - d_1)} + \frac{2V_{\text{in}2}}{(1 - d_2)}$$

(5)

The output voltage is derived from (2), which is given by

$$V_{\text{out}} = V_{C4} + \frac{V_{\text{in}1}}{(1 - d_1)} = \frac{3V_{\text{in}1}}{(1 - d_1)} + \frac{2V_{\text{in}2}}{(1 - d_2)}$$

(6)

Similar analysis can be extended to a converter with N number of VM stages (see Fig.6). Thus, the VM stage capacitor voltages are given by

$$V_{Cn} = \left(\frac{n+1}{2}\right) \frac{V_{\text{in}1}}{(1-d_1)} + \left(\frac{n-1}{2}\right) \frac{V_{\text{in}2}}{(1-d_2)}$$

if n is odd & $n \le N$ ,

$$V_{Cn} = \left(\frac{n}{2}\right) \frac{V_{\text{in}1}}{(1-d_1)} + \left(\frac{n}{2}\right) \frac{V_{\text{in}2}}{(1-d_2)}$$

if n is even &  $n \le N$ .

(7)

The output voltage equation of the converter with N number of VM stages depends on whether N is odd or even and is given by

$$V_{\text{out}} = V_{CN} + \frac{V_{\text{in}2}}{(1 - d_2)} \quad \text{if } N \text{ is odd}$$

$$= \left(\frac{N+1}{2}\right) \frac{V_{\text{in}1}}{(1 - d_1)} + \left(\frac{N+1}{2}\right) \frac{V_{\text{in}2}}{(1 - d_2)}$$

(8)

$$V_{

m out} = V_{CN} + rac{V_{

m in}1}{(1-d_1)}_{

m if \, N \, is \, even}$$

$$= \left(\frac{N+2}{2}\right) \frac{V_{\text{in}1}}{(1-d_1)} + \left(\frac{N}{2}\right) \frac{V_{\text{in}2}}{(1-d_2)} \tag{9}$$

When the converter operates in an interleaved manner with single input source, if  $d_1$  and  $d_2$  are also chosen to be identical, i.e.,  $d_1 = d_2 = d$ , then the output voltage is given by

$$V_{\text{out}} = (N+1)\frac{V_{\text{in}}}{(1-d)}$$

(10)

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

Fig.7. Alternative to the proposed converter with N number of VM stages

In [21], an interleaved boost power factor corrected converter with voltage-doubler characteristics is introduced. It can be observed that it is a special case of the proposed converter with a single VM stage (N = 1).

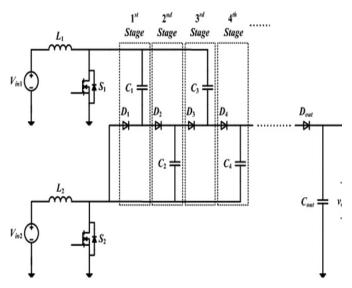

It is worth noting that there is an alternative to the proposed converter (see Fig.7) where diode D1 of the first VM stage is connected to the lower boost switching node and capacitor C1 is connected to the upper boost switching node (compare with Fig.6).

The output voltage equation for this alternative topology is given by

$$V_{\text{out}} = \left(\frac{N+1}{2}\right) \frac{V_{\text{in}1}}{(1-d_1)} + \left(\frac{N+1}{2}\right) \frac{V_{\text{in}2}}{(1-d_2)}$$

if  $N$  is odd (11)

$$V_{\text{out}} = \left(\frac{N}{2}\right) \frac{V_{\text{in}1}}{(1 - d_1)} + \left(\frac{N + 2}{2}\right) \frac{V_{\text{in}2}}{(1 - d_2)}$$

if N is even. (12)

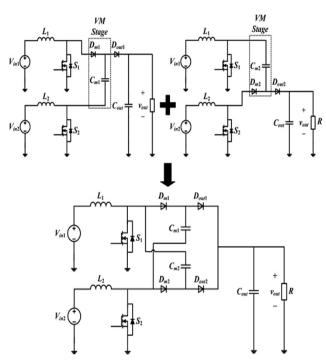

For N = 1, if one combines the topology depicted in Fig.6 with its alternative (see Fig. 7), then the resulting converter in Fig.8 is similar to the multiphase converter introduced in [22].

In general, when both topologies with N number of VM stages are combined, then the resulting converter is shown in Fig.9. When N is odd, then from (3.7) and (3.10), the voltage gain of the combined topology is given by

$$V_{\text{out}} = \left(\frac{N+1}{2}\right) \frac{V_{\text{in}1}}{(1-d_1)} + \left(\frac{N+1}{2}\right) \frac{V_{\text{in}2}}{(1-d_2)}$$

if N is odd. (13)

In this case, the original topology and its alternative each process half of the output power. In other words, the average currents of Dout1 and Dout2 are equal.

When N is even, the output voltage of the combined topology would be either (3.8) or (3.11) and will be dictated by the topology that provides a higher output voltage. Both legs (see Fig.9) would compete with each other and only one of the output diodes (Dout1 and Dout2) would process the entire power while the other will be reverse biased. When N is even, putting the converters in parallel only makes sense if there is only one source used and  $d_1 = d_2$ . In that case both (3.8) and (3.11) determine the output voltage.

Fig.8. Combined topology with single VM stage.

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

Fig.9. Combined topology with N number of VM stages.

$$V_{\text{out}} = (N+1) \frac{V_{\text{in}}}{(1-d)}$$

if  $N$  is even (14)

For the combined topology with a single input source and identical duty ratios d1 and d2, i.e., d1 = d2 = d, both the boost stages will always have symmetrical inductor and switch currents irrespective of the number of VM stages.

## IV. MATLAB/SIMULINK RESULTS:

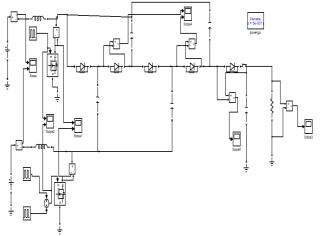

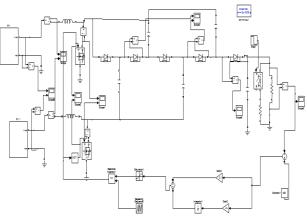

Fig.10. Matlab/simulink Model for Proposed with Two Input Boost Stages

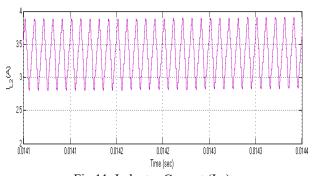

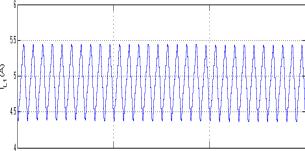

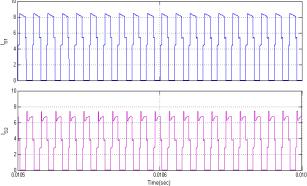

Fig.11. Inductor Current  $(I_{L2})$

Fig.12. Inductor Current (I<sub>L1</sub>)

Fig.13. Switch Gating Pulses S<sub>1</sub>, S<sub>2</sub>

Fig.14. Switching Currents I<sub>S1</sub>, I<sub>S2</sub>

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

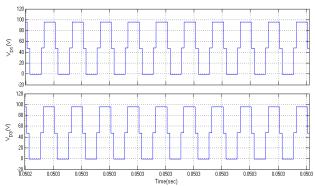

Fig.15. Diode Voltages V<sub>D1</sub>, V<sub>D3</sub>

Fig.16. Diode Voltage V<sub>D4</sub>

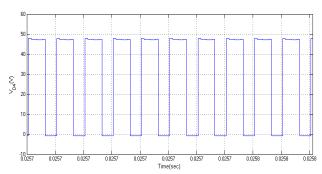

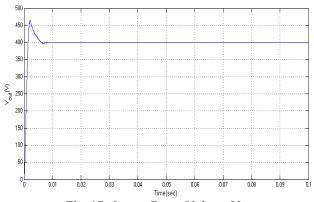

Fig..17. Output Boost Voltage V<sub>0</sub>.

Fig.18. Matlab/simulink Model of Proposed converter with PV Fed Closed loop operation.

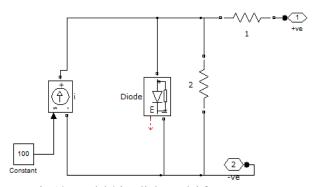

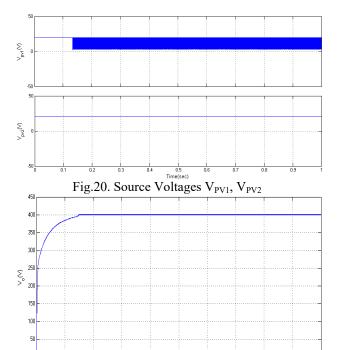

Fig.19. Matlab/simulink Model for PV System.

Fig.21. Output Voltage.

## V. CONCLUSION

In this paper, a family of novel high-voltage-gain dc—dc converters with two boost stages at the input has been proposed. The proposed converter is based on diode—capacitor VM stages and the voltage gain is increased by increasing the number of VM stages. It can draw power from two input sources like a multiport converter or operate in an interleaved manner when connected to a single source. One of the advantages of the proposed converter is that since it is a multiport converter with high voltage gain, it has the flexibility to be connected to independent sources while allowing power

## ₹® ®

## International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

sharing, MPPT algorithms etc., to be implemented independently at each input port. Furthermore, an alternative topology of the proposed converter has been presented and combining them both would result in a new converter topology. The proposed converter can be used for solar applications where each panel can be individually linked to the 400-V dc bus.

### REFERENCES

- [1] S. Jain and V. Agarwal, "A single-stage grid connected inverter topology for solar PV systems with maximum power point tracking," IEEE Trans. Power Electron., vol. 22, no. 5, pp. 1928–1940, Sep. 2007.

- [2] X. Kong and A. M. Khambadkone, "Analysis and implementation of a high efficiency, interleaved current-fed full bridge converter for fuel cell system," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 543–550, Mar. 2007.

- [3] C. Liu and J. S. Lai, "Low frequency current ripple reduction technique with active control in a fuel cell power system with inverter load," IEEE Trans. Power Electron., vol. 22, no. 4, pp. 1429–1436, Jul. 2007.

- [4] E. H. Ismail, M. A. Al-Saffar, A. J. Sabzali, and A. A. Fardoun, "A family of single-switch PWM converters with high step-up conversion ratio," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 4, pp. 1159–1171, May 2008

- [5] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd ed. Norwell, MA, USA: Kluwer, 2001.

- [6] W. Li and X. He, "A family of interleaved DC–DC converters deduced from a basic cell with winding-cross-coupled inductors (WCCIs) for high step-up or step-down conversions," IEEE Trans. Power Electron., vol. 23, no. 4, pp. 1791–1801, Jul. 2008.

- [7] W. Li and X. He, "An interleaved winding-coupled boost converter with passive lossless clamp circuits," IEEE Trans. Power Electron., vol. 22, no. 4, pp. 1499–1507, Jul. 2007.

- [8] W. Li, Y. Zhao, Y. Deng, and X. He, "Interleaved converter with voltage multiplier cell for high step-up and high-efficiency conversion," IEEE Trans. Power Electron., vol. 25, no. 9, pp. 2397–2408, Sep. 2010.

- [9] Y.-P. Hsieh, J.-F. Chen, T.-J. Liang, and L.-S. Yang, "A novel high step-up DC–DC converter for a micro grid system," IEEE Trans. Power Electron., vol. 26, no. 4, pp. 1127–1136, Apr. 2011.

- [10] R. Xie, W. Li, Y. Zhao, J. Zhao, X. He, and F. Cao, "Performance analysis of isolated ZVT interleaved converter with winding-cross-coupled inductors and switched-capacitors," in Proc. IEEE Energy Convers. Congr.Expo., Atlanta, GA, USA, 2010, pp. 2025–2029.

- [11] W. Li, W. Li, X. He, D. Xu, and B. Wu, "General derivation law of non-isolated high-step-up interleaved

converters with built-in transformer," IEEE Trans. Ind. Electron., vol. 59, no. 3, pp. 1650–1661, Mar. 2012.

- [12] K.-C. Tseng, C.-C. Huang, and W.-Y. Shih, "A high step-up converter with a voltage multiplier module for a photovoltaic system," IEEE Trans. Power Electron., vol. 28, no. 6, pp. 3047–3057, Jun. 2013.

- [13] W. Li, Y. Zhao, J. Wu, and X. He, "Interleaved high step-up converter with winding-cross-coupled inductors and voltage multiplier cells," IEEE Trans. Power Electron., vol. 27, no. 1, pp. 133–143, Jan. 2012.