at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07

March 2018

## CODING TECHNIQUES FOR RECYCLING CIRCUITS IN ITS

<sup>1</sup>N USHARANI,<sup>2</sup>S SWATHI

<sup>1</sup>Pg Scholar, Department of ECE, Vaagdevi College of Engineering Bollikunta Warangal, Telangana.

<sup>2</sup>Associate professor, Department of ECE, Vaagdevi College of Engineering, Bollikunta Warangal, Telangana

### **ABSTRACT:**

The DSRC standards generally adopt FM0 and Manchester codes to achieve electricity-balance, improving the signal reliability. This paper not just evolves a completely reused VLSI architecture, but additionally exhibits a competent performance in comparison using the existing works. The devoted short-range communication (DSRC) is definitely an emerging method to push the intelligent transportation system into our daily existence Nonetheless, the codingdiversity between your FMO and Manchester codes seriously limits the possibility to create a completely reused VLSI architecture for. Within this paper, the similarity-oriented logic simplification (SOLS) strategy is suggested to beat this limitation. The SOLS technique increases the hardware utilization rate from 57.14% to 100% for FMO and Manchester encodings. The performance of the paper is evaluated around the post layout simulation in Taiwan Semiconductor Manufacturing Company (TSMC) .18-µm 1P6M CMOS technology. The utmost operation frequency is 2 GHz and 900 MHz for Manchester and FM0 encodings, correspondingly. The ability consumption is 1.58 mW at 2 GHz for Manchester encoding and 1.14 mW at 900 MHz for FM0 encoding. The main circuit area is  $65.98 \times 30.43$  µm2. The encoding capacity of the paper can fully offer the DSRC standards of the use, Europe, and Japan.

Keywords: Dedicated short-range communication (DSRC), FM0, Manchester, VLSI.

#### I. INTRODUCTION

The securities issues include blind-place, intersection warning, inter cars distance, and collisionalarm. The car-to-kerbside concentrates on the intelligent transportation service, for example

## ₹® ®

## International Journal of Research Available

at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

electronic toll collection (ETC) system. The DSRC could be briefly classified into two groups: automobile-to-automobile and automobile-to-kerbside [1]. In automobile-to-automobile, the DSRC allows the content delivering and broadcasting among automobiles for issues of safety and public information announcement. Top of the and bottom parts are devoted for transmission and receiving, correspondingly. This transceiver is classed into three fundamental modules: micro-processor, baseband processing, and RF front-finish. The devoted short-range communication (DSRC) is really a protocol for just one- or two-way medium range communication specifically for intelligent transportation systems [2]. With ETC, the toll collecting is electronically accomplished using the contactless IC-card platform. Furthermore, the ETC could be extended towards the payment for parking-service, and gas-refueling. Thus, the DSRC system plays a huge role in modern automobile industry. The machine architecture of DSRC transceiver. The micro-processor translates instructions from media access control to schedule the duties of baseband processing and RF front-finish. The baseband processing accounts for modulation, error correction, clock synchronization, and encoding. The RF frontend transmits and has got the wireless signal with the antenna. The DSRC standards have been in existence by a number of organizations in numerous nations. These DSRC standards of the use, Europe, and Japan are proven in Table I. The information rate individually targets at 500 kb/s, 4 Mb/s, and 27 Mb/s with carrier frequency of 5.8 and 5.9 GHz. Generally, the waveform of sent signal is envisioned having zero mean for sturdiness issue, which is also known to as electricitybalance. The sent signal includes arbitrary binary sequence that is hard to obtain electricitybalance. The modulation techniques incorporate amplitude shift keying, phase shift keying, and orthogonal frequency division multiplexing. The reasons of FMO and Manchester codes can offer the sent signal with electricity-balance. Both FM0 and Manchester codes are broadly adopted in encoding for downlink. The VLSI architectures of FM0 and Manchester encoders are reviewed.

### II. PREVIOUS WORK

The literature suggested, a VLSI architecture of Manchester encoder for optical communications. This design adopts the CMOS inverter and also the gated inverter because the change to construct Manchester encoder [3]. A higher-speed VLSI architecture almost fully reused with

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

Manchester and Burns encodings for rf identification (RFID) programs. proposes a Manchester encoding architecture for ultrahigh frequency (UHF) RFID tag emulator. This hardware architecture is carried out in the finite condition machine (FSM) of Manchester code, and it is recognized into field-prrr-rrrglable gate array (FPGA) prototyping system. The utmost operation frequency of the design is all about 256 MHz The same design methodology is further put on individually construct FM0 and Burns encoders furthermore UHF RFID Tag emulator. Its maximum operation frequency is all about 192 MHz In addition, combines frequency shift keying (FSK) modulation and demodulation with Manchester codec in hardware realization. However, the coding-diversity between both seriously limits the possibility to create a VLSI architecture that may be fully reused with one another.

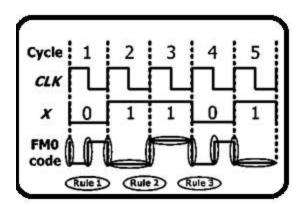

Fig.1. FM0 Coding example

### III. PROPOSED VLSI MODEL

This paper proposes a VLSI architecture design using similarity-oriented logic simplification (SOLS) technique. The SOLS includes two core techniques: area-compact retiming and balance logic-operation discussing [4]. The region-compact retiming relocates the hardware resource to lessen 22 transistors. The total amount logic-operation discussing efficiently combines FM0 and Manchester encodings using the fully reused hardware architecture. With SOL's technique, this paper constructs a completely reused VLSI architecture of Manchester and FM0 encodings for DSRC programs. The experiment results demonstrate that this design accomplishes a competent

# R

## International Journal of Research Available

at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

performance in comparison with sophisticated works. To create an analysis on hardware usage of FM0 and Manchester encoders, the hardware architectures of both of them are carried out first. As pointed out earlier, the hardware architecture of Manchester encoding is simply by a XOR operation. However, the passing of hardware architecture for FM0 isn't as simple as those of Manchester. How to develop the hardware architecture of FMO encoding should begin with the FSM of FM0 first. The coding-diversity between your FM0 and Manchester codes seriously limits the possibility to create a completely reused VLSI architecture. The objective of SOL's strategy is to create a completely reused VLSI architecture for FM0 and Manchester encodings. The SOLS strategy is classified into a double edged sword: area-compact retiming and balance logic-operation discussing. Each part is individually referred to as follows. The component is understood to be the hardware to carry out a specific logic function, for example AND, OR, NOT, and switch-flop. The active components mean the constituents that actually work for FM0 or Manchester encoding. The entire components are the amount of components within the entire hardware architecture regardless of what encoding technique is adopted. The HUR of FMO and Manchester encodings The adoption of FM0 or Manchester code is dependent on Mode and CLR. Additionally, the CLR further has somebody else purpose of a hardware initialization. When the CLR is just derived by inverting Mode without setting a person CLR control signal, this can lead to a conflict between your coding mode selection and also the hardware initialization. To avert this conflict, both Mode and CLR are assumed to become individually allotted for this design from the system controller. Whether FMO or Manchester code is adopted, no logic element of the suggested VLSI architecture is wasted. Every component is active both in FMO and Manchester encodings. Therefore, the HUR from the suggested VLSI architecture is greatly enhanced. The suggested SOLS strategy is developed from architecture perspective to attain 100% HUR. One of the logic families, both static CMOS circuit and transmission gate logic are broadly used in digital circuit because of their superior integration in process manufacturing. Hence, the timing analysis is offered under these 2 kinds of logic families for any more general purpose. To help lessen the transistor count in Manchester encoding path, the transmission-gate logic is recognized as within the circuit designs With SOLS technique, the entire components are reduced from seven lower to 5. Without SOL's technique, the FMO and

## R

## International Journal of Research Available

at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

Manchester encodings are carried out on individual hardware architecture having a poor HUR To normalize the procedure parameters because of different CMOS technologies, the CMOS process scaling from the constant field theorem is used [5]. The SOLS technique eliminates this limitation on HUR by two core techniques: area- compact retiming and balance logic-operation discussing. The region-compact retiming relocates the hardware resource to lessen 22 transistors. The total amount logic-operation discussing efficiently combines FMO and Manchester encodings using the identical logic components.

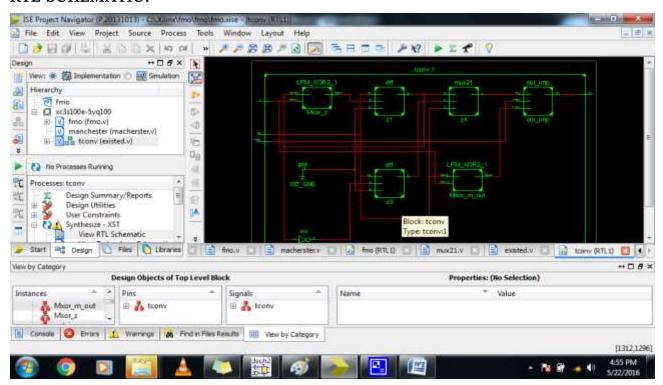

### **RTL SCHEMATIC:**

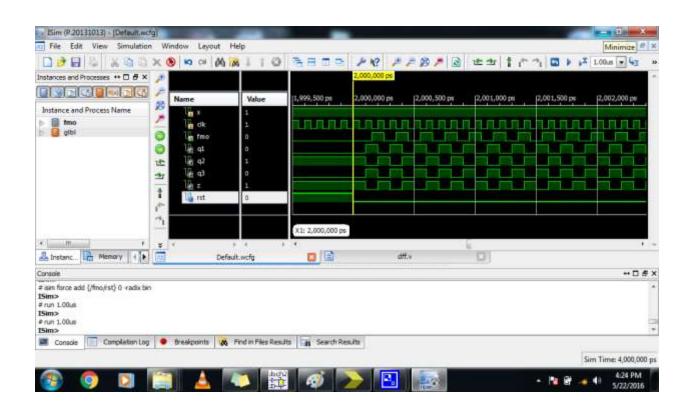

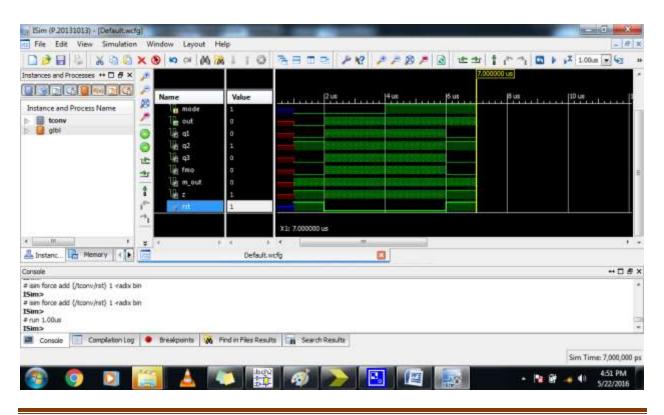

### SIMULATION RESULTS:

at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

## ₹®®

## International Journal of Research Available

at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

#### IV. CONCLUSION

Within this paper, the fully reused VLSI architecture using SOL's way of both FM0 and Manchester encodings is suggested. The ability consumption is 1.58 mW at 2 GHz for Manchester encoding and 1.14 mW at 900 MHz for FM0 encoding. The main circuit area is 65.98 × 30.43 µm<sup>2</sup>. A limitation analysis on hardware usage of FMO and Manchester encodings is talked about at length. The coding-diversity between FM0 and Manchester encodings causes the limitation on hardware usage of VLSI architecture design. The region-compact retiming relocates the hardware resource to lessen 22 transistors. The total amount logic-operation discussing efficiently combines FM0 and Manchester encodings using the identical logic components. This paper is recognized in TSMC .18-um 1P6MCMOS technology by having an outstanding device efficiency. The utmost operation frequency is 2 GHz and 900 MHz for Manchester and FMO encodings, correspondingly. The encoding capacity of the paper can fully offer the DSRC standards of the use, Europe, and Japan. This paper not just evolves a completely reused VLSI architecture, but additionally exhibits an aggressive performance in comparison using the existing works. The SOLS technique increases the HUR from 57.14% to 100%. The SOLS technique eliminates the limitation on hardware utilization by two core techniques: area compact retiming and balance logic-operation discussing.

### **REFERENCES**

[1] H. Zhou and A. Aziz, "Buffer minimization in pass transistor logic," *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.*, vol. 20, no. 5, pp. 693–697, May 2001.

[2] J. Daniel, V. Taliwal, A. Meier, W. Holfelder, and R. Herrtwich, "Design of 5.9 GHz DSRC-based vehicular safety communication," *IEEE Wireless Commun. Mag.*, vol. 13, no. 5, pp. 36–43, Oct. 2006.

at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

[3] M. A. Khan, M. Sharma, and P. R. Brahmanandha, "FSM based FM0 and Miller encoder for UHF RFID tag emulator," in *Proc. IEEE Adv. Comput. Conf.*, Mar. 2009, pp. 1317–1322.

[4] F. Ahmed-Zaid, F. Bai, S. Bai, C. Basnayake, B. Bellur, S. Brovold, *et al.*, "Vehicle safety communications—Applications (VSC-A) final report," U.S. Dept. Trans., Nat. Highway Traffic Safety Admin., Washington, DC, USA, Rep. DOT HS 810 591, Sep. 2011.

[5] Y.-C. Hung, M.-M. Kuo, C.-K. Tung, and S.-H. Shieh, "High-speed CMOS chip design for Manchester and Miller encoder," in *Proc. Intell. Inf. Hiding Multimedia Signal Process.*, Sep. 2009, pp. 538–541.