Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

# POWER EFFICIENT PARALLEL CHIEN SEARCH ARCHITECTURE USING A TWO-STEP APPROACH IN RS CODES

#### G SHIREESHA\* D SRINIVASRAO\*\*

- 1.Pg Scholar, Department of ECE, Vaagdevi College of Engineering, Bollikunta Warangal, Telangana

- .2. Assistant Professor, Department Of ECE, Vaagdevi College of Engineering, Bollikunta Warangal, Telangana

#### **ABSTRACT**

This short proposes a nascent power proficient Chien seek (CS) engineering for parallel Bose-Chaudhuri-Hocquenghem (BCH) codes. For disorder predicated unraveling, the CS assumes a considerable part in discovering blunder areas, thorough calculation brings about cosmically tremendous misuse of strength In the proposed design, utilization. testing procedure is disintegrated into two stages predicated on the paired lattice portrayal. Dissimilar to the initial step got to each cycle, the second step is initiated just when the initial step is prosperous, bringing about striking force safeguarding. Moreover, a productive engineering is exhibited to shun the defer increment in basic ways caused by the two-stage approach. Test comes about demonstrate that the proposed two-stage design for the BCH (8752, 8192, 40) code jelly control utilization by up to half contrasted and the customary engineering. Key words: - **Record Terms**—Bose—Chaudhuri–Hocquenghem (BCH) codes, Chien seek (CS), low intensity, two-stage approach.

#### I INTRODUCTION

Among sundry blunder amendment codes used to instaurate tainted code words in interchanges and capacity frameworks, the Bose-Chaudhuri-Hocquenghem (BCH) code [1], is a standout amongst the most utilized mathematical generally codes because of its intense mistake correction execution and moderate equipment multifaceted design. The paired BCH code has been utilized in various frameworks, for example, propelled strong state stockpiles fiber correspondence [3] and optical frameworks, and the majority of these applications interminably definitively are ordering ever higher interpreting throughput

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

International Journal of Research Available and perpetually sizably voluminous at mistake correction ability. [4] Since a gigantic calculation is ineluctably destined in satisfying high throughput and incredible mistake amendment ability, control effective structure turns out to be more principal in BCH disentangling. When all is said in done, a BCH decoder that can change t bits at most extreme is made out of three principle pieces, to be specific, disorder (SC), computation key-condition illuminating (KES), and Chien seek (CS) [2]. Given a got code word R(x), the SC figures 2t disorders, and the KES causes the mistake locator polynomial  $\Lambda(x)$  using the disorders. Determinately, mistake position E(x) is discourage Computerized Object 10.1109/TCSII.2015.2482958 Identifier mined by finding the underlying foundations of  $\Lambda(x)$  predicated on the CS calculation. In a parallel BCH decoder, the CS is a noteworthy supporter of the puissance utilization and takes up to a moiety of general power utilization. Many investigations have proposed productive structures to lessen the puissance utilization of the CS. Early end methods introduced in [7] are to dispose of excess calculations in the wake of finding the last mistake. A

supplemental blunder counter is augmented at whatever point a mistake is found, and the CS is killed when the counter matches the quantity of blunders recognized in the KES. Though the early end is easy to execute and useful in the BCH decoder managing a humble number of blunders, its energy safeguarding is worthless when the mistake correction capacity is not minuscule.[10] In more proficient technique called polynomial request decrease (POR) was proposed to change the mistake locator polynomial at whatever point a blunder is found. The request of the locator polynomial is decremented by piecemeal and in the end winds up noticeably zero when all blunders are identified. The POR [8] bit by bit cripples the CS by shutting down the hardware related with one polynomial component at any given moment. Though International Journal of Research Available the POR was prosperous for serial BCH decoders, it is difficult to apply the system to the parallel engineering on account of the boggling mind polynomial refresh. Moreover, the puissance saving of all the foremost calculations, including the early end [6] and the POR relies upon the position of mistakes. For example, if blunders are situated at the end of a code word, the

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

strength saving is not as noteworthy as the case that mistakes are situated at the beginning. In this short, we propose a beginning methodology in which the parallel CS is decayed into two stages. The initial step is gotten to each cycle, yet the second step is actuated just when the initial step is prosperous, bringing about a less number of get to. The proposed two-stage approach is theoretically homogeneous to that in [9]. Yet the two-stage approach, by and large, prompts the incrementation in basic way postponement and inactivity, the disadvantages are settled in this brief by utilizing a productive pipelined structure. Not at all like the predecessor models the proposed engineering can protect the power utilization paying little heed to mistake areas.

#### 2. RELATED WORK

Among sundry mistake correction codes used to recover ruined code words in correspondences and capacity frameworks, the Bose-Chaudhuri-Hocquenghem (BCH) code , is a standout amongst the most generally utilized arithmetical codes because of its strong blunder amendment execution and reasonable equipment multifaceted design. The paired BCH code has been

utilized in differing frameworks. for example, propelled strong state stockpiles optical fiber correspondence and frameworks, and a large portion of these interminably applications injuctively are higher interpreting approving ever throughput and perpetually tremendously monster blunder amendment ability. Since an enormous calculation is ineluctably fated in slaking high throughput and energetic mistake correction ability, control proficient structure turns out to be more vital in BCH deciphering We propose an early approach in which the parallel CS is deteriorated into two stages. The initial step is gotten to each cycle, however the second step is initiated just when the first step is prosperous, bringing about a less number of get to. The proposed International Journal of Research Available at two-stage approach reasonably homogeneous to that. But the two-stage approach, when all is said in done, prompts the increment in basic way postponement the and dormancy. disadvantages are settled in this brief by utilizing a proficient pipelined structure. Not at all like the point of reference structures, the proposed design can protect the strength utilization paying little heed to mistake areas.

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

#### 3.IMPLEMENTATION

#### 3.1 PARALLEL CS ARCHITECTURE

Give us a chance to consider a twofold BCH (n,k,t) code over GF(2m), where n is the code length, k is the message length, and t is the maximal number of correctable blunder bits. All the more exactly, n = k + mt, where m is the field measurement that satisfies 2m - 1 $\geq$  n. Amid the disorder predicated deciphering the blunder locator polynomial conveyed by the KES is communicated as  $\Lambda(x)=t$   $j=1\lambda jxj+1=Y(x)+1$ . To decide the blunder position E(x), the CS iteratively substitutes  $\alpha i$  into (1) for  $1 \le i \le n$  and recognizes the nearness of a mistake when  $\Lambda(\alpha i)=0$  or Y  $(\alpha i)=1$ . By and by, p-parallel CS engineering is generally executed to accomplish a high through put, where the parallel element p is the quantity of ai supersessions performed simultaneously. Fig. 1 portrays the p-parallel CS engineering that decreases the quantity of cycles from n to n/pby ascertaining Y ( $\alpha wp+i$ )= t j=1  $\lambda i \alpha w p i \alpha i = t i = 1 \omega i(w) \alpha i for 1 \le i \le p.$  (2) AsshowninFig.1, anintermediatevalueωj intheithregistersissimultaneouslyfedtopfinite fieldmultipliers(FFMs)located in a similar section. Therefore, the p-parallel structure is made out of pt FFMs, pt-input m-bit limited

field adders, pm-bit comparators, tm-bit registers, and tm-bit multiplexers. Since all components over GF(2m) can be communicated 1×m lattice, as a the calculation in the CS can be defined by using the paired networks. In this brief,  $\alpha i(a:b)$  for 0 < b < a < m-1 is used to exactly signify a part of component ai going from the bth bit to the ath bit. Specifically,  $\alpha i(a) =$ αi(a:a) means a specific piece, and αi verifiably signifies αi(m-1:0). For instance,  $\alpha 4(3:2) = 1 \times \alpha 3 + 0 \times \alpha 2$  and  $\alpha 4(3) = \alpha 4(1) = 0$  $\alpha 4(0) = 1$  for  $\alpha 4 = \alpha 4(3:0) = 1 \times \alpha 3 + 0 \times \alpha 2$  $+1\times\alpha 1$   $+1\times\alpha 0$  over GF(24). As indicated by the FFM situated on the ith push and jth segment in Fig. 1 can be changed to a paired network increase as pt FFMs predicated on (2) and (3), the whole p-parallel CS can be reformulated as Y (w)=  $Y(\alpha wp+1) \cdot \cdot \cdot Y$  $\alpha wp + (p-1)Y \quad (\alpha wp + p) \quad design \quad for \quad parallel$ CS. The customary CS is disintegrated into two stages to accomplish a foremost power saving by lessening access to the second step. Under the equipollently likely mistake low-control CS show. the design is contrasted and the customary engineering for sundry arrangements of field measurement, parallel component, and correction capacity. blunder Exploratory outcomes demonstrate that the proposed

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

engineering decreases up to half power utilization contrasted and the regular parallel CS. The puissance saving turns out to be more principal as the parallel element or the field measurement increments. The proposed two-stage CS is also appropriate to other straight piece codes, for example, the Reed–Solomon codes.

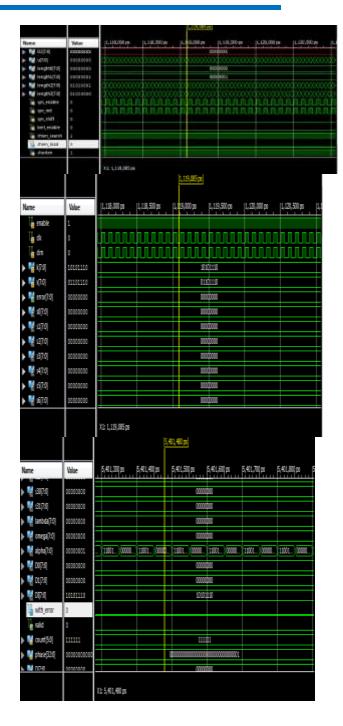

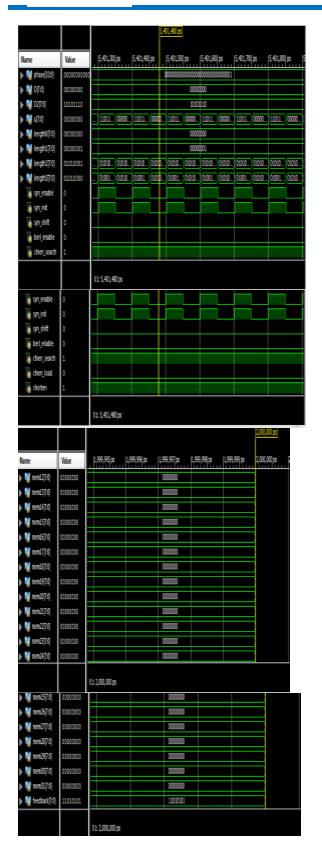

#### SIMULATION RESULTS:

CS low power, depending on the size of the field of construction of the proposed two different configurations, and errorstep correction capability of the horizontal factor compared to traditional construction. At the operating frequency of 200 MHz for all the CS blocks with a 130-nm CMOS technology is, and equally probable error model [7], [8] adopted simulations power consumption. More precisely, V errors BCH (n, k, t) signals, the average bit of a distance between two adjacent errors n / V model, every bit of the code word received is from the same error occurs when the reference is corrupted.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

For fair comparison, all of the BCH codes to model the rate of 0.93 is designed and shown in Fig 8. Set the horizontal element. 4, the proposed increase in the size of the field of development becomes even more important as a result of the construction, and a small number of bits are sufficient in electricity savings increase. For example, BCH for the proposed two-step structure (8752, 8192, 40) GF (214) 49.3% power savings over the code FFM partial opening of the first four MSBs will be processed. Moreover, Figs. 5 and 6 horizontal error correction factor and illustrate how it affects the efficiency of power saving. horizontal element increases, the energy savings and the horizontal aspect ratio closer to 50% than the energy saving ratio of 8. It is error correction capability is almost independently shown to be saturated when. In figs. 3-6, we estimate an offset between savings and in spite energy simulation, a simplified energy model (9) can be used as a good estimate. Due to the additional buffers are addressed in Section III, proposed construction of an the approximately 10% increase in hardware complexity.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

CONCLUSION: This is neither a new lowpower architecture for parallel CS provided. By reducing access to the second stage of the conventional CS to achieve significant power savings is decomposed in two steps. Error operate under the same ownership, the less energy the size of the CS in the construction in different sector error-correction configurations, and capability of the horizontal factor compared traditional construction. From the experimental results. the proposed construction of a 50% reduction in power consumption compared to the conventional CS horizontal show. Power saving horizontal factor or increase the size of the field will become more and more important. ReedSolomon codes, such as the proposed two-step CS also applies to other linear block codes.

#### REFERENCE

- [1] S. Lin and D. J. Costello, Error Control Coding: Fundamentals and Applications, 2nd ed. Englewood Cliffs, NJ, USA: Prentice-Hall, 2004.

- [2] S. B. Wicker, Error Control Systems for Digital Communication and Storage.

Englewood Cliffs, NJ, USA: Prentice-Hall, 1994.

- [3] Y. Lin, C. Yang, C. Hsu, H. Chang, and C. Lee, "A MPCN-based parallel architecture in BCH decoders for NAND Flash memory devices," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 58, no. 10, pp. 682–686, Oct. 2011.

- [4] Y. Lee, H. Yoo, and I.-C. Park, "Highthroughput and low-complexity BCH decoding architecture for solid-state drives," International Journal of Research Available at https://edupediapublications.org/journals p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 09 August 2017 Available online:https://edupediapublications.org/journals/index.php/IJR/ P a g e | 423 IEEE Trans. Very Large Scale Integr. Syst., vol. 22, no. 5, pp. 1183–1187, May 2014.

- [5] X. Zhang and Z. Wang, "A lowcomplexity three-error-correcting BCH decoder for optical transport network," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 59, no. 10, pp. 663–667, Oct. 2012.

- [6] K. Lee, S. Lim, and J. Kim, "Low-cost, low-power and high-throughput BCH decoder for NAND flash memory," in Proc. IEEE ISCAS, May 2012, pp. 413–415.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 07 March 2018

- [7] Y. Wu, "Low power decoding of BCH codes," in Proc. IEEE ISCAS, May 2004, pp. II-369–II-372

- . [8] S. Wong, C. Chen, and Q. M. Wu, "Low power Chien search for BCH decoder using RT-level power management," IEEE Trans. Very Large Scale Integr. Syst., vol. 19, no. 2, pp. 338–341, Feb. 2011.

- [9] H. Weingarten, E. Sterin, O. A. Kanter, and M. Katz, "Low Power Chien-Search Based BCH/RS Decoding System for Flash Memory, Mobile Communications Devices and Other Applications," U.S. Patent 2010 013 1831 A1, May 27, 2010.

- [10] Y. Chen and K. K. Parhi, "Small area parallel Chien search architectures for long BCH codes," IEEE Trans. Very Large Scale Integr. Syst., vol. 12, no. 5, pp. 545–549, May 2004.