#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 17 December 2017

### **High Efficiency Single Phase Transformer PV Inverter Topology**

#### G.Krishnaiah

M.Tech(Digital Systems and Computer Electronic)

Abstract: Renewable energy sources are getting more and more widespread, mainly due to the fact that they generate energy by keeping the environment clean. Most of these systems have an isolation transformer included, which if excluded from the system would increase the efficiency and decrease the size of PV installations, furthermore it would lead to a lower cost for the whole investment. For safety reasons grid connected PV systems include galvanic isolation. In case of transformerless inverters, the leakage ground current through the parasitic capacitance of the PV panels, can reach very high values. A common-mode model based on analytical approach is introduced, used to predict the commonmode behavior, at frequencies lower than 50kHz, of the selected topologies and to explain the influence of system imbalance on the leakage current. It will be demonstrated that the neutral inductance has a crucial influence on the leakage current method.

**Keywords-**Leakage current, parasitic capacitance, switching converter.

#### I. INTRODUCTION

The importance of renewable energy sources is recognized by both the general public and the power industries. Some researchers believe the concern for environmental damage is now an even greater priority than the need to preserve the finite natural resources for future generations. PHOTOVOLTAIC (PV) inverters become more and more widespread within both private and commercial circles. These grid/load-connected inverters convert the available direct current supplied by the PV panels and feed it into the utility grid/load. There are two main topology groups used in the case of grid/load-connected PV systems, namely, with and without galvanic isolation. Galvanic isolation can be on the dc side in the form of a high-frequency dc-dc

transformer or on the grid/load side in the form of a big bulky ac transformer. Both of these solutions offer the safety and advantage of galvanic isolation, but the efficiency of the whole system is decreased due to power Losses in these extra components. An

improvement in inverter efficiency and a reduction in cost have been achieved by omitting the 50 Hz power transformer (transformer less) and by optimizing the Inverter current control strategies. The inverter described in this project is specifically for grid/Loadconnected PV Systems, it can be used for other traditional applications such as in uninterruptible Power supplies (UPS), motor controls and voltage regulation systems. The main aim of this project was to develop a new design procedure for a single-phase, transformer less PV inverter system suitable for grid/Load connection, which would lead to higher inverter efficiencies, improved output power quality and reduced cost. Detailed performance analyses of both the unipolar and the bipolar switched inverters will be carried out before a final choice is made.

Techniques to remove DC offset current will be investigated to ensure that the DC current injected into the grid/Load system is maintained within the legal limits irrespective of its source. To improve the quality of inverter output current, a suitable efficient and cost effective ripple current filter design will also be developed. The specific objectives of the project are summarized

- High efficiency

- Constant High Frequency Common Mode Voltage

- Very Small Leakage Current

- Low Total Harmonic Distortion

# R UIR

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 17 December 2017

A single-phase grid-connected inverter is usually used for residential or low-power applications of power ranges that are less than 10 kW [1]. Types of single-phase grid connected inverters have been investigated [2]. A common topology of this inverter is full-bridge three-level. The threelevel inverter can satisfy specifications through its very high switching, but it could also unfortunately increase switching losses, acoustic noise, and level of interference to other equipment. Improving its output waveform reduces its harmonic content and, hence, also the size of the filter used and the level of electromagnetic interference (EMI) generated by the inverter's switching operation [3]. Multilevel inverters are promising; they have nearly sinusoidal output-voltage waveforms, output current with better harmonic profile, less stressing of electronic components owing to decreased voltages, switching losses that are lower than those of conventional two-level inverters, a smaller filter size, and lower EMI, all of which make them cheaper, lighter, and more compact [3], [4].

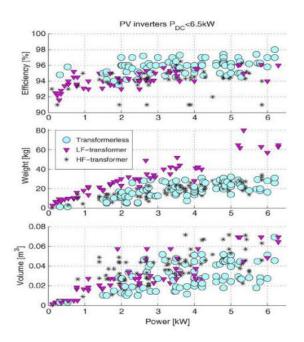

Fig. 1 has been made from the database of more than 400 commercially available PV inverters, presented in a commercial magazine about PV systems. The conclusion drawn from these graphs is that transformer less inverters have higher efficiency and smaller weight and size than their counterparts with galvanic separation.

Fig.1. Advantages and drawback of different inverter topologies.

#### II. PREVIOUS WORK

In order to minimize the ground leakage current through the parasitic capacitance of the PV array, several techniques have been used. One of them is to connect the midpoint of the dc-link capacitors to the neutral of the grid, like the half-bridge, neutral point clamped (NPC), or three-phase full bridge with a split capacitor topology, thereby continuously clamping the PV array to the neutral connector of the utility grid.

Half-bridge and NPC type of converters have very high efficiency, above 97%. Furthermore, the topology proposed reduces the dc current injection, which is an important issue in the case of transformer less topologies and is limited by different standards. The non-injection of dc current into the grid is topologically guaranteed by adding a second capacitive divider to which the neutral terminal of the grid is connected. An extra control loop is introduced that compensates for any dc current injection, by controlling the voltage of both capacitive dividers to be equal.

# R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 17 December 2017

Another solution is to disconnect the PV array from the grid, in the case of H-bridge (HB) inverters, when the zero vector is applied to the load (grid). This disconnection can be done either on the dc side of the inverter (like the topology from and H5 topology from Solar Technologies AG) or on the ac side (like the Highly Efficient and Reliable Inverter Concept (HERIC) topology from Sun ways). A new topology called HB zero-voltage state rectifier (HB-ZVR) is given where the midpoint of the dc link is clamped to the inverter only during the zero-state period by means of a diode rectifier and one switch.

The aim of the work presented in this paper is to introduce a common-mode model based on analytical approach for the single phasephase inverter connected to the utility grid with the help of NPC multi level inverter. This model will be used to predict the common-mode behavior, at frequencies lower than 50kHz, of the selected topologies and to explain the influence of system imbalance on the ground leakage current. It will also be shown, that the neutral inductance has a crucial influence on the common mode behavior of the topology, thereby directly influencing the ground leakage current of the system. Simulation results will be presented in case of the NPC topology in order to validate the simulation model.

### III. TRANSFORMER LESS TOPOLOGY ANALYSIS

As mentioned in previous works, the common mode voltage generated by a topology and modulation strategy will greatly influence the ground leakage current that flows through the parasitic capacitance of the PV array. Generally, the utility grid doesn't influence the common mode behavior of the system, thus it may be complete that the generated common mode voltage of an explicit electrical converter topology and modulation strategy may be shown employing a straightforward resistor as load. Therefore, within the case of simulations, solely a resistive load is employed, and therefore the common-mode voltage is measured between the dc+terminal of the dc supply and therefore the grounded middle point of the resistor as shown in Fig. 2..

Fig. 2. Test setup used for common-mode voltage measurement.

In the following, simulation results obtained using MATLAB/SIMULINK are shown. The simulation step size is  $0.1~\mu s$ , with an 8-kHz switching frequency.

Simulation parameters:

$L_f = 1.8 \text{ mH}$  filter inductance;

$C_f = 2 \mu F$  filter capacitance;

$R = 7.5 \Omega$  load resistance;

$V_{dc} = 350 \text{ V}$  input dc voltage;

$C_{dc} = 250 \mu F dc$ -link capacitance;

$C_G$ -PV = 100 nF parasitic capacitance of PV array;

Fsw = 8 kHz switching frequency for all cases except that the switching frequency for unipolar Pulse width modulation (PWM) has been chosen to be  $F_{sw}=4$  kHz, so the output voltage of the inverter has the same frequency for all cases.

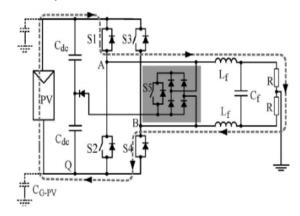

#### A. HB-ZVR Topology

Another solution for generating the zero-voltage state can be done using a bidirectional switch made of one IGBT and one Diode Bridge. The topology is detailed in Fig. 3, showing the bidirectional switch as an uxiliary component with a gray background. This bidirectional switch is clamped to the midpoint of the dc-link capacitors in order to fix the potential of the PV array also during the zero-voltage vector when S1–S4 and S2–S3 are open. An extra diode is used to protect from short-circuiting the lower dc-link capacitor.

During the positive half-wave, S1 and S4 are used to generate the active state, supplying a positive voltage

## R

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 17 December 2017

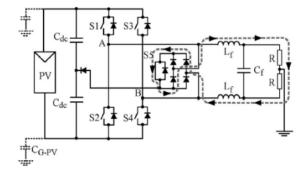

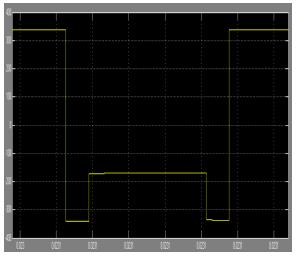

to the load, as shown in Fig. 3. The zero-voltage state is achieved by turning on S5 when S1 and S4 are turned off, as shown in Fig. 4. The gate signal for S5 will be the complementary gate signal of S1 and S4, with a small dead time to avoid short-circuiting the input capacitor. By using S5, it is possible for the grid current to flow in both directions; this way, the inverter can also feed reactive power to the grid, if necessary.

Fig. 3. Active vector applied to load, using S1 and S4 during positive half-wave.

Fig. 4. Zero vectors applied to load, using S5 during positive half-wave.

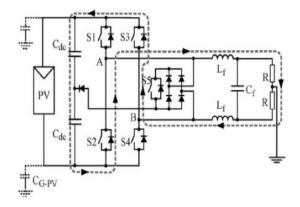

During the negative half-wave of the load voltage, S2 and S3 are used to generate the active vector and S5 is controlled using the complementary signal of S2 and S3 and generates the zero voltage state, by shortcircuiting the outputs of the inverter and clamping them to the midpoint of the dc-link.

Fig. 5. Dead time between turnoff of S1 and S4 and turn on of S5 during positive half-wave.

During the dead time, between the active state and the zero state, there is a short period when the freewheeling current finds its path through the anti parallel diodes to the input capacitor while all the switches are turned off. This is shown in Fig. 5 and leads to higher losses, compared to the HERIC topology, where the freewheeling current finds its path through the bidirectional switch, either through S5 or S6, depending on the sign of the current.

#### IV. SIMULATION RESULTS

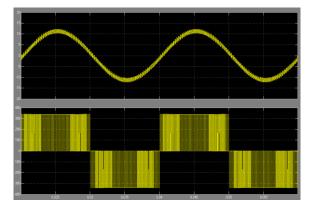

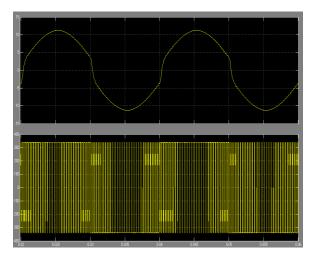

Fig. 6. HB-Unip topology: Load current and inverter output voltage.

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 17 December 2017

Fig. 7. HB-Unip topology: Voltage to ground and ground leakage current.

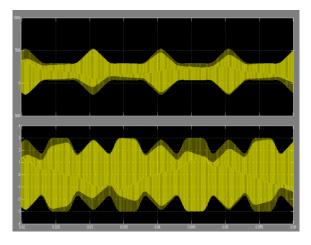

Fig. 8. HERIC topology: Load current and inverter output voltage.

Fig. 9. HERIC topology: Voltage to ground and ground leakage current.

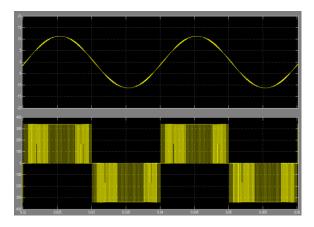

Fig. 10. HB-ZVR load current and inverter output voltage.

#### V. CONCLUSION

Bipolar PWM generates a constant common-mode voltage, but the efficiency of the converter is low, due to the two level output voltage. By using unipolar PWM modulation, the output of the converter will have three levels, but in this case, the generated common-mode voltage will have high-frequency components, which will lead to very high ground leakage currents. This paper has introduced a transformer less topology and given an alternative solution for the bidirectional switch, used to generate

### International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 17 December 2017

the zero-voltage state. The constant common-mode voltage of the HB-ZVR topology and its high efficiency make it an attractive solution for transformer less PV applications.

#### **REFERENCES**

- [1] "Trends in photovoltaic applications: Survey report of selected IEA countries between 1992 and 2007," IEA, Paris, France, Rep. IEA-PVPS T1-T17, 2008.

- [2] J. M. Carrasco, L. G. Franquelo, J. T. Bialasiewicz, E. Galvan, R. C. P. Guisado, M. A. M. Prats, J. I. Leon, and N. Moreno-Alfonso, "Power-electronic systems for the grid integration of renewable energy sources: A survey," IEEE Trans. Ind. Electron., vol. 53, no. 4, pp. 1002–1016, Jul. 2008.

- [3] "Photon international," The Photovoltaic Magazine, Apr. 2007.

- [4] R. Gonzalez, J. Lopez, P. Sanchis, and L. Marroyo, "Transformer less inverter for single phase photovoltaic systems," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 693–697, Mar. 2007.

- [5] B. Sahan, A. N. Vergara, N. Henze, A. Engler, and P. Zacharias, "A single stage PV module integrated converter based on a low-power current source inverter," IEEE Trans. Ind. Electron., vol. 55, no. 7, pp. 2602–2609, Jul. 2008.

- [6] R. Gonzalez, E. Gubia, J. Lopez, and L. Marroyo, "Transformer less single-phase multilevel-based photovoltaic inverter," IEEE Trans. Ind. Electron., vol. 55, no. 7, pp. 2694–2702, Jul. 2008.

- [7] J. Selvaraj and N. A. Rahim, "Multilevel inverter for grid-connected PV system employing digital PI controller," IEEE Trans. Ind. Electron., vol. 56, no. 1, pp. 149–158, Jan. 2009.

- [8] E. Gubía, P. Sanchis, A. Ursúa, J. Lopez, and L. Marroyo, "Ground currents in single-phase transformer less photovoltaic systems," Prog. Photo volt., Res. Appl., vol. 15, no. 7, pp. 629–650, 2007.

- [9] T. Kerekes, R. Teodorescu, and U. Borup, "Transformer less photovoltaic inverters connected to the grid," in Proc. APEC, Feb. 25–Mar. 1, 2007, pp. 1733–1737.

- [10] T. Kerekes, R. Teodorescu, C. Klumpner, M. Sumner, D. Floricau, and R. Rodriguez, "Evaluation of three-phase transformer less photovoltaic inverter topologies," in Proc. Eur. Conf. Power Electron. Appl., Sep. 2–5, 2007, pp. 1–10.6.

#### **BioData**

G.Krishnaiah completed M.Tech (Digital Systems and Computer Electronic).