#### Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

# Necessities of Low-Power Vlsi Design Strategies And Its Involvement With New Technologies

#### **MARATY MEENA**

maratymeena@gmail.com

### **Abstract**

The significant goal of this approach is to outline another circuit with low-control utilization, which is more productive and clever for offering help to most recent innovations and developments, for example, compact handsets, cell phones, calling-tablets, portable PCs/PCs and some more. In electronic-space, low-control wordings are most astounding needs, control exhaustment is a standout amongst the most essential focus in measuring up to with speedand-execution' of VLSI chips. The significant difficulties' available into the planning of lowcontrol VLSI chips resemble: size and similarity and power go down. Another real issue emerge while outlining the circuit of low-control VLSI configuration is budgetary viewpoint, that is taken a toll savvy reducements are required to make such gadgets. For control upkeep plot, spillage/spillage current in like manner accept a basic part in low power VLSI designs. Spillage/spillage current is transforming into an obviously indispensable piece of the total power dissipating of facilitated circuits. framework depicts about the diverse systems, approaches and in addition control organization plans for low power circuits and structures. For all the whole arrangement of low-control outlining of VLSI chips ensures that the cos lessening and versatility of gadget with appropriate power administration plans. Future troubles that must be met to plots low power predominant circuits are similarly discussed.

**Keywords:** Low-Power-VLSI Design, Power Management', power spillage, Processing Units, Power-Exhaustment.

### Introduction

The advantage of utilizing a blend of lowcontrol parts in a joint effort with low-control outline techniques is more vital now than whenever in late memory. Necessities for bring low-control use continue expanding basically as portions/segments' advance toward getting to be battery-powered, tinier and additionally require more value. In past, the genuine concentration organizers for the **VLSI** was zone, execution/execution' and monetary needs/cost'. Power thought was the discretionary concerned now-a-days, directly a day's vitality is the fundamental stressed because of the outstanding improvement and achievement in the field of individualized figuring contraptions and remote correspondence structure which ask for fast count and complex helpfulness with low-control use. The motivations for lessening power-use differentiate application'- to-application'. In the class of little scale filled battery worked flexible

#### International Journal of Research

# Available at

# https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

applications, for example, cell phones, the goal is to keep the battery lifetime and weight sensible and packaging cost low.

For high execution/execution' adaptable PCs, for instance, compact workstation the goal is to lessen the power spread of the contraptions bit of the system to a point which is about part of the total power diffusing. Finally for the unrivaled non battery worked structure, for example, workstations the general goal of vitality minimization is to diminish the system cost while ensuring whole deal contraption steady quality.

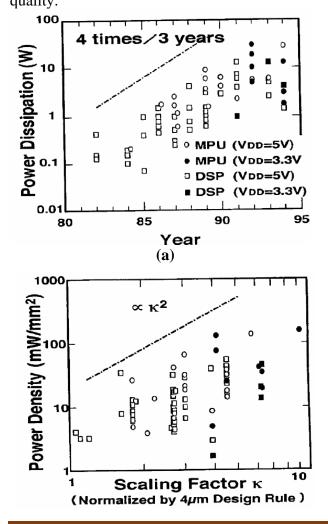

**(b)**

# **Fig.1 Power Dissipation Development**

For such high execution/performance' frameworks, process innovation has driven energy to the fore front to all elements in such plans. At process hubs underneath '100nm' innovation, control utilization because of spillage has joined exchanging action as an essential power administration concern. There are numerous procedures [5] that have been produced over the previous decade to address the constantly forceful power decrease prerequisites of a large portion of the superior. The essential low-power outline systems, ex., clock gating for lessening dynamic power, or various voltage edges (multi-Voltage) to diminish spillage current, are settled and bolstered by existing apparatuses [7].

### **Low-Power-Design Approach**

Many different kinds of approaches are available on different levels of designing the VLSI-circuits/chips for regulating the power-consumption' process. The following table Table-I, illustrates those parameters of VLSI designing. Viable power administration is conceivable by utilizing the distinctive

#### International Journal of Research

#### Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

techniques at different levels in VLSI-Configuration process. So fashioners require a shrewd approach for enhancing power utilizations in outlines.

# TABLE-I LOW POWER DESIGN APPROACHES

| Low-Power-Design     | Approaches            |  |

|----------------------|-----------------------|--|

| Stages               |                       |  |

| Level of Operating-  | Splitting and Low-    |  |

| System' [OS]         | Density-Power         |  |

|                      | Management            |  |

| Software-Level-      | Regular-Intervals,    |  |

| Design               | Localization and      |  |

|                      | Concurrent-Operations |  |

| Architectural-Level- | Pipelining',          |  |

| Design               | Redundancy', Data-    |  |

|                      | Encoding'             |  |

| Circuit(or)Logical-  | Logic-Nature',        |  |

| Level-Design         | Transistor-Sizing as- |  |

|                      | well-as Energy-       |  |

|                      | Sustainability        |  |

| Technology'-Level-   | Interval' and Multi-  |  |

| Design               | Thread Processing     |  |

In a design circuit' three parts are in charge of energy/power' dispersal: dynamic-power, cut-off-power as-well-as static-power'. Out of these, dynamic-power' or exchanging-power' is fundamentally control dispersed while charging or releasing capacitors and is portrayed beneath [4][5]:

$$P_{DYN} = CL/Vdd2*X_f$$

(1)

Where CL indicates Load-Capacitance', a component of fan'-out', wire-length' and' transistor-estimate, Vdd indicates Supply-Voltage, which has been dropping with progressive process hubs X indicates Activity-Factor, which means how frequently by and large, the wires switch, f indicates Clock Frequency, which is expanding at each progressive process hub. Static-Power or spillage-Control is a component of the supply voltage [Vdd'], the exchanging edge [Vt], and transistor sizes. As process hubs recoil, spillage turns into a more noteworthy wellspring of vitality utilize, devouring no less than 30% of aggregate power [1][3].

### **Initial Needs of Power-Dispersal**

#### International Journal of Research

### Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

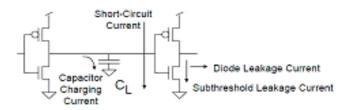

Fig.2 CMOS-Power-Dispersal

Crowbar streams, caused at the point when both the PMOS and NMOS gadgets are at the same time on, likewise add to the spillage control dissemination [1]. Most circuit level minimization strategies concentrate just on Sub limit spillage lessening without considering the impacts of door spillage [15] .For this MTCMOS conspire [2] has been proposed for decrease of sub-threshold spillage current in rest mode. Figure-2 demonstrates the different parts in charge of energy/power' dispersal in CMOS.

### **Low-Power-Design-Strategy**

From the above area it is uncovered that there are three degrees of flexibility in the VLSI-configuration-space: Voltage, Physical Capacitance and information movement. Improving for more power involves an endeavor to decrease at least one of these variables. This segment quickly portrays about their significance in control improvement process.

## (a) Voltage-Analysis

In view of its quadratic relationship to control, voltage diminishment offers the best methods for limiting force consumption. Without requiring any unique circuits and advancements, a factor of two lessening in supply voltage yields a factor of four declines in control utilization. Shockingly, there is speed punishment for supply voltage lessening and deferrals radically increment as Vdd ways to deal with the edge voltage Vt of the gadget. The way to deal with diminishes the supply voltage without misfortune in throughput is to adjust the edge voltage of the gadgets. Decreasing the Vt enables the supply voltage to be downsized without misfortune in speed. The farthest point of how low the Vt can go is set by the requirement to set sufficient clamor edges and control the expansion in the sub-threshold spillage current [1][5][6].

### (b) Physical Capacitance

Dynamic power utilization depends straightly on the physical capacitance being exchanged. In this way, notwithstanding working at low voltages, limiting capacitances offer another procedure for limiting force consumption. The capacitances can be kept at

#### International Journal of Research

# Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

the very least by utilizing less rationale, littler gadgets, less and shorter wires [3][4][6]. Likewise with voltage, be that as it may, we are not allowed to upgrade capacitances autonomously, for instance decreasing gadget sizes diminishes physical capacitance, however it additionally lessens the present drive of the transistor influencing the circuit to work all the more gradually.

### (c) Exchanging Activity

There are two segments to exchanging action: Fclk which decides the normal periodicity of information landings and E(sw) which decides what number of advances every entry will generate [2][14]. E(sw) is diminished by choosing legitimate calculations engineering advancement, by appropriate decision of rationale topology and by rationale level improvement which brings about less power [7][15]. The information movement E(sw) are joined with the physical capacitance C to got switch capacitance Csw=C.E(sw),which portrays the normal capacitance charge amid every datum period1/Fclk which decides the power devoured by CMOS circuit [8][11][9].

TABLE-II Low-Power-Scheme Usages

| Classical-<br>Techniques' | Intelligent-<br>Power- | Power-<br>Leakages' |

|---------------------------|------------------------|---------------------|

|                           | Diminishing'           |                     |

| Cloak-Gate-               | Cloak-                 | Diminished          |

| Nature'                   | gating'                | under 10vt          |

| Power-Gate-               | Efficient-             | Power-              |

| Nature'                   | Power-                 | Gate-               |

|                           | Management             | Reduced             |

|                           | -Technique'            | up-to 5vt           |

| Variable-                 | VF-Level-1             | Back'-              |

| Frequency'                |                        | Bias-               |

|                           |                        | Nature'             |

| Variable-                 | Consistent-            | Minimize-           |

| Voltage'-                 | Voltage'-              | Oxide'-             |

| Frequencies'              | Supply'                | Density'            |

### **Designing Circuit-Nature and Logics**

In the wake of choosing innovation, the emphasis is on outline strategies to advance power. One needs to begin by choosing the suitable rationale door from the standard battery-cell library. Each entryway in a standard battery-cell library utilizes the littlest transistors and has numerous renditions with various drive qualities, sizes, delays, numerous edge voltage and power utilization. Since the fundamental parameter for controlling dynamic power is the power-supply voltage, battery-cell creators

#### International Journal of Research

# Available at

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01 January 2017

https://edupediapublications.org/journals

regularly plan and portray the entryways to work at voltages as much as 30% lower than the control supply voltage [1]. Bringing down the power-supply voltage produces littler streams, bringing about more deferral. Nonetheless, this log jam is satisfactory if the plan isn't pushing the edges of guaranteed innovation. Expanding the edge voltage lessens the spillage current in gadget. Spillage control additionally the controlled by planning rationale doors with various edge voltage gadgets [12][16], including standard high and low limit voltage gadgets. Figure-4 demonstrates the variety of entryway defer Vs spillage control.

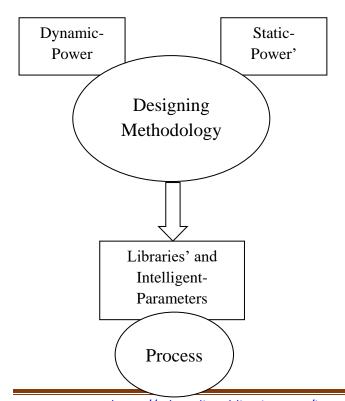

'Power-Integrity'

## Fig.3 Intelligent Power Management Scheme

Physical plan apparatuses translate the power aim and actualize the format effectively, from position of exceptional cells to directing and streamlining crosswise over power areas within the sight of numerous corners, modes, and power states, in addition to producing inconstancy [5][2][3]. An undeniably normal strategy to diminish control in physical configuration is the utilization of numerous voltage islands [areas'], which enables a few pieces to utilize bring down supply voltages than others, or to be totally closed off for specific methods of operation [15][6]. Clocks are a noteworthy wellspring of dynamic power utilization. Low-control clock tree amalgamation (CTS) techniques [5][6][8] incorporate bringing down general capacitance and limiting changing movement to accomplish control sparing. In any case, getting the best power comes about because of CTS relies upon capacity to combine the tickers for numerous corners and modes simultaneously within the sight of outline and assembling changeability, and in multi-voltage streams

#### International Journal of Research

## Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

[1][17][8]. Power gating system is viable for lessening spillage control by incidentally killed the circuit [17][2][8]. This impermanent shutdown time can likewise call as "low-power'-'mode" or "inert-mode". Whenever circuit pieces are required for operation indeed they are actuated to "dynamic'-mode". Closing down the pieces can be expert either by programming or equipment. Presently a-days a committed power administration controller is utilized for this reason [17]. Table-3 gives the exchange off related with the different power administration methods [17].

## **Literature Survey**

In the year of 2010, the author "Prasad Subramanian" proposed a paper titled "Power management for optimal power design", in that he described such as: an advancement of energy utilization is one of the greatest difficulties IC fashioners confront today. In spite of the fact that power advancement has dependably been basic for battery-worked outlines, the proceeded with development of framework execution with each new age of semiconductor innovation, alongside the expanding accentuation on "green" and "clean" specialized applications, has made power improvement fundamental

notwithstanding for divider controlled plans. Viable power administration includes determination of the correct innovation, the utilization of streamlined libraries and IP (protected innovation), and plan strategy. It additionally implies advancing both dynamic power and static spillage control. This article looks at the different ways to deal with viable power administration.

In the year of 2009, the publishing hub "Mentor Graphics" published a research summary titled "Low power physical design with Olympus SOC", in that they described such as: for some, plans, enhancing for control is as critical as timing, because of the need to lessen bundle cost and expand battery life. In any case, the complexities of planning lowcontrol chips at cutting edge process hubs can adversely affect execution and time-toadvertise. Low power configuration includes juggling full scale level practical intricacy issues (numerous operational modes), and small scale level process and assembling issues (different outline corners) that could have clashing force, timing, flag trustworthiness (SI), manufacturability, and territory conclusion prerequisites. In this paper, we investigate methods utilized as a part of successful low

#### International Journal of Research

# Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

power IC configuration, depict the essential difficulties of low-control plan, and examine how the Mentor Graphics place and course framework executes the ideal low-control arrangement through all means of the physical outline stream.

**Conclusion**

The necessity for cut down power systems is being driven by many market areas. Deplorably delineating for low-control adds' another estimation to the authoritatively complex arrangement issue and the arrangement must be improved for control and furthermore Performance and Area. In conclusion unique issues and genuine troubles seeing low power traces are according to the accompanying:

Advancement Scaling: It relates with the going with parts like: Capacitance per center reduces by '30%', Electrical center points augments by '2X', Die assess creates by '14%'(Moore's Law), Supply Voltage diminishes by '15%' and Frequency Increases by '2X'. To meet these issues respectably '2.7X' dynamic-power will increase.

Spillage/Leakage-Power: To deal with repeat request Vt will be scaled which comes to fruition high spillage control. A low voltage/low edge advancement and circuit setup approach, concentrating on supply voltage around 1V and working with reduced edges.

Dynamic power organization techniques, varying supply voltage and execution speed as showed by the activity estimation. Low power interconnect, using advance development, reduced swing or activity approach.

### References

[1]. Michael Keating, David Flynn, Robert Aitken, Ala Gibsons and Kaijian Shi, "Low Power Methodology Manual for System on Chip Design", Springer Publications, New York, 2007.

[2]. Creating Low-Power Digital Integrated Circuits The Implementation Phase, Cadence, 2007.

[3].Liu, Weidong, Xiaodong Jin, Xuemei Xi, James Chen, Min-Chie Jeng, Zhihong Liu, Yuhua Cheng, Kai Chen, Mansun Chan, Kelvin Hui, Jianhui

# Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

Huang, Robert Tu, Ping K Ko, and Chenming Hu, BSIM3v3.3 MOSFET Model User's Manual, Department of Electrical Engineering and Computer Sciences, University of California-Berkeley, 2005.

- [4]. Glasser, Lance A, and Daniel W Dobberpuhl, TheDesign and Analysis of VLSI Circuits, Addison-Wesley Publishing Co, 1985.

- [5]. Shekar Borkar, "Design Challenges of Technology Scaling," IEEE Micro, July/August 1999, pg 23.

- [6]. T. Inukai, et.al, "Boosted Gate MOS (BGMOS): Device/Circuit Cooperation Scheme to Achieve Leakage-Free Giga-Scale Integration," Proc. CICC 2000, pp.409-412.

- [7]. F.Hamzaoglu and M. Stan, "Circuit-Level Techniques to Control Gate Leakage for sub 100nm CMOS," Proc. ISLPED, pp. 60-63, Aug. 2002.

- [8]. Y. Yeo, et.al, "Direct Tunneling Gate Leakage Current in Transistors with

Ultrathin Silicon Nitride Gate Dielectric," IEEE Electron Devices Letters, vol.21, no.11, pp. 540-542, Nov.2000.

- [9]. S. Mutoh, et.al, "1-V Power Supply High-Speed Digital Circuit Technology with Multi-Threshold Voltage CMOS,"IEEE Journal of Solid State Circuits, vol. 30, no. 8, pp. 847-854, Aug. 1995.

- [10]. M.Alidina, j. Monterio, S. Devadas, M. Papaefthymiou. A.Ghosh and "Precomputation -based Sequential logic optimization for low power" Proceedings of the 1994 International Workshop on Low Power Design, pages 57-62, April 1994. [11] .Anand Iyer, "Demystify power gating and stop leakage cold", Cadence Design Systems, Inc.

- [12] .De-Shiuan Chiou, Shih-Hsin Chen, Chingwei Yeh, "Timing driven power gating", Proceedings of the 43rd annual conference on Design automation, ACM

#### **International Journal of Research**

# Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 01

January 2017

Special Interest Group on Design Automation, pp.121 - 124, 2006.

[13] .B.Perman, "Design technologies for VLSI design", encyclopedia of computer science, 1995.

[14] .Mentor Graphics, "Low power physical design with Olympus SOC", Place and route white paper, March 27, 2009.

[15]. Rahul. M.Rao, Jeffery L.Burns, Richard B.Brown, "Circuit Techniques for gate and subthreshold leakage minimization in future CMOS technologies" Proc. ISLPED, pp70-73, 2002.

[16] .J.kao, Siva Narendra, Ananta Chandra Kasan, "Subthresh leakage modeling and reduction technique", 2002.

[17] Prasad Subramanian, "Power management for optimal power design", ESILICON, Corp.2010.

MARATY MEENA received her B.Tech in ECE in Gokaraju Rangaraju Institute of Technology and sciences in the year 2006 Miyapur, R.R.Dist, Telangana, and M.TECH received in ECE (VLSI and Embedded Systems) in Vivekananda Institute of Engineering and Technology in the year 2016 Bogaram, Keesara, R.R.Dist, Telangana, India.

### **AUTHOR**