# R

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 16 June 2018

# Design a High Speed and Energy Efficient Novel FFT Using CSKA

## <sup>1</sup> GARLAPATI SRAVANTHI, <sup>2</sup> SHAIK KHAMURUDDEEN

<sup>1</sup>M.tech-Scholar, Dept of ECE, KKR & KSR Institute of Technology and Sciences, Guntur, A.P. <sup>2</sup>Associate Professor, Dept of ECE, KKR & KSR Institute of Technology and Sciences, Guntur, A.P.

ABSTRACT: The DFT (Discrete Fourier Transform) is a significant technique in the fields such as Telecommunications and Digital Signal Processing (DSP). An efficient algorithm for enumerating the DFT and its inverse is Fast Fourier Transform (FFT). The FFT processor plays a key role in the field of communication systems such as Digital Video or Audio Broadcasting, Wireless LAN with Standards of IEEE 802.11, High Speed Digital Subscriber Lines etc. The existed structure utilizes AND-OR-INVERT (AOI) and OR-AND-INVERT (OAI) compound gates for the skip logic. The existed system is complex in area. Hence, we propose an algorithm which is area efficient and consumed delay in previous algorithm. The proposed design is implementation in Xilinx software.

KEY TERMS: Single Path Delay Feedback (SDF), Serial in Serial out Shift Register, Fast Fourier Transform (FFT), CSKA, Folding Technique.

#### I. INTRODUCTION

The Fourier Transform is an inevitable approach in signal processing. The Discrete Fourier Transform decomposes a set of values into different components of frequency. The Fast Fourier transform (FFT) is an appropriate technique to do manipulation of DFT. The algorithm of FFT was devised by Cooley and Tukey in order to decrease the amount of complexity with respect to time and computations.

The hardware of FFT can be implemented by two types of classifications- memory architecture and pipeline architecture. The memory architecture comprises a single processing element and various units of memory.

The merits of memory architecture include low power and low cost when compared to that of other styles. The specific demerits are greater latency and lower throughput. The above demerits of the memory architecture are totally eliminated by pipeline architecture at the expense of extra hardware in an acceptable way.

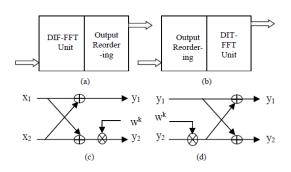

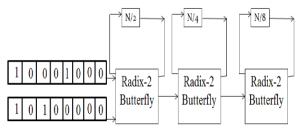

The various types of pipeline architecture include Single delay feedback (SDF), Single delay commutator (SDC) and multiple delay commutator (MDC). The pipeline architecture is a regular structure which can be adopted by using hardware description language in an easy manner. In the recent years, the communication systems need to transmit voice and video signals of high quality in an efficient manner. In present day the efficient module is high speed, reliable communication. technology of The algorithms of FFT can be grouped into fixed-radix, mixed radix and split radix algorithms in a rough manner. The basic categories of algorithms of FFT include -Decimation infrequency (DIF) and the Decimation-in-time (DIT) as shown in Figure 1.

Both of these algorithms depend on disintegration of transformation of an Npoint sequence into many subsequences in

# ®

# **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 16 June 2018

a successive manner. There is no major difference between them as far as complexity of computation is concerned. Generally DIT deals with the input and output in reverse sequence and normal sequence respectively, while DIF deals with input and output in normal sequence and reverse sequence respectively. Only Decimation-in-frequency (DIF) algorithm will be taken into consideration.

Figure 1: (a) DIF FFT processing (b) DIT FFT processing(c) DIF FFT butterfly (d) DIT FFT butterfly

#### **II.EXISTED SYSTEM**

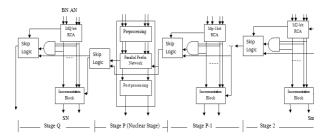

The existed structure is depends on uniting the incrementation and the concatenation schemes with the Conv-CSKA structure, and hence, it is indicated as CI-CSKA. The existed hybrid variable latency CSKA structure is exhibit in below figure 2.

Fig 2. The structure of the existed hybrid variable latency CSKA

It gives us with the ability to utilize simpler carry skip logics. The logic

utilized is AOI/OAI compound gates which replaces 2:1 multiplexers. The gates, which contain fewer transistors, have lower area, delay and less power consumption when compared with the 2:1 multiplexer. Hence, in this structure, through the skip logics, the carry becomes propagate SO. it complemented. Therefore, the complement of the carry is generated at the skip logic output of even stages.

existed structure The has less propagation delay with a slightly less area. Hence, while the AOI (or OAI) gate power consumptions are smaller than that of the multiplexer, the existed CI-CSKA power consumption is a little more than that of the conventional one. This is because of the maximize in the number of the gates, which imposes higher wiring capacitance.

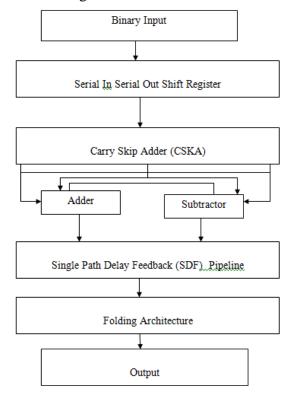

#### III.PROPOSED SYSTEM

Proposed method are used in binary input is going to the serial input serial output (SISO) shift register as shown in Figure 3. In proposing algorithm consist of SISO, and carry skip adder (CSKA), adder, Subtractor, Single path Delay Feedback (SDF) Pipeline, Folding architecture. SISO: - SISO technique depends on the binary input. Suppose the binary input of the system is 8 word length, then eight delay flip flops are utilized in SISO register.

The algorithm specifies that all possible AND terms are created white cell and all possible NAND terms are created gray cell. The white cell consists of full adder

# R

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 16 June 2018

and AND gate, but the gray cell consists of full adder and NAND gate.

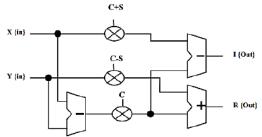

Complex multiplication is consisting of 4 multiplications, 2 adders and 1 subtraction. But in the proposed complex multiplication is consisting of 3 multiplications, 1 adder and 1 subtraction in shown in figure 4.

Figure 3: Flow Chart of Proposed Algorithm

Subtractor: Subtractor is consist of half subtractor and full subtractor depends on word length in proposed algorithm.

Figure 4: Block Diagram of Complex Multiplication

Single-path Delay Feedback Pipeline Architecture:- Herbert L. Groginsky and George A. Works introduced a feedback mechanism in order to minimize the number of delay elements. In the proposed architecture, when the data of input are instantly sent to the butterfly one half of outputs from each stage are fed back to the input data buffer.

Figure 5: Flow Graph of the Radix-2 SDF Pipeline Architecture

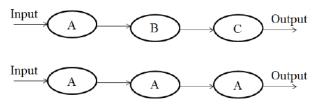

Folding Architecture: Folding is a transformation technique which is utilizing in DSP architecture, implementation for reducing the number of functional blocks in synthesizing DSP architecture. In 1992, Folding was first implemented by Keshab K. Parhi and his students.

Figure 6: (a) Without folding technique (b) With folding technique

**IV.RESULTS**

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 16 June 2018

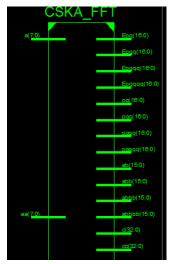

Fig 7: RTL Schematic Diagram

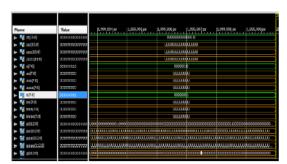

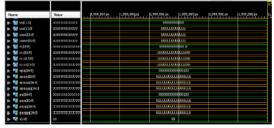

Fig.8 Input Waveform Of FFT

Fig 9: Output Waveform Of FFT

# **V. CONCLUSION**

This paper has reported two efficient VLSI architectures of DIT-FFT. Both proposed architectures are designed for complex inputs with a data width of 16 bits, maintained constant all along. The proposed simulation outputs of architectures have not shown much deviation from numerical values. But, proposed architecture utilizing Radix-2 algorithm has high memory usage and also has huge number of arithmetic operations which causes the delay to be maximum as the signal length increases; this drawback has been overcome in the later VLSI architecture using Radix FFT Algorithm. This research work involved the implementation of a low delay and area efficient pipelined FFT processor using radix-2 algorithm.

#### VI. REFERENCES

[1] Charles. Roth Jr., "Digital Systems Design using VHDL", Thomson Brooks/Cole, 7th reprint, 2005.

[2] S. S. Kerur, Prakash Narchi, Jayashree C N, Harish M Kittur and Girish V A, "Implementation of Vedic multiplier for Digital Signal Processing", International Conference on VLSI, Communication & Instrumentation (ICVCI) 2011, Proceedings published by International Joural of Computer Applications® (IJCA), pp.1-6.

[3] Himanshu Thapaliyal and M.B Srinivas, "VLSI Implementation of RSA Encryption System Using Ancient Indian Vedic Mathematics", Center for VLSI and Embedded System Technologies, International Institute of Information Technology Hyderabad, India.

[4] Charles. Roth Jr., "Digital Systems Design using VHDL", Thomson Brooks/Cole, 7th reprint, 2005.

[5] S. S. Kerur, Prakash Narchi, Jayashree C N, Harish M Kittur and Girish V A, "Implementation of Vedic multiplier for Digital Signal Processing", International Conference on VLSI, Communication & Instrumentation (ICVCI) 2011, Proceedings published by International Joural of Computer Applications® (IJCA), pp.1-6.

[6] Himanshu Thapaliyal and M.B Srinivas,"VLSI Implementation of RSA EncryptionSystem Using Ancient Indian Vedic

# R Inte

# **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 16 June 2018

Mathematics", Center for VLSI and Embedded System

Technologies, International Institute of Information Technology Hyderabad, India.

- [7] Jagadguru Swami Sri Bharati Krishna Tirthaji Maharaja, "Vedic Mathematics: Sixteen simple Mathematical Formulae from the Veda", Delhi (2011).

- [8] Harpreet Singh Dhillon and Abhijit Mitra, "A Reduced-bit Multiplication Algorithm for Digital Arithmetic", International Journal of Computational and Mathematical Sciences, Febrauary 2008, pp.64-69.

- [9] Charles. Roth Jr., "Digital Systems Design using VHDL", Thomson Brooks/Cole, 7th reprint, 2005.

Available online: <a href="https://edupediapublications.org/journals/index.php/IJR/">https://edupediapublications.org/journals/index.php/IJR/</a>

Page | **1454**