## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 15 May 2018

# Reliable and Error Detection Architectures of Pomaranch for False Alarm Sensitive Cryptographic Applications

Sayed Munwarunnisa,

Mr. K. Raghavendra Rao

M.Tech Student,

**Assistant Professor**

munnawarunnisasayed@gmail.com

raghukommana@gmail.com

Nimra college of engineering and Technology

ABSTRACT: In this paper, reliability and false-alarm sensitivity of sensitive cryptographic applications are benchmarked through a case study, i.e., the uneven substitution box of a stream cipher, to elaborate on the respective effects on smart infrastructures. The proposed architectures are benchmarked in terms of error coverage for different fault models and assessed for false-alarm immunity. Moreover, they have been synthesized on an ASIC platform and it is shown that with an acceptable overhead, high error coverage can be achieved for the proposed architectures. The benchmark details the smart infrastructure implications and elaborates on the fact that using the proposed framework, smart infrastructures can be more efficiently and reliably utilized.

KEY WORDS: False alarm sensitivity, ASIC, AES, Encryption, Decryption.

#### **I.INTRODUCTION**

High level security, adoptable to diverse application, efficient and exportable are the objectives of AES. In this project work, the plain text of 128 bits is given as input to encryption block in which encryption of data is made and the cipher text of 128 bits is throughout as output. The key length of 128 bits is used in process of encryption. The AES algorithm is a block cipher that uses the same binary key both to encrypt and decrypt data blocks is called a symmetric key cipher. To read an encrypted message of AES a good symmetric key algorithm likeAES should exists with no attack better than key exhaustion.

In this paper an iterated block cipher of AES is used with a fixed block size of 128 and a variable key length. Various transformations are operated on the intermediate results which is called as *state*. The state is arectangular array of Bytes and the block size is 128 bits. Basically, it is 16 bytes rectangular array with dimensions 4x4. In the AES algorithm the basic unit for processing is a byte anda sequence of eight bits. These are treated as a single entity. The input, output and Cipher Key bit sequences are processed as arrays of bytes which are formed by dividing the sequences into groups of eight contiguous bits to form arrays of bytes.

Generally the variable block size andthe row size is fixed to four in AES and the number of columns also varies. In the AES the number of columns isdivided by 32 and it is denoted as Nb. Coming to the cipher key, it is pictured as arectangular array with four rows. The number of columns of the cipher key isequal to the key length divided by 32. So AES uses a variable number of rounds, which are fixed that is represented as key of size 128 has 10 rounds.

In the process of Encryption or Cipher, the input data and the input keywere copied to the State array using the conventions. So at first the XOR operation is performed between each byte of the input data and the input key and the output should be given as the input of the Round-1. After the process of an initial Round Key addition, the State array is transformed by implementing a round function 10times. So with the final round it can obtain output from *Nr*—

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 15 May 2018

1rounds. At last the final State is copied to the output. By using round function, the process is parameterized which consists of a one-dimensional array of four-byte words. These are derived by using the Key Expansion routine.

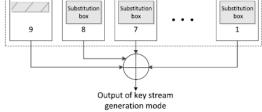

#### II. EXISTED SYSTEM

The structure of a jump register section includes jumpcontrol in (JCi) and out (JCo) signals, which are fed into andout of the section. The substitution box is part of this unitwhich nonlinearly affects the jump control out signal whichis used as an input of the following section. Theaforementioned sections cascaded nine times to contribute to the key stream of the cipher. As observed in this figure, this accumulated cascade jump control in key stream generation mode combines the outputs of the nine sections to reach to the key stream needed.

As part of its key generation process, Pomaranch useseight uneven substitution boxes with a 9-bit input and a 7-bitoutput. Each substitution unit is based on the inverse moduloan irreducible polynomial of degree nine, i.e., x9 + x + 1, whose period is 73. The 9-bit output is then converted intoa 7-bit one with deletion of the most significant and least significant bits of the result. For the hardware implementations of the uneven substitution box of Pomaranch, multiple instances (memories or lookup Tables) are needed. In field-programmable gate array (FPGA) platforms, one needs to use block memories or distributed pipelined memories and in ASIC, memory macros or synthesized logic is needed which are not preferable for high-performance and low-complexity applications. From below figure (1) we can see the block formation of existed system.

# Simplified Jump Register Sections

Fig. 1. Existed system

In general, time and hardware redundancy are two mainmethods for fault diagnosis. Hardware redundancy addshardware to the original structure for diagnosis and timeredundancy repeats the operations two times for detection ftransient faults. Permanent faults through time redundancycan be detected using various methods which are, generally, denoted as recomputation with encoded operands. The fault diagnosis methods alarm the errors in the architectures; however, even if the overhead is acceptable, there could be a chance for false alarms, i.e., detection of faults that do not result in erroneous outputs. Such false alarms could be exploited to induce distrust to the user, i.e., repetitive, false detections result in either ignoring the alarms by theuser or abandoning the devices in which the cryptographicarchitectures are embedded.

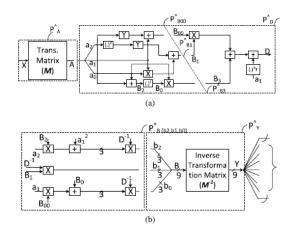

#### III. PROPOSED SYSTEM

In this section, we propose fault detection architectures for the substitution box of Pomaranch considering the vulnerability of such structures to false alarms due to their uneven

# R

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 15 May 2018

architectures. Specifically, we propose a framework that can be tailored based on the available resources and thereliability objectives to achieve.

Fault diagnosis approaches are providedfor the architectures presented. Multiterm signatures are devised and presented as a fault diagnosis frameworkthat can be used depending on the requirements in smartinfrastructures in terms of reliability. We carefully pinpoint thefalse-alarm vulnerability of such approaches and modifications needed to counteract such instances are presented. These arebenchmarked in detail in terms of error coverage and efficiency in the following sections.

We first present two theorems that are used in deriving the signatures needed for our fault diagnosis approaches. Based on the structures in multiplications in composite fields are used frequently to perform operations in the subfield GF(23). Moreover, observing thearchitecture of inversion in GF(23) is shown which is used in each substitution box iteration. Accordingly, the following two theorems are presented to derive the predicted parities of these two important operations in the subfield GF(23). From below figure (2) we can observe the block formation of proposed system.

Fig. 2. Proposed system

## IV. RESULTS Register Transfer level

### Technology schematic

#### Output

# R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 15 May 2018

#### IV. RESULTSV. CONCLUSION

In this paper, reliability and false-alarm sensitivity of sensitive cryptographic applications are benchmarked through case study, i.e., the uneven substitution box of a streamcipher, to elaborate on the respective effects on smartinfrastructures. We have presented low-power architectures for this stream cipher and then proposed a framework toprovide fault immunity for infrastructures that need to dealwith sensitive information and are smart and ubiquitous. The proposed architectures are benchmarked in terms of error coverage for different fault models and assessed for false-alarm immunity. Moreover, they have been synthesized on an ASIC platform and it is shown that with an acceptable overhead, high error coverage can be achieved for the proposed architectures. Furthermore, we have assessed the benefits and effects of such architectures for smart infrastructures. The benchmark details the smart infrastructure implications and elaborates on the fact that using the proposed framework, smart infrastructures can be more efficiently and reliably utilized.

#### VI. EFERENCES

- [1] K. Fu and J. Blum, "Controlling for cybersecurity risks of medicaldevice software," *Commun. ACM*, vol. 56, no. 10, pp. 35–37, Oct. 2013.

- [2] D. Halperin, T. Kohno, T. S. Heydt-Benjamin, K. Fu, and W. H. Maisel, "Security and privacy for implantable medical devices," *IEEE PervasiveComput.*, vol. 7, no. 1, pp. 30–39, Jan./Mar. 2008.

- [3] M. Rostami, W. Burleson, A. Jules, and F. Koushanfar, "Balancingsecurity and utility in medical devices?" in *Proc. 50th ACM/EDAC/IEEEInt. Conf. Design Autom.*, May/Jun. 2013, pp. 1–6.

- [4] M. Zhang, A. Raghunathan, and N. K. Jha, "Trustworthiness of medicaldevices and body area networks," *Proc. IEEE*, vol. 102, no. 8,pp. 1174–1188, Aug. 2014.

- [5] H. Khurana, M. Hadley, N. Lu, and D. A. Frincke, "Smart-grid securityissues," *IEEE Security Privacy*, vol. 8, no. 1, pp. 81–85, Jan./Feb. 2010.

- [6] M. Mozaffari-Kermani, M. Zhang, A. Raghunathan, and N. K. Jha, "Emerging frontiers in embedded security," in *Proc. 26th Int. Conf. VLSIDesign*, Jan. 2013, pp. 203–208.

- [7] R. Roman, P. Najera, and J. Lopez, "Securing the Internet of things," *Computer*, vol. 44, no. 9, pp. 51–58, Sep. 2011.

- [8] T. H.-J. Kim, L. Bauer, J. Newsome, A. Perrig, and J. Walker, "Challenges in access right assignment for secure home networks," in *Proc. USENIX Conf. Hot Topics Secur.*, 2010, pp. 1–6.