# International Journal of Research Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 19 August 2018

# A Modular Multilevel DC/DC Converter with Fault Blocking Capability for HVDC Interconnects

#### **VEMAGIRI RAJESH & Mr. P.VICTOR BABU**

B.Tech (EEE), Department of Electronics and Electrical Engineering, Helapuri Institute of Technology and Science, Eluru, A.P.

Assistant Professor, Department of Electronics and Electrical Engineering,

Helapuri Institute of Technology and Science, Eluru, A.P.

ABSTRACT-A modular multilevel dc/dc converter, termed the DC-MMC, that can be deployed to interconnect HVDC networks of different or similar voltage levels is introduced in this paper. Its key features include: 1) bidirectional power flow; 2) step-up and step-down operation; and 3) bidirectional fault blocking similar to a dc circuit breaker. The kernel of the DC-MMC is a new class of bidirectional single-stage dc/dc converters utilizing interleaved strings of cascaded sub modules. The DC-MMC operation is analyzed and an open loop voltage control strategy that ensures power balance of each sub module capacitor via circulating ac currents is proposed. Here, we are using the Ann controller. Artificial neuron is supposed to mimic the action of a biological neuron, i.e., to accept many different signals, xi, from many neighboring neurons and to process them in a pre-defined simple way. The goal of the neural network is to solve problems in the same way that the human brain would, although several neural networks are much more abstract. Modern neural network projects typically work with a few thousand to a few million neural units and millions of connections, which is still several orders of magnitude less complex than the human brain and closer to the computing power of a worm. Simulations performed the DC-MMC's principle of operation and the proposed control strategy. By using the simulation results we can analyze the single-stage dc/dc conversion process for both step-down and step-up operating modes.

Available online: <a href="https://edupediapublications.org/journals/index.php/IJR/">https://edupediapublications.org/journals/index.php/IJR/</a>

# R

### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 19 August 2018

Index Terms—Converters, ANN, dc-dc power conversion, HVDC converters, multilevel systems.

#### I. INTRODUCTION

The dc/ac standard structure convertor (MMC) has gained widespread quality because of its several operational benefits for top voltage and high power applications. DC transmission is chop-chop turning into a most popular alternative for the largescale integration of renewable energy sources. a replacement category of standard construction bidirectional dc/dc converters supported the MMC thought have recently been proposed. These converters, termed the DC-MMC, are able to accomplish single-stage dc/dc conversion using series cascaded SMs. Most notably, its potential advantages for grid affiliation of offshore wind farms are well known. due to this dynamic electrical landscape, the development of dc grids for the gathering and distribution of energy from renewable sources is gaining traction. This paper proposes a standard multilevel dc/dc converter, termed the DC-MMC, that has the potential to interconnect HVDC networks of either totally different or similar voltage levels whereas at the same time giving the promise of bidirectional fault block. The DC-MMC uses multiple interleaved strings of cascaded SMs to perform single-stage bidirectional dc/dc conversion, and is capable of each reduction and increase operation. Elimination of the standard intermediate ac link is achieved by exploiting current ac currents to take care of power balance of every SM capacitance. the utilization of 2 cascaded dc/ac stages is expensive and hinders overall conversion potency whereas electrical device less dc/dc converters ar usually not absolutely standard and might suffer from uncontrolled propagation of fault currents [26] because of external dc faults. Due to its standard structure and lots of operational benefits, the well-known modular multilevel convertor (MMC) has become a most popular resolution for dc/ac conversion in varied power grid applications. The MMC is especially engaging to be used in HVDC transmission wherever its ascendable design permits massive operative voltages to be realised by merely stacking the requisite variety of sub modules (SMs) in cascade. However, the most disadvantage

₹®

**International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X

Volume 05 Issue 19 August 2018

of MMC-based dc/dc topologies is that they need 2 cascaded dc/ac conversion stages. this can be a

comparatively expensive answer as every dc/ac stage should method an equivalent input power, leading

to poor utilization of total put in SM rating. Moreover, the inherent would like for AN intermediate ac

link and electrical device rated for the complete input power more adversely impacts the full value

similarly as overall conversion potency.

II. PROPOSED DC-MMC FOR HVDC INTERCONNECTS

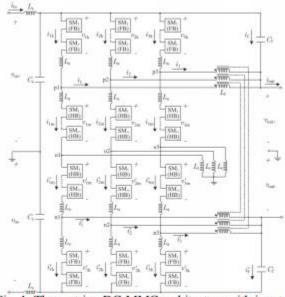

A. Three-String Architecture

The DC-MMC performs single-stage dc/dc conversion by utilizing interleaved strings of cascaded SMs.

Fig. 1(a) shows the three-string architecture of the DC-MMC for deployment in bipolar HVDC networks.

Each string is comprised of two pairs of arms; each pair of arms consisting of an inner arm and an outer

arm, where an arm is defined as a set of cascaded SMs.

The arms of each string are series-stacked in symmetric relation about an associated midpoint, i.e., o1,

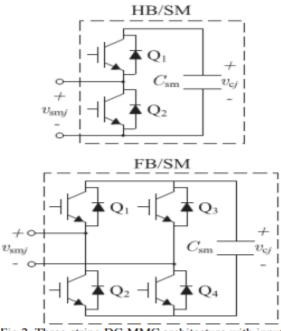

o2, o3, with the inner arms flanked by the outer arms. Each inner arm and outer arm employs m half-

bridge SMs (HB/SMs) and k full-bridge SMs (FB/SMs), respectively. Circuit configurations for the HB/SM

and FB/SM switching cells are given in Fig. 1(b).

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 19 August 2018

Fig. 1. Three-string DC-MMC architecture with input and output filtering: (a) circuit diagram

Fig.2. Three-string DC-MMC architecture with input and output filtering: (b) switching cell configurations for j th half-bridge SM (HB/SM) and jth full-bridge SM (FB/SM).

# ₹®

### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 19

August 2018

In comparison to the three-phase dc/ac MMC, the three-string architecture in Fig. 1 shares a similar modular structure. As will become more apparent in subsequent sections, the three-string implementation of the proposed DC-MMC may be viewed as the three-phase dc/ac MMC structure adapted for single-stage dc/dc conversion. Unlike the recently proposed dc/dc converter, which is formed by series-stacking two conventional three-phase dc/ac MMCs, the operation and control of Fig. 1 is fundamentally different from that of the dc/ac MMC.

**B. Two-String Architecture**

The DC-MMC in Fig. 1 utilizes three interleaved strings of cascaded SMs. By removing one of the strings, a two-string implementation is also possible as shown in Fig. 2. This architecture is the simplest multi string implementation of the DC-MMC. In general, an arbitrary number of strings can be interleaved. Note the ability to install a coupled inductor set at each dc output pole has been exploited due to the even number of interleaved strings. Consequently, this reduces insulation requirements on the output filter inductances as compared to Fig. 1. The two-string and three-string architectures have the same fundamental principle of operation as each string employs an identical dc/dc conversion process. For equal string designs, the two-string has 2/3 the output power rating of the three-string.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 19 August 2018

Fig. 3. Two-string DC-MMC architecture with input and output filtering.

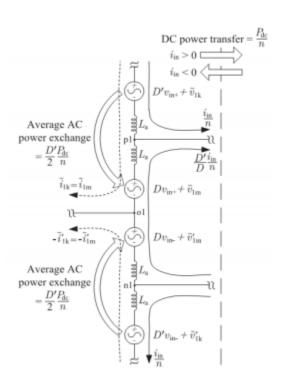

#### C. Principle of Operation

In Figs. 1 and 2, the input network voltages vin+ and vin – can be unevenly split between the arms of each string. For example, arm voltages v1k (outer arm) and v1m (inner arm) can have unequal dc components that sum to vin+ . The same applies to v1m (inner arm) and v1k (outer arm) with vin –. Division of vin+ and vin – as described is achieved by controlling the number and polarity of SM capacitors inserted along each string via switching action, where possible switching states for the jth HB/SM and FB/SM are vsmj =  $\{0, +vcj\}$  and vsmj =  $\{0, -vcj, +vcj\}$ , respectively. The output network, represented by vout+ and vout –, is coupled across the inner arms of each string as shown. DC power transfer between networks can be reversed by changing polarity of iin. Bidirectional dc power transfer is easily accommodated as the SMs inherently permit bidirectional current flow. The arrangement of HB/SMs and FB/SMs in Figs. 1 and 2 permits both step-up and step-down voltage level conversion for the DC-MMC. the operating modes of the DCMMC are summarized: 1) step-down operation: 0 < D < 1 and thus 0 < D < 1; 2) step-up operation: D > 1 and thus D < 0. For step-down operation where the

Available online: <a href="https://edupediapublications.org/journals/index.php/IJR/">https://edupediapublications.org/journals/index.php/IJR/</a>

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X

Volume 05 Issue 19 August 2018

voltages at nodes p1, p2,p3 (and n1, n2, n3) relative to ground always remain below vin+ (and above

-vin -), By using circulating ac currents to ensure power balance for each SM capacitor the DC-MMC in

Figs. 1 and 2 is able to perform single stage dc/dc conversion. The circulating currents are established by

reactive elements and serve to exchange average ac power between each outer arm and the adjacent

inner arm, in a near lossless manner. Average ac power exchange between arms (Pac ) for SM capacitor

charge balancing is indicated by the bold arrows. link the string midpoints using capacitors, however,

this is done at the expense of highimpedance grounding the DC-MMC structure. Based on the above

discussion, the principle of operation of the two-string DC-MMC architecture is conceptualized in Fig. 3.

III. ANALYSIS OF DC-MMC OPERATION

Based on the analysis, a modulation scheme for the ac arms voltages that satisfies SM capacitor power

balance for all possible operating modes is proposed. The DC-MMC operation in greater depth, by

utilizing a simplified string model to study the otherwise indicated, the following assumptions are

enforced: 1) each arm has a large number of SMs such that ideal sinusoidal ac voltages are synthesized;

2) ac voltages and currents are represented by their steady-state fundamental frequency components;

3) resistance terms are neglected; and 4) ac output filter currents are negligible.

A. Single-Stage DC/DC Conversion Process

This design flexibility is a salient feature of the DC-MMC. Depending on the specific application, a

suitable modulating frequency would be selected based on a tradeoff between design constraints such

as SM capacitor voltage ripple, total energy storage cost, and switching losses. To illustrate the ideal

single-stage dc/dc conversion process, provides a simplified model for string #1 of the DCMMC.

**B. Steady-State Power Balance of SM Capacitors**

There are infinitely many combinations of ac arms voltages and resulting ac arms currents that can

satisfy power balance constraints. The peak magnitude of the ac arms voltages is denoted by V<sup>ˆ</sup>. Φ is

the phase shift between ac voltages of each outer arm and the adjacent inner arm, with positive values

of  $\Phi$  defined for the inner arm voltage leading the outer arm voltage. However, adopting such a strategy

Available online: <a href="https://edupediapublications.org/journals/index.php/IJR/">https://edupediapublications.org/journals/index.php/IJR/</a>

Page | **503**

®

**International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X

Volume 05 Issue 19 August 2018

constrains each pair of arms to equally share the reactive power requirements of the composite load

formed by Lr and La.

C.BIDIRECTIONAL DC FAULT BLOCKING CAPABILITY

In addition to enabling step-up operation and the interconnection of HVDC networks with similar

voltage levels, the FB/SMs in Figs. 1 and 2 can provide bidirectional fault blocking. That is, the DCMMC

can interrupt fault currents initiated by dc faults in either the input or output side networks similar to a

dc circuit breaker. This is accomplished by controlling the FB/SMs in Figs. 1 and 2 to impose the

appropriate polarity of voltage.

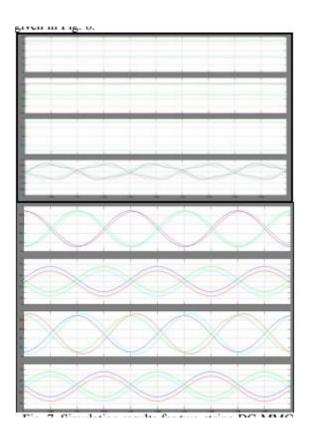

**SIMULATION RESULTS**

1) Step-Down Operation: Simulation results for D = 0.5 with dc power transfer from input to output are

given in Fig. 4.

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 19 August 2018

Fig. 4. Simulation results for two-string DC-MMC

**2) Step-Up Operation**: Simulation results for D = 1.1 are provided in Fig. 5 The input voltage of  $\pm 8.8$  kV is now stepped up to  $\pm 9.68$  kV. This scenario is chosen to demonstrate the DC MMC's ability to interconnect dc networks of similar voltages by exploiting FB/SMs in the outer arms.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 19 August 2018

Fig. 5. Simulation results for two-string DC-MMC Step-Up Operation

#### **CONCLUSION**

The DC-MMC is a new class of modular multilevel dc/dc converters well suited for HVDC system using ANN is proposed in this paper. This paper presents the first dynamic model for the DCMMC. The proposed state-space model is validated by comparing with simulation results for a comprehensive switched model. A new modular multilevel dc/dc converter, termed the DC MMC, is presented for the interconnection of bipolar HVDC networks. The main advantages of using Artificial Neural Networks (ANN) include: it can handle large amount of data sets; it has the ability to implicitly detect complex nonlinear relationships between dependent and independent variables; it has ability to detect all possible interactions between predictor variables; etc. The proposed state-space model is validated by comparing with simulation results for a comprehensive switched model. The DC-MMC features a new class of bidirectional single-stage dc/dc converters utilizing interleaved strings of cascaded SMs. By employing a unique arrangement of HB/SMs and FB/SMs for each string, the DC MMC can provide both step-up and step-down operations and interconnect HVDC networks of similar voltage levels. To ensure capacitor voltages are regulated to their nominal values the DC-MMC needs some form of regulation for the ac average power exchange between converter arms. This regulation is achieved via closed loop control of the internally circulating ac currents. A simplified model of the converter strings is presented and the ideal dc/dc conversion process is analyzed in this paper. An open loop voltage control scheme is proposed for the single string and two-string architectures that adopts closed-loop ac current control to maintain power balance of the SM capacitors. To ensure capacitor voltages are regulated to their nominal values the DC-MMC needs some form of regulation for the ac average power exchange between converter arms. To compensate for load and parameter imbalances the simulation results validate the proposed method. The proposed scheme has the benefits of minimizing the circulating ac currents needed for the dc/dc conversion process while significantly reducing the installed circuit reactance.

#### **REFERENCES**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 19 August 2018

[1] R. Majumder, C. Bartzsch, P. Kohnstam, E. Fullerton, A. Finn, and W. Galli, "Magic bus: Highvoltage DC on the new power transmission highway," IEEE Power Energy Mag., vol. 10, no. 6, pp. 39–49, Nov. 2012.

[2] W. Chen, A.Q. Huang, C. Li, G. Wang, and W. Gu, "Analysis and comparison of medium voltage high power DC/DC converters for offshore wind energy systems," IEEE Trans. Power Electron., vol. 28, no. 4, pp. 2014–2023, Apr. 2013.

[3] F. Deng and Z. Chen, "Control of improved fullbridge three-level DC/DC converter for wind turbines in a DC grid," IEEE Trans. Power Electron., vol. 28, no. 1, pp. 314–324, Jan. 2013.

[4] J. W. Bialek, "European offshore power grid demonstration projects," in Proc. IEEE Power Energy Soc. General Meet., Jul. 2012, pp. 1–6.

[5] D. Das, J. Pan, and S. Bala, "HVDC light for large offshore wind farm integration," in IEEE Power Electron. Mach. Wind Appl., Jul. 2012, pp. 1–7. 2010.

[6] J. Robinson, D. Jovcic, and G. Joos, "Analysis and design of an offshore wind farm using a MV DC grid," IEEE Trans. Power Del., vol. 25, no. 4, pp. 2164–2173, Oct. 2010.

[7] C. Meyer, M. Hoing, A. Peterson, and R. W. De Doncker, "Control and design of DC grids for offshore wind farms," IEEE Trans. Ind. Appl., vol. 43, no. 6, pp. 1475–1482, Nov./Dec. 2007.

[8] S. S. Gjerde and T. M. Undeland, "Control of direct driven offshore wind turbines in a DCcollection grid within the wind farms," in IEEE Trondheim PowerTech, Jun. 2011, pp. 1–7.

[9] A. Orths, A. Hiorns, R. Van Houtert, L. Fisher, and C. Fourment, "The European north seas countries' offshore grid initiative—The way forward," in IEEE Power Energy Soc. General Meet., Jul. 2012, pp. 1–8.