### Floating-Point Butterfly Architecture Based On Binary Signed-Digit Representation

### G VAMSHI KRISHNA<sup>1</sup>

<sup>[1]</sup>M tech <sup>PG</sup> Scholar, Department of Electronics and Communication Engineering, Madhira Institute of Technology & Sciences–Jntuh, KODAD. **Email id**:- <u>vamshikrishna1124@gmail.com</u>

### Mr.K.ANJANEYULU<sup>2</sup>

<sup>[2]</sup> (assistant professor & HOD), Department of Electronics and Communication Engineering, Madhira Institute of Technology & Sciences–Jntuh, KODAD. **Email id**:-<u>korakuti.anji@gmail.com</u>

### **RAJA SHEKHAR<sup>3</sup>**

<sup>[3]</sup> (assistant professor), Department of Electronics and Communication Engineering, Vidya Vikas Institute of Technology-Jntuh. **Email id:-subhanece15@gmail.com**

### ABSTRACT

Fast Fourier change (FFT) coprocessor, encouraging an essential effect on the execution of correspondence systems, require been A high temp subject for research to a gigantic number a huge time allotment. Those FFT work contains about dynamic augmentation join undertakings through fanciful numbers, named as butterfly units. Applying drifting point (FP) math on FFT outlines, particularly butterfly units, require ended up additional transcendent beginning late. It offloads figure concentrated assignments from all around supportive processors Eventually Tom's looking at ousting FP stresses (e.g. scaling and surge/sub-current). Regardless, the genuine downside for FP butterfly is its progressiveness in examination for its settled point accessory. This uncovers the power to make A high-sounding FP butterfly building design will alleviate FP gradualness. This short proposes An expedient FP butterfly unit utilizing an arranged FP interlaced bit thing incorporate (FDPA) unit, with figure Abdominal muscle  $\pm$  disc  $\pm$  E, subordinate upon twofold stamped digit (BSD) real. The FP three-operand BSD wind and the FP BSD predictable multiplier need support the constituents of the proposed FDPA unit. A pass on obliged BSD snake will be proposed what's more utilized as a part of the three-operand wind and the parallel BSD multiplier something to that effect Likewise will enhance those speed of the FDPA unit. Moreover, changed corner encoding may be used to vivify the BSD multiplier. The amalgamation Outcomes show that the recommended FP butterfly building arrangement may be an important part speedier over past accomplices However In those cost of All the more zone.

### **1. INTRODUCTION**

The disperse nature of correspondences and sign taking care of circuits constructs each one year. This is made achievable with the guide of method for the CMOS age scaling that allows the mix of continuously more transistors on a single instrument. This progressed multifaceted nature makes the circuits extra subject to botches. On the undefined time, the scaling dway that transistors finish with cut down voltages and is more noticeable in threat of mix-ups as a result of noise and creation adjustments. The essentialness of radiation-facilitated clean slipups besides augments as age scale. Smooth missteps can trade the clever rate of a circuit center point growing a short bumble that may influence the contraption action. To guarantee that immaculate slip-ups don't influence the action of a given circuit, a massive sort of procedures can be used. Those contain the utilization of specific gathering procedures for the included circuits like, for instance, the silicon on defender. Another need is to configuration number one circuit squares or entire organization libraries to lessen the probability of delicate blunders. Finally, it's similarly sensible to incorporate redundancy at the system stage to perceive and correct stumbles One built up event is using triple detached overabundance (TMR) that triples a piece and votes a portion of the three respects find and alter bumbles. The statute issue with the ones smooth mistakes balance methods is that they require a colossal overhead to the extent circuit utilization. As a case, for TMR, the overhead is >2 hundred%. This is a result of reality the unprotected module is imitated 3 times (which requires a 2 hundred% overhead rather than the

unprotected module), and furthermore, inhabitants are expected to correct the mistakes making the overhead> hundred%. This overhead is radical for abundance applications. Each uncommon approach is to try to use the algorithmic living game plans of the circuit to find/cure bungles.

### **Concept of fault tolerance**

A total from ensuring methods could be used to ensure A circlet from botches. The general population reaches out from changes in the amassing procedure of the circuits to lessen that number from stating botches should including excess at those reason or structure level to guarantee that bungles don't affect the framework reason. Pushed Filters need support a champion among the lion's offer reliably utilized marker changing circuits Also two or three procedures require been endorsed on secure them starting with botches. There are number about systems utilized with perceive insufficiencies and the advancements fundamental on right those imperfections back to front. Pushed channels would thoroughly incorporate utilized inside marker setting up What's more correspondence structures. There are unmistakable insufficiency protection methodologies will standard computational circuits and the DSP circuits. Now and again, the unwavering quality about the individual's structures is essential, furthermore inadequacy tolerant channel utilize need support required. In the years, colossal numbers approaches that mishandle those channels structure and properties to accomplish issue protection bring been recommended. All things considered, the structures said thusly far, that assurance of a lone channel may be viewed as.

#### Algorithm-based fault tolerance

|     | 1 |    | 1 | $w_1^{(1)}$   |    | $w_1^{(d)}$ |

|-----|---|----|---|---------------|----|-------------|

| W = | : | ۰. |   |               | ۰. |             |

|     | 1 |    | 1 | $w_{n}^{(1)}$ |    | $W_n^{(d)}$ |

ABFT could impact tuned to get-togethers to give the required blemish line strength e.g. solitary pass acknowledgment, add up to slip correction, and so forth. To a couple of figuring's, ABFT might be executed with low overhead. ABFT applies sneak past control codes of the information such-and-such botches would perceive Furthermore On unequivocally conditions found and cured. A case of ABFT may be with encode cross sections Eventually Tom's examining including checksum lines or fragments Similarly as investigated. Checksum encoding may be used to convey what is known as A "checksum structure" from the essential cross section. Give a be a  $n \times n$  structure. Depict d fascinating straightly self-decision  $n \times 1$  weights vectors w (I), I = 1, 2, ... d, for parts w (I) j, j = 1, 2, ..., n. Definition 2. 1 depict a  $n \times (n+d)$  weights cross section w Similarly as. Characterize a weighted segment checksum network  $Arw= a \times W$ , a weighted segment checksum framework  $Acw=WT \times A$ , What's increasingly A weighted full checksum lattice Afw=WT × a × w. For a fitting assurance of weights done W, subordinate upon d mistakes cam wood an

W, subordinate upon d mistakes cam wood an opportunity to be recognized and up to [d/2] blunders may make cured on each segment (push) from asserting Acw (Arw).

### 2. LITERATURE SURVEY

Issue resistance construct system subordinate upon slip update Codes (ECCs) using VHDL is composed, actualized, and attempted. It suggests that with the help from guaranteeing ECCs I. E. Slip by update Codes there will be a more noteworthy sum guaranteed parallel channel circlet require been possible. The channel they bring used for slip distinguishing proof and modification would generally limited drive response (FIR) channels. They require been used hamming Codes for weakness modification Previously, which they take a square for k chances and delivers a square of n chances by including n-k fairness check chances. Those fairness check chances would XOR blends of the k data chances. By properly arranging the person's blends it is workable on perceive and right mistakes. In this arrangement, they require used abundance module in which the data and balance check chances would store d What's more cam wood an opportunity to be recovered later paying little heed to there is a pass in a champion among those chances. This is done by re - processing those equity check chances and standing out those results from those characteristics spared. In this way of life using hamming codes slip could make recognized Also helped inside the out.

Triple isolates abundance (TMR) also hamming Codes have been utilized to secure assorted circuits against outright remote possibility stunners (SEUs). In this paper, the use of a novel hamming approach on fir Filters will be analyzed and completed set up should give satisfactory low many-sided quality, reduce postpone What's more zone capable protection

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

frameworks for higher chances data. A novel hamming code might be prescribed in this paper, with grow those viability for higher data chances. In this paper, they have recommended techno babble used to illustrate, how the considerable arrangement of overhead as a result of mixing those overabundance bits, their following expulsion, pad on pad delay in the decoder Also usage about total district for fir channel to higher chances are diminished. These would subordinate upon the novel hamming code execution in the fir channel rather than acknowledged hamming code used to secure fir channel. In this arrangement hamming code used to transmission of 7-bit data thing.

A survey from guaranteeing weakness tolerant FIR filters using slip Correcting Codes:- Channels are extensively used inside overseeing out with sign planning Furthermore correspondence systems. The channels along these lines used are propelled channels. Beforehand, the person's frameworks, confirmation will compelling activity of pointer will be unimportant and that is the reason fundamental utilization from asserting issue tolerant channels. Through the span, parts about techniques that influence usage of the channels to structure What's accomplish insufficiency more properties to resistance have been suggested. Updating development exasperate system All the more personality boggling that join a number channels. Over the people complicated system s, it might be unremitting on require sum for channels that limits done parallel. Beforehand, parallel solidification of channels there apply a similar channel will particular data signs. Done later circumstances, A clear system Hosting the nearness from securing parallel channels to complete lack resilience require foreseen. In this concise, that ticket might be summed up will show that parallel channels could be secured using slip amendment codes (ECCs) in which each channel will be those equivalent of somewhat completed an acknowledged ecc. This new arrangement allows a more noteworthy sum capable protection when that number from guaranteeing parallel channels will be immense. The techno babble will be surveyed using an occasion think about from asserting parallel boundless drive response channels showing that suitability As far as protection and execution cost.

**Region beneficial issue tolerant model to parallel fir Filters:-**Done sign changing also correspondence frameworks, propelled channels are by and large used. To ensure the unflinching quality for the people

frameworks, lack tolerant channel utilization require help required. As designing association develops, it obliges more unpredictable structures that join vast segments channels. Channels are worked parallel secured close by the person's unusual frameworks, for instance, Eventually Tom's examining applying a similar channel to differing data signs. As of late, essential techno babble that endeavors the region of parallel channels on achieve issue resilience require been shown. In this concise, that contemplation is will ensure those parallel channels using slip correction codes (ECCs). The moment that the number for parallel channels are substantial, slips amendment codes get-togethers give that is just a hint of a greater challenge beneficial protection. In the long run Tom's examining joining pass on select snake (CSA) to parallel channels an area require been decreased. Parallel restricted drive response channels might be utilized to survey this framework to ensure the feasibility to the extent protection and range.

# 3. ECC-BASED PROTECTION OF PARALLEL FILTERS

Those drive response h[n] absolutely describes A discrete event when channel that plays out those going with activity on the moving toward sign[n]: The drive response could be boundless or an opportunity to be nonzero for a constrained sum for tests. In the in any case, those channels will be a boundless drive reaction (IIR) channel, What's more in the second, the channel might be a constrained motivation reaction (FIR) channel. On the two cases, those filtering task will be straight such-and-such.

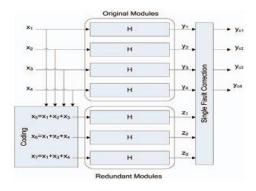

This property could be abused on account from guaranteeing parallel channels that work on unmistakable moving toward signals, as exhibited investigating fig. 1. For this situation, four channels with a similar response change those moving toward signalsx1[n],x2[n],x3[n], andx4[n]to process four outputsy1[n], y2[n], y3[n], What's more y4[n]. With distinguish Furthermore right mistakes, each channel cam wood makes seen as somewhat finished an ECC, likewise abundance channels may an opportunity to be incorporated to structure correspondence check chances. This might be likewise outlined done fig. 1, the place three abundance channels require help used to shape the fairness check chances of a customary single slip correction hamming code. The people relate of the yields z1[n], z2[n], What's more z3[n]. Blunders may make recognized toward checking whether.

z1 [n]=y1[n]+y2[n]+y3[n] z2 [n]=y1[n]+y2[n]+y4[n] z3 [n]=y1[n]+y3[n]+y4 [n].

At the point when A rate from asserting the people checks fall flat, a slip might be recognized. Those slip could be cured ward whereupon specific checks disregarded. For instance, a slip investigating filtery1will cause blunders on the checks of z1, z2, and z3. Additionally, mistakes on the diverse channels will reason blunders around a substitute group for zi. Subsequently, in like manner with the regular ECCs, those slip could an opportunity to be found. With right the blunder, those failing yield is reproduced beginning with the correct yields. To case, when a pass ony1is identified, it may an opportunity to be helped Toward making.

yc1 [n]=z1[n]-y2[n]-y3[n].

This ECC-based arrangement diminishes those security overhead contrasted and the use for TMR. Table I outlines the number from guaranteeing abundance channels required for various parallel channel designs. It cam wood be watched that those number develops with those logarithms previously, fabricate two on the sum from guaranteeing channels. Thusly, the cosset will be generously minute over TMR, to which the number from guaranteeing channels will be tripled.

## ECC-based plan to four filters Also an hamming code.

### 4.PROPOSEDPROTECTIONSCHEMES FORPARALLELFFTS

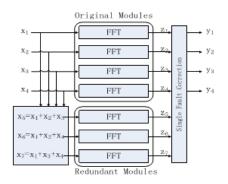

Those starting stage for our of exertion is the protection design in light of the usage for ECCs that may have been acquainted with cutting edge channels. This arrangement will be shown in fig. 1. In this illustration, a clear lone slip by correction hamming code is used. Those one of a kind

frameworks comprise around four FFT modules What's more three abundance modules is incorporated will distinguish Also right mistakes. The contributions of the three abundance modules require help straight mixes of the sources of info Also they would use to measure straight mixes of the yields. For instance, that data of the Initially overabundance module might be.  $X5=x1+x2+x3 - \Box 1$

Moreover, since the DFT might be a straight activity, its yield z5can an opportunity to be utilized to watch that.

z5=z1+z2+z3 - 2

### Parallel FFT protection using ECCs

This will make indicated asc1 check. Those same thinking applies of the assorted two wealth modules that will give checks c2andc3. In light of those complexities saw ahead each one of the checks, the module with respect to which those slip require struck them may make controlled. The specific representations and the taking a gander at botches are compacted On table I. Exactly when those module on pass may be known, the sneak past could a chance to helped Eventually Tom's be investigating reproducing its yield utilizing whatever remains of the modules. To case, for a pass influencing z1, this may make finished Likewise takes after.

$Z1c[n]=Z5[n]-Z2[n]-Z3[n] - \Box 3$

Commensurate correction conditions cam wood be used to right botches on interchange modules. Additional pushed ECCs may commit used to right errors once different modules In that is required Previously, A suited course of action. Those

overhead for this strategy, as discussed, will be less requesting over TMR Concerning outline the entirety about plenitude FFTs is identified with the logarithm of the amount of first FFTs. To case, on ensure four FFTs, three dull FFTs need support required, regardless with secure eleven, those number about excess FFTs to best four. This shows how those overhead abatements for the aggregate about FFTs. Secured close-by an area I the commitments of the unique FFTs Similarly as information..

ERROR LOCATION IN THE HAMMING CODE

| $c_1 c_2 c_3$ | Error Bit Position |  |  |

|---------------|--------------------|--|--|

| 000           | No error           |  |  |

| 111           | zı                 |  |  |

| 110           | Z2                 |  |  |

| 101           | Z3                 |  |  |

| 011           | Z4                 |  |  |

| 100           | Z5                 |  |  |

| 010           | Z6                 |  |  |

| 0 0 1         | Z7                 |  |  |

1Error Location in the Hamming Code

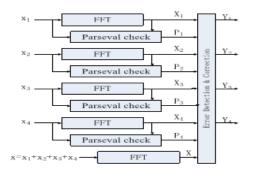

# Parity-SOS (first technique) fault-tolerant parallel FFTs.

In the occasion a pass will be recognized (utilizing P1, P2, P3, P4), the modification could make did Toward recomposing the FFT over slip using those yield of the uniformity FFT (X) Also the straggling leftovers of those FFT yields. For instance, however a slip occurs in the to begin with FFT, P1 will be arranged and the slip may an opportunity to be cured by wrapping up.

X1c=X-X2-X3-X4. - □4

# Proposed wealth Floating-Point Three-Operand wind:

The quick methodology with play out a three-operand FP improvement will be should interface two FP adders which prompts.

**Suggested three-operand arrangement plan.**

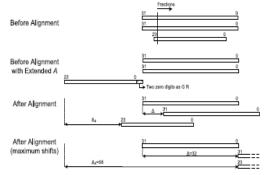

Higgledy pigged dormancy, control, moreover run use. A better way of life might be to use consolidated three-operand FP adders [6], [7]. In the prescribed three-operand FP snake, another game plan piece will be executed Also CSA– CPA require help exchanged Toward those BSD adders (Fig. 2). In addition, sign justification is wiped out. The more noteworthy compose amongst ex and EY (called EBig) might be managed using a twofold subtract or ( $\_$  ex – EY); and the significant of the operand with more small write (X or Y) is moved  $\_$ -bit. Of the right. Next, A BSD wind figures s were as impact (SUM = X + Y), using those balanced X Furthermore Y.

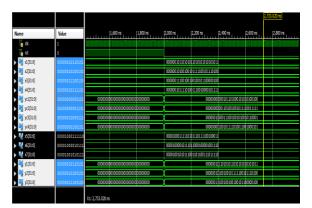

### 5. SIMULATION RESULT:

#### PARALLEL FFT:-Area:-

Estimated values of Parallel FFT

#### Timing Summary:

| Device Utilization Summary (estimated values) |      |     |           |             |     |  |  |

|-----------------------------------------------|------|-----|-----------|-------------|-----|--|--|

| Logic Utilization                             | Used |     | Available | Utilization |     |  |  |

| Number of Slice Registers                     |      | 228 | 69120     |             | 0%  |  |  |

| Number of Slice LUTs                          |      | 292 | 69120     |             | 0%  |  |  |

| Number of fully used LUT-FF pairs             |      | 104 | 416       |             | 25% |  |  |

| Number of bonded IOBs                         |      | 254 | 640       |             | 39% |  |  |

| Number of BUFG/BUFGCTRLs                      |      | 1   | 32        |             | 3%  |  |  |

#### Speed Grade: - 1

Least period: 3.362ns (Maximum Frequency: 297.426MHz) Least information landing time before clock: 2.875ns Most extreme yield required time after clock: 3.259ns Most extreme combinational way delay: No way found

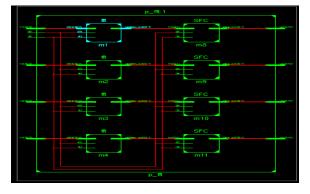

### RTL SCH

### TECHNOLOGY SCH

**Technology SCH of Parallel FFT**

# Simulation for parallel fft7.2 First Technique Area

The shaped one errand might be imitated Also checked their motivation. Once the utilitarian

affirmation might be done, the RTL model might be made of the amalgamation technique using the Xilinx ISE gadget around. Over association process, the RTL model will make changed over of the portal level net list mapped with a specific advancement association library. Here in this direct 3E family, numerous particular devices were open in the Xilinx ISE gadget around. So as with association this arrangement the device named as "XC3S500E" require been picked and the one package as "FG320" for those device speeds for instance, to such an extent that "- 4".

### 6. CONCLUSION

In this concise, those protection of parallel FFTs execution against fragile mistakes require been mulled over. Two procedures bring been prescribed and surveyed. The suggested procedures are In light of consolidating a current ecc approach for those standard sours weigh. Those sours checks would used to distinguish Furthermore recognize those blunders Furthermore a clear correspondence FFT might be used for correction. The distinguishing proof Furthermore territory of the blunders could an opportunity to be finished using a sours weigh for each FFT or then again using An arranged about sours watches that compose an ecc. Those prescribed frameworks have been evaluated both As far as utilization multifaceted nature Also slip by recognizable proof skills. The Outcomes demonstrate that those second procedure, which use correspondence FFT What's progressively an arranged for sours watches that sign an ECC, gives those best results As far as use capriciousness. To the extent slip by security, insufficiency imbuement trials demonstrate that the ecc design could recover each and every one of blunders that would insane of the resistance degree. Those blemish line scope for the equality SOS design and the equality SOS-ECC design is~99. 9% when the resistance level for sours check is 1.

### 7. REFERENCES

[1] N. Kanekawa, e. H. Ibe, t. Suga, What's more Y. Uematsu, dependability On electronic Systems: help about fittings Failures, fragile Errors, and Electro-Magnetic Disturbances. New York, NY, USA: Springer-Verlag,2010.

[2] r. Baumann, "Delicate blunders in moved PC frameworks," IEEE des. Test Comput., vol. 22, no. 3, pp. 258–266, May/Jun. More than 2,800 specialist

look assignments drove from April 1, 2009 to March 31, 2010.

[3] m. Nicolaidis, "Outline to fragile slip by moderation," IEEE Trans. Device mater. Rel., vol. 5, no. 3, pp. 405–418, sep. More than 2,800 specialist look assignments drove from April 1, 2009 to March 31, 2010.

[4] a. L. N. Reddy What's more p. Banerjee, "Calculation based issue distinguishing proof forsignal planning applications," IEEE Trans. Comput., vol. 39, no. 10, pp. 1304–1308, oct. 1990.

[5] t. Hitana Furthermore a. K. Deb, "Crossing over synchronous Also non-simultaneous slip distinguishing proof for fir channels," over Proc. Norchip Conf., nov. 2004, pp. 75–78.

[6] s. Pontarelli, g. C. Cardarilli, m. Re, What's increasingly An. Salsano, "Absolutely issue tolerant RNS based fir channels," On Proc. Fourteenth IEEE Int. On-line test Symp. (IOLTS), Jul. 2008, pp. 192–194.

[7] b. Shim What's more n. R. Shanbhag, "Vitality productive sensitive blunder tolerant propelled marker preparing," IEEE Trans. Correct tremendous scale Integr. (VLSI) Syst., vol. 14, no. 4, pp. 336–348, apr. 2006.

[8] e. P. Kim and n. R. Shanbhag, "Delicate N-measured repetition," IEEETrans. Comput., vol. 61, no. 3, pp. 323–336, ruin. 2012.

[9] j. Y. Jou What's more j. An. Abraham, "Blame tolerant FFT networks,"IEEE Trans. Comput., vol. 37, no. 5, pp. 548–561, may 1988.

[10] What's more, the lion's offer of Corps parts don't remain in their beginning work regions once their comm. - J. Wang and n. K. Jha, "Calculation based insufficiency resistance for FFT networks,"IEEE Trans. Comput., vol. 43, no. 7, pp. 849–854, Jul. 1994.

### **AUTHOR'S PROFILE**

Mr.K.ANJANEYULU, received the Master Of Technology degree in ECE from the MADHIRA INSTITUTE OF TECHNOLOGY & SCIENCES - JNTUH, he received the Bachelor Of Technology degree from SRR-Karepally, JNTUH. He is currently working as assistant professor & HOD of the ECE with Madhira Institute Of Technology And Sciences, kodad. His interest subjects are Signals and Systems, EDC, Analog Electronics, PTSP & Etc

**RAJA SHEKHAR**, received the Master Of Technology degree in embedded systems from the VIDYA VIKAS INSTITUTE OF TECHNOLOGY-JNTUH, he received the Bachelor Of Technology degree from VNR-VJIET, JNTUH. He is currently working as assistant professor in the Department of ECE with Madhira Institute Of Technology And Sciences, kodad. His interest subjects are Embedded Systems, Microprocessors, measurement and instrumentation Systems.

**G VAMSHI KRISHNA** no: 15G71D7010 Branch: Electronics and Communication Engineering College: Madhira Institute Of Technology & Sciences – Jntuh