Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

#### The Reduction of Energy Consumption using Data Encoding Techniques In Network on Chip

<sup>1</sup>V.SANDYADEEPA, <sup>2</sup>V.CHINNA OBULESU

<sup>1</sup>M.Tech Dept of ECE, S.V.I.T. College, Ananthapuramu, Affiliated to JNTUA, AP, India. <sup>2</sup>Assistant Professor, Dept of ECE, S.V.I.T. College, Ananthapuramu, Affiliated to JNTUA, AP, India

Abstract - As technology shrinks, the energy dissipated through the hyperlinks of a network-on-chip (NoC) begins to compete with the power dissipated by means of the opposite factors of the communication subsystem, particularly, the routers and the community interfaces (NIs). On this project, we present a hard and fast of records encoding schemes geared toward reducing the electricity consumption with the aid of the links of a NoC. The proposed schemes are general and obvious with respect to the underlying NoC (i.e., their software does now not require any modification of the routers and link structure). The proposed encoding scheme exploits the wormhole switching strategies and works on a give upto-stop foundation. That is, flits are encoded by way of the Network interface (NI) before they may be injected inside the network and are decoded by means of the destination NI. This makes the scheme transparent to the underlying community for the reason that encoder and decoder logic is included in the NI and no amendment of the routers architecture is needed. We check the proposed encoding scheme on a set of consultant statistics streams (both artificial and extracted from actual applications) displaying that it's far viable to reduce the power contribution of both the self-switching activity and the coupling switching activity in inter-routers links. As consequences, we acquire a reduction in general power consumption and energy intake, with none extensive degradation in phrases of each overall performance.

**Keywords:** Network-On-Chip (NoC), Network Interface (NI), System-On- Chip (SoC)..

#### I. INTRODUCTION

The wide variety of cores integrated right into a system onchip (SoC) will increase, the position played via the interconnection machine turns into more and more important. The international technology Roadmap for Semiconductors depicts the on-chip communication issues as the proscribing factors for overall performance and energy intake in modern day and subsequent era SoCs. Layout within the technology of extremely deep submicron silicon is especially dominated via troubles concerning the

communication infrastructure. Because the design complexity will increase, the full length of the interconnection wires will increase, ensuing in long transmission delay and higher energy intake. Similarly, the gap among wires shrinks with era, increasing coupling capacitance, and the height of the wire fabric will increase resulting in more fringe capacitance even as SoCs consisting of tens of cores were not unusual inside the closing decade, commonplace predictions foresee that the next era of many cores SoC will comprise masses or thousands of cores. in the many center generation, as the number of cores residing on the same SoC will increase appreciably, the verbal exchange solutions additionally want to alternate appreciably that allows you to assist the brand new inter-core communication needs. It's miles now a days broadly identified that Network on-chip (NoC) architectures constitute the maximum feasible option to deal with scalability issues of destiny many-core. structures and to meet performance, energy, and reliability requirements which represent future ambient sensible packages. The significance of interconnects in complex many-core chips has outrun the significance of transistors as a dominant thing of performance, strength, and reliability, device on-chip communication protocols, regarding superior adaptive routing algorithms, choice policies, records protection schemes, mechanisms aimed at making sure the great-of-provider are pushing the interconnect machine to become one of the major elements which characterizes the system in phrases of both strength dissipation and strength

# R

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

consumption. In reality, the blessings over bus-based totally architectures come on the price of growth in complexity which pushes the verbal exchange gadget to become one of the primary factors of a SoC which strongly effect the price, power, and performance of the general system. The fundamental factors which paperwork a NoCprimarily based interconnect are network interfaces (NIs), routers, and hyperlinks. As era shrinks, the strength dissipated by using the links is more relevant as (or extra applicable than) that dissipated by routers and NIs .in this project we recognition on energy dissipated through network links. Hyperlinks use up strength due to the switching interest (each self and coupling) induced by next data styles traversing the hyperlink. We consciousness on facts encoding schemes as a viable manner to reduce strength dissipated through the community hyperlinks. The fundamental idea is to opportunely encode the information earlier than their injection within the community in this kind of way as to reduce the switching pastime of the links. The fabrication technology permit designers to implement a whole device on a single chip, however the inherent design complexity of such structures makes it tough to absolutely explore the generation capacity. For that reason, the design of system-on-Chip (SoCs) is generally based at the reuse of predesigned and pre-proven highbrow assets core which might be interconnected via unique verbal exchange assets that must manage very tight performance and area constraints. Further to the ones application-associated constraints, deep consequences pose bodily design challenges for long wires and international on-chip conversation. a likely approach to conquer those demanding situations is to exchange from a fully synchronous layout paradigm to a globally asynchronous, locally synchronous (GALS) layout paradigm. A network on-Chip (NoC) is an infrastructure essentially composed routers interconnected via communication channels. It's far appropriate to help the GALS paradigm, because it offers asynchronous communication, scalability, reusability and reliability.

#### II. RELATED WORK

The information encoding techniques can be categorized into classes. In the first class, encoding strategies focus on decreasing the electricity due to self-switching hobby of character bus strains while ignoring the power dissipation attributable to their coupling switching pastime. On this class, bus invert (BI) and INC-XOR were proposed for the case that random information styles are transmitted through those lines. However, gray code, T0, operatingquarter encoding, and T0-XOR have been recommended for the case of correlated facts patterns. Application-precise procedures have also been proposed. This class of encoding isn't always suitable to be carried out in the deep sub micron meter technology nodes wherein the coupling capacitance constitutes a prime part of the total interconnect capacitance. This causes the electricity intake due to the coupling switching activity to come to be a huge fraction of the total hyperlink strength consumption, making the aforementioned strategies, which forget about such contributions, inefficient. The works within the second class focus on decreasing energy dissipation via the discount of the coupling switching among these schemes, the switching pastime is decreased the usage of many extra manipulate traces. For instance, the information b us width grows from 32 to 55. The strategies proposed have a smaller number of manage lines however the complexity of their interpreting logic is high. The technique described in is as follows: first, the statistics are each abnormal inverted and even inverted, after which transmission is done the usage of the type of inversion which reduces greater the switching activity in the coupling switching interest is decreased.

On this project, we use a less complicated decoder even as accomplishing a better past time reduction. Let us now discuss in more detail the works with which we examine our proposed schemes. In, the wide variety of transitions from zero to one for two consecutive flits (the flit that just traversed and the one which is ready to traverse the link) is counted. If the quantity is bigger than half of the link width, the inversion may be accomplished to lessen the quantity of 0 to at least one transition when the flit is transferred thru the link. This method is most effective worried approximately the self switching without stressful the coupling switching. Note that the coupling capacitance inside the state-of-the-artwork silicon era is considerably large (e.g., four instances) as compared with the self-

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

capacitance, and consequently, need to be considered in any scheme proposed for the link energy reduction. Further, the scheme was primarily based on the hop-by usinghop approach, and consequently encoding/interpreting is accomplished in each node

#### III. PROPOSED SYSTEM

We present the proposed encoding scheme whose intention is to lessen power dissipation by using minimizing the coupling transition activities on the hyperlinks of the interconnection network allow us to first describe the strength model that incorporates unique components of electricity dissipation of a link. The dynamic energy dissipated with the aid of the interconnects drivers .One can classify four styles of coupling transitions as described. A type I transition takes place whilst one of the strains switches when the opposite remains unchanged. In a type II transition, one line switches from low to high at the same time as the other makes transition from high to low. A type III transition corresponds to the case in which each traces switch simultaneously. Finally, in a type IV transition both traces do not change. The effective switched capacitance varies from type to type, an for this reason, the coupling transition activity, is a weighted sum of various forms of coupling transition contribution.

#### A. Scheme I

The scheme compares the contemporary information with the preceding one to decide whether or not unusual inversion or no inversion of the modern-day information can result in the hyperlink energy reduction. If the flit is peculiar inverted before being transmitted, the dynamic electricity on the hyperlink

### TABLE I: Effect of Odd Inversion on Change of Transition Types

| Time       | Normal         |                |        | Odd Inverted          |                |         |

|------------|----------------|----------------|--------|-----------------------|----------------|---------|

|            | Type I         |                |        | Types II, III, and IV |                |         |

| t-1        | 00, 11         | 00, 11, 01, 10 | 01, 10 | 00, 11                | 00, 11, 01, 10 | 01, 10  |

| t          | 10, 01         | 01, 10, 00, 11 | 11, 00 | 11, 00                | 00, 11, 01, 10 | 10, 01  |

|            | T1*            | T1**           | T1***  | Type III              | Type IV        | Type II |

| t - 1      | Type II        |                |        | Type I                |                |         |

|            | 01, 10         |                |        | 01, 10                |                |         |

|            | 10, 01         |                |        | 11, 00                |                |         |

| t - 1<br>t | Type III       |                |        | Type I                |                |         |

|            | 00, 11         |                |        | 00, 11                |                |         |

|            | 11, 00         |                |        | 10, 01                |                |         |

| t - 1      | Type IV        |                |        | Type I                |                |         |

|            | 00, 11, 01, 10 |                |        | 00, 11, 01, 10        |                |         |

|            | 00, 11, 01, 10 |                |        | 01, 10, 00, 11        |                |         |

Table I reports, for each transition, the relationship among the coupling transition activities of the flit while transmitted as is and when its bits are bizarre inverted records are prepared as follows. The first bit is the cost of the frequent i th line of the link, while the second one bit represents the value of its (i + 1) th line. For every partition, the first (2nd)line represents the values at time t - 1 (t). As table I suggests, if the flit is ordinary inverted, types II, III, and IV transitions convert to kind I transitions within the case of type I transitions, the inversion ends in one of types II, III, or type IV transitions. Specifically, transitions indicated as T1\*, T1\*\*and T1\*\*\* inside the table convert to sorts II, III, and IV transitions, respectively. This is the exact circumstance to be used to determine whether the abnormal invert needs to be completed. Since the terms  $T0 \rightarrow 1$  (odd) and  $T0 \rightarrow 0$ (odd) are weighted with a issue of one/four, for link widths greater than sixteen bits, the misprediction of the invert circumstance will no longer exceed 1.2% on common.

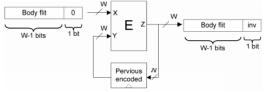

Fig.1. (a) Encoder architecture scheme I Circuit diagram

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

Fig.1. (b) Encoder architecture scheme I, Internal view of the encoder block (E).

Accordingly, we are able to approximate the precise situation as the usage of the approximated peculiar invert circumstance reduces the effectiveness of the encoding scheme due to the mistake brought on via the approximation but it simplifies the hardware implementation of encoder. Assuming the link width of w bits, the overall transition among adjoining strains is w-1, and subsequently as a result, we can write (1) as

$$T_{V} > (w - 1) / 2....(1)$$

Proposed Encoding Architecture: The proposed encoding architecture, which is based totally at the unusual invert situation defined by using (1), proven in Fig. 1. We keep in mind a hyperlink width of w bits. If no encoding is used, the frame flits are grouped in w bits with the aid of the NI and are transmitted via the link. In our approach, one little bit of the hyperlink is used for the inversion bit, which suggests if the flit traversing the hyperlink has been inverted or now not greater mainly, the NI packs the body flits in w - 1 bits [Fig. 1(a)]. The encoding common sense E, which is included into the NI, is chargeable for identifying if the inversion must take place and appearing the inversion if needed. The wellknown block diagram proven in Fig.1(a) is the same for all three encoding schemes proposed on this paper and simplest the block E is one-of-a-kind for the schemes. To make the choice, the formerly encoded flit is compared with the modern -day flit being transmitted. This latter, whose w bits are the concatenation of w-1 payload bits and a "zero" bit, represents the primary input of the encoder, whilst the previous encoded flit represents the second input of the encoder [Fig. 1(b)].

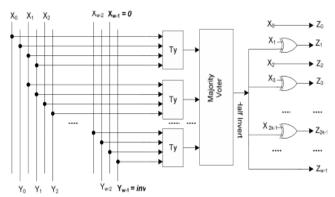

The w - 1 bits of the incoming (previous encoded) body flit are indicated by way of Xi (Yi), i = 0, 1,...,w - 2. The w th little bit of the previously encoded body flit is indicated by using inv which shows if it was inverted (inv =1) r left because it changed into (inv=0). in the encoding common sense, each Ty block takes the 2 adjoining bits of the enter flits (e.g., X1X2Y1Y2, X2X3Y2Y3, X3X4Y3Y4, etc.) and sets its output to "1" if any of the transition styles of Ty is detected. Because of this the atypical inverting for this pair of bits leads to the reduction of the hyperlink electricity dissipation (desk I). The Ty block can be carried out the usage of a easy circuit. The second level of the encoder, that's a majority voter block, determines if the situation given in (1) is satisfied (a better number of 1s within the input of the block in comparison to 0s). If this circumstance is satisfied, inside the remaining degree, the inversion is achieved on unusual bits. The decoder circuit in reality inverts the received flit while the inversion bit is high.

#### **B. Scheme II**

In the proposed encoding scheme II, we employ each odd (as discussed previously) and full inversion. The total inversion operation converts kind II transitions to type IV transitions. The scheme compares the contemporary data with the previous one to determine whether the odd, complete, or no inversion of the modern-day information can supply upward thrust to the link energy reduction (2).

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

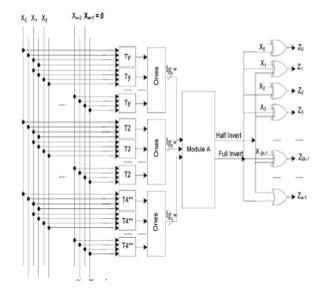

Fig.2. Encoder architecture Scheme II.

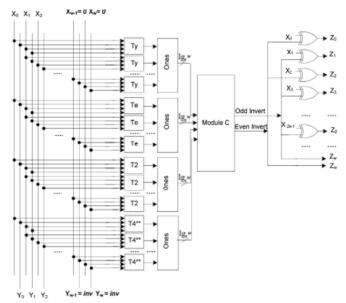

#### C. Scheme III

Inside the proposed encoding Scheme III, we upload even inversion to Scheme II. The reason is that odd inversion converts some of type I (T1\*\*\*) transitions to type II transitions. As can be determined from table II, if the flit is even inverted, the transitions indicated as T1\*\*/T1\*\*\* in the table are converted to type IV/type III transitions. Therefore, the even inversion may lessen the hyperlink electricity dissipation as nicely. The scheme compares the present day information with the previous one to determine whether unusual, even, completes, or no inversion of the modern statistics can deliver upward thrust to the link power reduction.

**TABLE II: Effect Of Even Inversion On Change Of Transition Types**

|      |             | <u> </u>      |       |                  |               |          |

|------|-------------|---------------|-------|------------------|---------------|----------|

| Time |             | Normal        |       | Even Inverted    |               |          |

|      | Type I      |               |       | Types II,III, IV |               |          |

| t-1  | 01,10       | 00, 11, 01,10 | 00,11 | 01,10            | 00, 11, 01,10 | 00,11    |

| t    | 00,11       | 10 ,01, 11,00 | 01,10 | 10,01            | 00, 11,01,10  | 11,00    |

|      | T1*         | T1**          | T1*** | Type II          | Type IV       | Type III |

| t-1  | Type II     |               |       | Type I           |               |          |

| t    | 01, 10      |               |       | 01,10            |               |          |

|      | 10,01       |               |       | 00, 11           |               |          |

| t-1  | Type III    |               |       | Type I           |               |          |

| t    | 00, 11      |               |       | 00, 11           |               |          |

|      | 11,00       |               |       | 01, 10           |               |          |

| t-1  | Type IV     |               |       | Type I           |               |          |

| t    | 00,11,01,10 |               |       | 00, 11, 01, 10   |               |          |

|      | 00,11,01,10 |               |       | 10, 01, 11, 00   |               |          |

Fig. 4. Encoder architecture Scheme III.

Proposed Encoding Architecture: The working ideas of this encoder are just like the ones of the encoders imposing Schemes I and II. The proposed encoding architecture, that's primarily based on the even invert circumstance of (7), the full invert circumstance of (8), and the odd invert situation of (9), is proven in Fig.4. The w th bit of the previously encoded body flit is indicated through inv which suggests if it was even, odd, or full inverted (inv=1) or left because it was (inv=zero). The first degree of the encoder determines the transition types even as the second level is formed by means of a hard and fast of 1s blocks which count the wide variety of ones in their inputs. In the first degree, we've got delivered the Te blocks which determine if any of the transition varieties of T2, T1\*\* and T1\*\*\* is detected for each pair bits in their inputs. For those transition kinds, the even invert motion yields link electricity discount. Again, we've 4 Ones blocks to decide the number of detected transitions for every Ty, Te, T2, T4\*\* blocks. The output of the ones blocks are inputs for Module C. This module determines if unusual, even, complete, or no invert action corresponding to the outputs "10," "01," "11," or "00," respectively, need to be carried out. The outputs "01," "eleven," and "10" display that whether (7), (8), and (9), respectively, are satisfied.

#### V. SIMULATION RESULTS

Fig.5 (a): Scheme I output

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

Fig.5 (b): Scheme II output

Fig.5(c): Scheme III output

#### **EXTENSION RESULTS (LDPC)**

Fig.6: LDPC output

#### **RTL Schematic:**

Fig.7: RTL Schematic of Data Encoder

#### IV. CONCLUSION

In this Project, we have offered a set of new data encoding schemes aimed toward lowering the strength dissipated by the links of a NoC. In truth, links are accountable for a huge fraction of the overall energy dissipated by the conversation machine. Further, their contribution is expected to growth in future era nodes. Compared to the preceding encoding schemes proposed within the literature, the purpose behind the proposed schemes is to minimize not best the switching hobby, but additionally (and particularly) the coupling switching activity that's especially answerable for hyperlink strength consumption inside the deep sub micron meter era regime. The proposed encoding schemes are agnostic with admire to the underlying NoC architecture neither in the sense that their application does no longer require any change neither within the routers nor in the hyperlinks. An intensive evaluation has been completed to assess the effect of the encoder and decoder common sense within the NI. The encoders imposing the proposed schemes were reduced the power consumption. The affects on the performance, power, and strength metrics had been studied the usage of a cycle- and bit accurate NoC simulator underneath each synthetic and actual traffic situations.

#### REFERENCES

[1] Global era Roadmap for Semiconductors. (2011) [Online]. Available: http://www.itrs.internet

## R

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

- [2] M. S. Rahaman and M. H. Chowdhury, —Crosstalk avoidance and error correction coding for coupled RLC interconnects, in Proc. IEEE Int. Symp. Circuits Syst., May additionally 2009, pp.141–144.

- [3] W.Wolf, A.Jerraya, and G. Martin, —Multiprocessor machine-on-chip MPSoC technology, IEEE Trans. Compute.-Aided layout Integrated Circuits Syst., vol. 27, no. 10, pp. 1701–1713, Oct. 2008.

- [4] L.Benini and G. DeMicheli, —Networks on chips: a new SoC paradigm, pc, vol. 35, no. 1, pp. 70–78, Jan. 2002.

- [5] S. E. Lee and N. Bagherzadeh, —A variable frequency link for a power aware community-on- chip (NoC), Integrated VLSI J., vol. 42, no. 4, pp. 479–485, Sep. 2009.

- [6] D.Yeh,L.S.Peh,S.Borkar,J.Darringer,A.Agarwal,andW. M.Hwu, —Thousand-middle chips round table,IIEEE layout check Compute., vol. 25, no. 3, pp. 272–278, can also–Jun. 2008.

- [7] A.Vittal and M. Marek-Sadowska, —Crosstalk reduction for VLSI, IEEE Trans. Comput.-Aided layout Integrated Circuits Syst., vol. sixteen, no. three, pp. 290–298, Mar. 1997.

- [8] M. Ghoneima, Y. I. Ismail, M. M. Khellah, J. W. Tschanz, and V. De, —Formal derivation of choicest lively protecting for low-electricity on-chip buses, IEEE Trans. Comput-Aided design Integrated Circuits Syst., vol. 25, no. 5, pp. 821–836, may additionally 2006.

- [9] L.Macchiarulo, E.Macii, and M.Poncino, —twine placement for crosstalk strength minimization in cope with buses, I in Proc. design Autom take a look at Eur. Conf. show off., Mar. 2002, pp. 158–162.

- [10] R.Ayoub and A.Orailoglu, —A unified transformational approach for reductions in fault vulnerability, strength, and crosstalk noise and postpone on processor buses, in Proc. design Autom. Conf. Asia South.