## **International Journal of Research**

Available at <a href="https://pen2print.org/index.php/ijr/">https://pen2print.org/index.php/ijr/</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

## Design of Nand Gate by Using Dvs and Multitheshold Technique

Y.Narendra & M.Koteswara Rao

<sup>1</sup>PG Scholar, Dept. of ECE, Chalapathi Institute of Technology, Guntur, AP.

<sup>2</sup>Assistant professor, Dept. of ECE, Chalapathi Institute of Technology, Guntur, AP.

#### Abstract

In advanced and simple circuits, control utilization assumes a critical job in CMOS gadget. Because of scale down innovation in VLSI circuits the edge voltage of transistors lessened however increments threshold spillage current. To decrease the sub threshold spillage current the powerful circuit level procedure is proposed. In this paper, the MTCMOS strategy is proposed which gives fast and low power scattering by keeping up the execution of the circuits. The NAND entryway is structured utilizing DVS and MTCMOS strategy gives slightest power utilization. Every one reenactments has been performed on Leather treater EDA Tool adaptation 14.1. The proposed method lessens the power scattering by 30% to 70%.

#### INTRODUCTION

Building low-control VLSI circuits has a huge execution objective as a result of the redesigning the innovation in remote correspondence frameworks and different hardware gadgets. In the previous decades the VLSI creators give the more significance estimate. execution cost. dependability. While in present day VLSI the power utilization is critical, speed furthermore, territory is as yet the principle prerequisites of a plan. The general power utilization can be lessened when the working voltage (VDD) be not exactly the VTH limit voltages existing in VLSI circuits. Power dissemination is decreased by scaling the supply voltage. For accomplishing the high execution, high thickness and low power

# R

## **International Journal of Research**

Available at <a href="https://pen2print.org/index.php/ijr/">https://pen2print.org/index.php/ijr/</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

utilization, the CMOS innovation has been ceaselessly downsized to make the power utilization under control. As of late there is request of fast, best execution in remote correspondence frameworks as close to home versatile communicators furthermore, computerized associates which has expanded the prerequisite of low power VLSI circuits Dynamic power and static power are the fundamental segments of intensity dissemination in CMOS gadgets. Dynamic power dissemination is expended of exchanging movement of transistors also, static power is because of independent of transistors exchanging.

Dynamic power contains exchanging power and in addition short circuit power and static power utilization results from intersection, sub-edge and current spillages created by CMOS transistors. There are two unique methods to lessen the power utilization of CMOS transistors is multi. The two

procedures were disclosed in this work to diminish the control utilization dynamic voltage scaling and multi limit CMOS

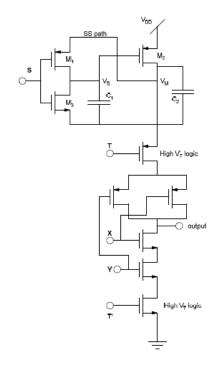

## I. PROPOSED DVTS AND MTCMOS METHOD

The proposed circuit joins the voltage scaling and MTCMOS procedure. The method is probed 2 input NAND door utilizing EDA leather treaterdevice 14.1. The circuit appears in Fig 3 works in two modes one is dynamic mode and second is backup mode. In dynamic method of task, the VDD is downsized through voltage scaling and sharing charge to strife dynamic power dispersal. By applying rationale 0 and 1 to rest and rest bar the high VT transistors are turned on and carries on as typical transistors. At the point when S is rationale 1, M3 turns on this makes transistor M2 and entire VDD is encouraged to the circuit. At

### **International Journal of Research**

Available at <a href="https://pen2print.org/index.php/ijr/">https://pen2print.org/index.php/ijr/</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

the point when S is rationale 0, transistors M1 and M2 are killed which drops the

voltage to ground. The capacitor C1 and C2 shares charge self adjustmentway which diminishes the voltage dimension of VM. In such condition, transistor M2 turns on, expanding the voltage dimension of VS and additionally decreases varieties in VS. Henceforth, dynamic power scattering is diminished trough scaling system. In backup method of task, the information sources connected to rationale doors and its yield does not change, the high VT transistor rest and rest block in the circuit are killed by giving rest what's more, rest bar rationale 1 and rationale 0. This gives high obstruction way between two high transistors, in this manner MTCMOS strategy additionally diminished the spillage current in reserve mode. Consequently the generally speaking force is diminished by mix of voltage scaling what's more, MTCMOS strategy.

Fig.1.Proposed cicuit using voltage scaling and MTCMOS

#### II. THE TESTED CIRCUIT

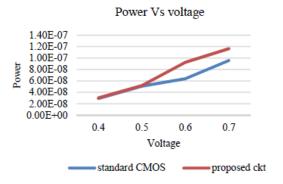

The proposed circuits were actualized on 2 input NAND entryway utilizing EDA device Tanner V14.1 with  $0.25\Box$  CMOS innovation. The supply voltage running from

# R

### **International Journal of Research**

Available at <a href="https://pen2print.org/index.php/ijr/">https://pen2print.org/index.php/ijr/</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

0.4V to 0.8V. The limit voltage is higher than that VDD gives low control utilization.

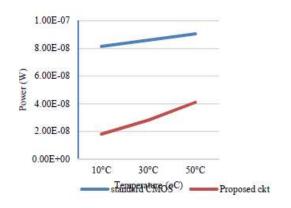

The proposed circuit results is contrasted and the standard CMOS circuits. For improving outcomes the proposed circuits are completed for power, differing voltages and temperatures.

Fig.2. Power consumption with varying supplyvoltage

Fig.3.Power consumption with temperature.

The power utilization as opposed to changing voltage the proposed circuit is likewise reproduced at different temperatures from 10o to 50o over standard circuit

#### III. CONCLUSION

The voltage scaling and MTCMOS method has been portrayed in this paper. The proposed circuit lessens the both dynamic and static power and has kept up the execution of the circuit. The proposed method diminishes the power scattering by 30% to 70%. It has been seen that the proposed procedure is connected on the rationale circuit and its execution and power utilization is assessed. What's to come work will incorporate the work of the proposed strategy on various rationale doors working in subthreshold voltage.

## **International Journal of Research**

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

### **REFERENCES**

- [1] AnkishHanda, PaanshulDobriyal,

Geetanjali Sharma, "A Novel High

execution Low Power Universal Gate

Implementation in SubthresholdDistrict," in

, February 2014.

- [2] F. Abdollahi, Fallah, and M. Pedram,

"An Effective Power Mode Change

Technique in MTCMOS Circuits," in 2005.

- [3] Hyo-Sig Won, et al., "A MTCMOS Design Methodology and Its Application to Mobile Computing," in 2003

- [4] A. Abdollahi, F. Fallah and M. Pedram, "Spillage current decrease in CMOS VLSI circuits by information vector control," in Feb. 2004