## **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

Elevated Appearance on VLSI application by using Design of 8bit, 1633j1m2, 444/lW squarer

<sup>1</sup>GUNDA SUKANYA, <sup>2</sup> A RAVINDHRA BABU

<sup>1</sup>PG Scholar, Dept. of ECE, Chalapathi Institute of Technology, Guntur, AP.

<sup>2</sup>Assistant professor, Dept. of ECE, Chalapathi Institute of Technology, Guntur, AP.

**ABSTRACT**

In this paper, another plan for structure and VLST usage of squarer circuits is proposed. The proposed configuration depends on further examination and adjustment of squaring capacity's scientific articulation and gives high proficiency in equipment usage. This enhancement depends on two systems, first, logarithmic revamp of each outcome bit, and second, utilizing foreseen symmetry from recently determined outcomes and applying it for other parts of the circuit. The proposed squarer has been executed in TSMC 180nm CMOS innovation and assessment results exhibits 14 percent decrease in kick the bucket zone, 18 percent decrease in static power utilization and furthermore minor enhancement in execution contrasted with traditional squarer.

**I.INTRODUCTION**

Squaring of twofold numbers is a standout amongst the most helpful tasks in advanced flag handling, cryptography and polynomial assessment. It very well may be actualized in programming, yet in high requesting applications, programming squarer is wasteful. Along these lines, plan of

# R

### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

enhanced squarer equipment has progressed toward becoming urgent. Diverse methodologies for equipment usage of squarer. The thought of partitioning squarer parts, have brought about littler advancement of high-radix squarer and multipliers. Other approach depended on truncated squarer and multiplier circuit in which a stochastic strategy have been connected to accomplish most outcome in spite of killing a bit of hardware. Our proposed plan is ordered among another technique that attempts to apply Boolean logarithmic principles on result conditions to accomplish better circuit attributes. Gibson and Gibard have checked on and talked about points of interest and impediments of a few distinctive circuit executions as far as territory, control utilization and postpone time. These methodologies are separated in two principle classes including sequential and parallel multipliers. Numerous

Complementary calculations for them two have been proposed. Our proposed squaring system is in view of parallel engineering.

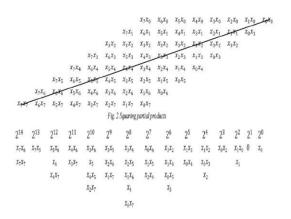

Fig.1 Partial products for 8bit squarer after initial simplification

#### II.PROPOSED METHOD

To accomplish a superior plan, it is vital to comprehend and utilize the distinction among squarer and multiplier to the fullest. The incomplete items from aftereffect of a 8 bit squaring task are appeared. With basic examination, obviously incomplete items au can be executed without utilizing any equipment asset, as communicated beneath:

# ®

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

Xn.Xn=Xn

The other distinction in squaring is the symmetry between incomplete items ai \* aj.

As appeared

in Fig 3, above and underneath the symmetry line, a similar fractional item is rehashed in each segment. Working with parallel numbers, this augmentation by 2 can be improved by left move activity. In this manner, one of the halfway items is moved to one side section and the other one is overlooked

TABLE.1

Partial products table before& after simplification

| 2 <sup>2</sup>        | 2 <sup>1</sup> | 20                    |  |  |

|-----------------------|----------------|-----------------------|--|--|

| Before Simplification |                |                       |  |  |

| _                     | $x_1 x_0$      | $x_{0}x_{0}$          |  |  |

| _                     | $x_0 x_1$      | _                     |  |  |

| After simplification  |                |                       |  |  |

| $x_{1}x_{0}$          | _              | <i>x</i> <sub>0</sub> |  |  |

#### **III.RESULTS AND DISCUSSION**

The previously mentioned techniques are blended and connected to the plan of effective equipment for 4-8 bit squarer. To assess the plan attributes post amalgamation reproduction is performed utilizing TSMC 180nm CMOS advanced library. Moreover plan from Cho and Chung was adjusted for 4 to 8 bits, and afterward executed utilizing a similar library. For looking at our plan with Cho and Chung's structure, Wallace tree including plot was utilized to additionally enhances the two plans productivity. Results

### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

are appeared in table .Looking at two structures, it tends to be noticed that our plan enhances squarer circuit in each perspective. bit squarer, configuration impressive has lower postponement of 34%, bring down territory of 30% and bring down intensity of 22%. in any case, the postponements of the two circuits are joined by expanding the quantity of bits, and our plan for 8 bit square is just 3% (imperceptibly) quicker contrasting with Cho's, while our plan zone is decreased by 14% and static control dissemination is diminished by 18%.

TABLE.2 Final results of design squarer

|           |         | -7 0        |         |             |

|-----------|---------|-------------|---------|-------------|

| Ref       | Squarer | Propagation | Power   | Area        |

|           | Bit     | delay (ns)  | (µWatt) | $(\mu m^2)$ |

| This work | 4       | 0.64        | 34.7    | 189.6       |

| [7]       |         | 0.99        | 48.5    | 272.7       |

| This work | 6       | 2.47        | 191.5   | 848.2       |

| [7]       |         | 2.86        | 224.4   | 964.5       |

| This work | 7       | 3.01        | 293.03  | 1190        |

| [7]       |         | 3.05        | 344.6   | 1327.2      |

| This work | 8       | 3.62        | 444.86  | 1633.2      |

| [7]       |         | 3.73        | 542.64  | 1896.0      |

#### **IV.CONCLUSION**

This paper exhibits another structure for parallel squarer circuit. Proposed configuration uses the reuse and further rearrangements of Boolean terms and in addition the symmetry to accomplish productive squarer equipment. This plan has been reenacted in CMOS 180nm innovation impressive and the outcome shows enhancement in power and region without execution debasement. At long last we may reason that the proposed squarer equipment is a promising contender for low power,

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

high thickness computerized handling applications.

#### REFERENCES

- [1] K. Cho and J. Chung, "Parallel squarer structure utilizing pre-determined wholes of fractional items," in 2007.

- [2] S. Bui and 1. E. S. Jr, "Extra Optimizations for Parallel Squarer Units," in 2014.

- [3] J. A. Gibson and R. W. Gibbard, "Combination and Comparison of Two's Complement Parallel Multipliers," in 1975.

- [4] D. K. Das and A. Banerjee, "A New Squarer plan with decreased region and postponement," in 2016.