#### International Journal of Research

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

### Design of Digital Clock Manager Based Reconfigurable BFD–True Random Number Generator in Xilinx

KOTAREDDY V SUBBAREDDY <sup>1</sup>, DR.E.SARVARAMESWARUDU <sup>2</sup>

<sup>1</sup>P.G Student, VLSI

2 Professor, Department of Electronics and Communication Engineering, Kits engineering College, divili.

Abstract: Cryptographic systems have become an integral part of our daily life through the need of security activities such as communication, electronic money systems, and disc encryptions. Random numbers is a key component for strengthening and confidentiality of securing the electronic communications and used in many cryptographic applications like key generation, encryption, masking protocols, internet gambling. Unpredictable random numbers are essential for the security cryptographic algorithms for generating underlying secret keys. TRUE random number generators (TRNGs) have become an vital component in many cryptographic systems, including PIN/password generation, authentication protocols, key generation, random padding, and nonce generation. The circuit utilizes undetermined random process, usually in the form of electrical noise, as a basic source. Field programmable gate arrays (FPGAs) form an ideal platform for hardware implementations of many of these security algorithms. Proposed TRNG is based on the principle of beat frequency detection for Xilinx-FPGA-based applications.

Keywords—True random number generator (TRNG), Cryptography, Field programmable gate arrays (FPGA), Bit frequency detection (BFD), Dynamic reconfiguration port (DRP).

#### I. INTRODUCTION

In today's, world security is of most noteworthy significance and thus cryptography assumes an essential part in PC and systems administration security. Cryptography is an arrangement of procedures for concealing data. It is utilized in a few fields as a major aspect of security conventions to anchor arranged data and information. Correspondence, being a basic piece of life, including the web and different methods for correspondence

has offered ascends security dangers. Cryptography in this manner gives the important insurance from the dangers by securing the information, i.e. giving diverse means and techniques for changing over information into an ambiguous frame. The fundamental point of cryptography is that the unapproved client cannot got to information. The substance of the information edges ought to be encoded with unequivocal example. Another application is to guarantee that the information should dependably be recognized by the originator of the message. Irregular numbers are basic to security on the grounds that cryptographic frameworks rely upon the presence of some mystery information known to approved clients and erratic by others and regularly arbitrary strings are utilized to warrant its eccentrics (e.g., in keys, salts, nounces, challenges, introduction vectors. and other one-time quantities)[1].

#### II. RELATED WORK

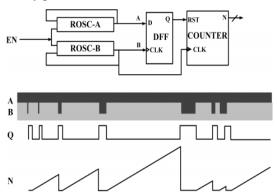

A Single Phase BFD-TRNG Model The structure and working of the (single stage) BFDTRNG [6] can be abridged as takes after, in conjunction with Fig.1:

- The circuit comprises of two indistinguishable ring oscillators (it is named as ROSCA and ROSCB), with comparative development and position. Because of intrinsic physical arbitrariness starting from process variety impacts related with profound sub-micron CMOS fabricating, one of the oscillators (say, ROSCA) sways marginally quicker than the other oscillator (ROSCB). Also, the creator proposed to utilize trimming capacitors to additionally tune the oscillator yield frequencies.

- 2) The yield of one of the ROs is utilized to test the yield of the other, utilizing a D flip-tumble (DFF). Without loss of simplification, accept the yield of ROSCA is bolstered to the D-contribution of the

## ®

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

DFF, while the yield of ROSCB is associated with the clock contribution of the DFF.

- 3) At certain time interims (dictated by the recurrence contrast of the two ROCs), the quicker oscillator flag passes, gets up to speed, and overwhelms the slower motion in stage. Because of irregular jitter, these catching occasions occur aimlessly interims, called "Beat Frequency Intervals". Accordingly, the DFF yields a rationale 1 at various irregular examples.

- 4) A counter controlled by the DFF increases amid the beat recurrence interims, and gets reset because of the rationale 1 yield of the DFF. Because of the irregular jitter, the free running counter yield increase to various pinnacle esteems in every one of the tally up interims before getting reset.

- 5) The yield of the counter is examined by an inspecting clock before it achieves its greatest esteem.

- 6) The examined reaction is then serialized to get the arbitrary piece stream.

Fig. 1: Architecture of single phase BFD-TRNG.

### III. TUNABLE BFD-TRNG FOR FPGA BASED APPLICATIONS

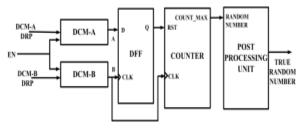

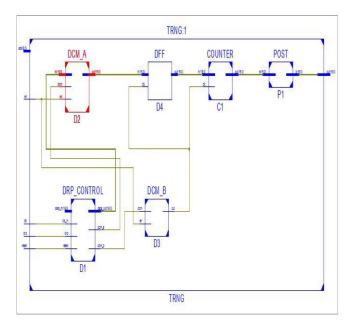

Fig 2 demonstrates the general design of the Digital Clock Manage based tunable BFD- TRNG. Instead of two ring oscillators, two DCM modules create the The swaying waveforms. DCM natives parameterized to create marginally unique frequencies, by altering two outline parameters M (Multiplication Factor) and D (Division Factor). In proposed outline, the TRNGspring haphazardness is the jitter introduced in the DCM hardware. The DCM modules permit more

noteworthy fashioner control over the clock waveforms, and their use takes out the requirement for starting alignment. Tunability is set up by setting the DCM parameters on– the– fly utilizing DPR capacities utilizing DRP ports. This capacity gives the outline more noteworthy adaptability than the ring oscillator based BFD-TRNG. The distinction in the frequencies of the two created clock signals is caught utilizing a DFF.

Fig. 2: Overall architecture of proposed Digital Clock Manager based tunable BFD–TRNG.

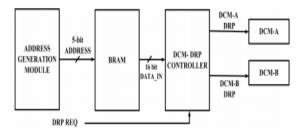

The DFF sets when the quicker oscillator finishes one cycle more than the slower one (at the beat recurrence interim). A counter is driven by one of the produced clock flags, and is reset when the DFF is set. Adequately, the counter expands the throughput of the produced arbitrary numbers. The last three LSBs of the most extreme tally esteems came to by tally were found to demonstrate arbitrariness properties. The objective recurrence is dictated by the arrangement of parameter esteems really chose. The irregular qualities came to by the counter, and in addition the jitters are identified with the picked parameters M and D. This makes it conceivable to tune the proposed TRNG utilizing the foreordained put away M and D esteems. As unlimited DPR has been appeared to be a potential danger to the circuit, the safe operational esteem blends of the D and M parameters for each DCM are foreordained amid the outline time, and put away on an on chip Block RAM (BRAM) memory obstruct in the FPGA. There are really two distinct choices for the clock generators – one can utilize the Phase Locked Loop (PLL) hard macros accessible on Xilinx FPGAs, or the DCMs. We next depict scientific and test comes about which

#### International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848

p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

constrained us to pick DCM for the PLL modules for clock waveform age.

Excellent irregular numbers are of basic significance to numerous logical applications, especially for Monte Carlo reproductions. Given the benefits of superior and reproducibility, pseudorandom number generators (PRNGs) in view of straight repeats over F2 are generally embraced in such reproductions. One predominant F2-straight PRNG is the Mersenne Twister (MT), which has extensive stretch and great equidistribution. Be that as it may, MT is additionally demonstrated to have certain disadvantages. For instance, one difficult issue is that it is touchy to poor introduction and can set aside a long opportunity to recoup from a zero-overabundance beginning state. The TRNG equi dispersed extensive stretch direct (TRNG) calculation is proposed to settle this issue. Contrasted and MT, TRNG has better equi appropriation [8] while holding an equivalent period length As application sizes scale, one rising pattern is to create parallelized form of the applications to abuse the accessible parallel equipment assets, for example, in field-programmable gate (FPGAs), to accomplish fast in execution. Being the key segment of different logical applications, planning PRNGs that can quickly give autonomous parallel floods of fantastic arbitrary numbers is likewise ending up progressively imperative in current frameworks. The quick hop ahead strategy gives an effective technique to decide the beginning stage of another sub stream from a current sub stream, in this manner enabling different PRNGs to produce autonomous sub streams in parallel and giving solid hypothetical help to parallelizing F2direct PRNGs with significant lot.

With its favorable circumstances over MT, TRNG additionally gets awesome consideration from the product network. In any case, few equipment usage can be found. The Ukalta Engineering Corporation gave a short prologue to its item that utilizes the calculation. Notwithstanding, TRNG accomplishes a throughput of one example each two cycles and no basic subtle elements are uncovered. We propose a more asset effective structure that diminishes the use of BRAMs from four to two,

while holding a similar throughput. The aggregate asset utilized is additionally decreased as much as half contrasted and the first structure. additionally outline a product/equipment system to parallelize its yield stream in view of the new structure[8]. All the more particularly, we make the accompanying commitments.

- 1) An asset productive equipment engineering for TRNG with a throughput of one example for each cycle.

- 2) A committed 6R/2W RAM structure for TRNG, which is equipped for giving six Reads and two Writes simultaneously in a solitary cycle, with little asset overhead.

- 3) A product/equipment system to create parallel arbitrary numbers.

Fig. 3: Architecture of tuning circuity.

#### SIMULATION RESULTS

2. Summary 2.1. On-Chip Power Summary

| 1 |           |   | On-C  | hip l | Pov | er Sum | na | ry        |   |             |     | 1 |

|---|-----------|---|-------|-------|-----|--------|----|-----------|---|-------------|-----|---|

| I | On-Chip   | I | Power | (mW)  | 1   | Used   | I  | Available | ١ | Utilization | (%) | 1 |

| I | Clocks    | 1 |       | 1.30  | ı   | 3      | ı  |           | ı |             |     | ı |

| I | Logic     | 1 |       | 0.00  | 1   | 10     | 1  | 11776     | 1 |             | 0   | 1 |

| 1 | Signals   | 1 |       | 0.00  | 1   | 20     | 1  | ===       | 1 |             |     | 1 |

| 1 | IOs       | 1 |       | 0.00  | 1   | 20     | 1  | 372       | 1 |             | 5   | 1 |

| 1 | Quiescent | 1 | 3     | 1.52  | 1   |        | 1  |           | 1 |             |     | 1 |

| 1 | Total     | 1 | 3     | 2.83  | 1   |        | 1  |           | 1 |             |     | 1 |

Fig. 4: power report

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

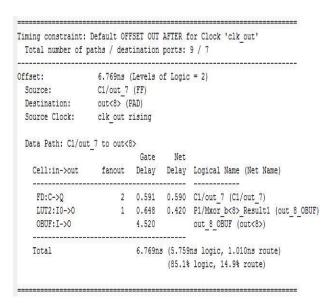

Fig. 5: Timing report

| Device Utilization Summary (estimated values) |      |           |             |  |  |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |  |  |

| Number of Slices                              | 9    | 5888      |             |  |  |  |  |

| Number of Slice Flip Flops                    | 10   | 11776     |             |  |  |  |  |

| Number of 4 input LUTs                        | 17   | 11776     |             |  |  |  |  |

| Number of bonded IOBs                         | 20   | 372       |             |  |  |  |  |

| Number of GCLKs                               | 1    | 24        |             |  |  |  |  |

Fig. 6: Design Summary

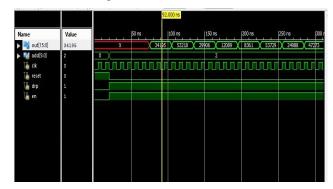

Fig. 7: RTL Schematic

Fig. 8: waveforms

#### CONCLUSION:

An improved fully digital tunable TRNG for FPGA based applications, based on the principle of Beat Frequency Detection and clock jitter, and with inbuilt error correction capabilities is presented. The TRNG utilizes this tunability feature for determining the degree of randomness, thus providing a high degree of flexibility for various applications. The proposed design successfully passes all NIST statistical tests.

#### REFERENCES

[1] DongshengLiu, Zilong Liu, Lun Li, and Xuecheng Zou(2016) A Low-Cost Low-Power Ring

# R

#### International Journal of Research

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 22 November 2018

Oscillator-Based Truly Random Number Generator for Encryption on Smart Card.

- [2] Johnson A.P., R. S. Chakraborty and D. Mukhopadhyay(2015)"APUFEnabled Secure ArchitectureforFPGA BasedIoTApplications," in EEE Transactions on Multi-Scale Computing Systems.

- [3] Johnson A.P., R. S. Chakraborty and D. Mukhopadhyay(2015) "A Novel Attack on a FPGA based True Random Number Generator", 10th Workshop on Embedded Systems Security.

- [4] Johnson A.P., S. Saha, R. S. Chakraborty, D. Mukhopadyay and Sezer Goren(2014)"Fault Attack on AES via Hardware Trojan Insertion by Dynamic Partial Reconfiguration of FPGA over Ethernet", 9th Workshop on Embedded Systems Security.

- [5] Rukhin A., J. Soto, J. Nechvatal, M. Smid and E. Barker(2001) "A Statistical Test Suite for Random and Pseudorandom Number Generators for Cryptographic Applications", DTIC Document.

- [6] Tang N., B. Kim, Y. Lao, K. K. Parhi and C. H. Kim(2014)"True Random Number Generator circuits based on single- and multi-phase beat frequency detection," Proceedings of the IEEE 2014 Custom Integrated Circuits Conference.

- [7] Von Neumann J. ,(1951)"Various Techniques used in Connection with Random Digits.", National Bureau of Standards Applied Mathematics Series.

- [8] Yuan Li, Paul Chow, Senior Member, IEEE, Jiang Jiang, Minxuan Zhang, and Shaojun Wei(2014) Software/Hardware Parallel Long-Period Random Number Generation Frame'work Based on the TRNG Method.