# International Journal of Research Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 23 December 2018

**Design of Low Power 9t Sram Using Single Bit Line**

<sup>1</sup>ATCHA LALITHA, <sup>2</sup>T.VAISHNAVI CHANDRA, <sup>3</sup>D.NAGA RAVI KIRAN

<sup>1</sup>M.Tech Student, Dept. of ECE, Chalapathi Institute of Technology, Guntur, AP.

<sup>2</sup>Assistant professor, Dept. of ECE, Chalapathi Institute of Technology, Guntur, AP.

<sup>3</sup>Associate professor & HOD, Dept. of ECE, Chalapathi Institute of Technology, Guntur, AP.

**ABSTRACT**

The Static sporadic access memory structure is requesting because of the combination of the

technique parameters with CMOS headway scaling. It ends up testing in light of the fact that the

dependability, make limit and spillage control use should all be considered to give an ideal

execution. The proposed cell depletes 8.54% less power showed up distinctively in connection to

twofold piece line SRAM. The 2 bit-line plan of SRAM has more dispersal of intensity in

perspective of the charging and releasing of correlative piece lines. This paper drives a solitary

piece line 9T SRAM structure which depletes chop down power and low spillage. It has a high

analyzed SNM with staggering static and dynamic read/shape execution. Single piece line

approach prompts chop down power utilization showed up distinctively in connection to the

traditional 2 bit-line SRAMs. Regardless, the entry time for read and make activity is expanded.

Keywords: Single Bit Line, Low Power Operation, Static Noise Margin, 9T SRAM.

**I.INTRODUCTION**

In the present moved world, recollections

are key fragments of the vast majority of the

contraptions. Starting now and into the

# R

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 23 December 2018

foreseeable future, an eagerness for low power and low zone gobbling up recollections has been stretched out with a fundamental of better effectiveness and execution. Due to their convenience and having an average for low support spillage, SRAM cells are generally utilized for implanted applications. One system for lessening power scattering is by curtailing supply voltage. With scaling, the static power dispersal diminishes, near to a diminishing in the nature of the SRAM. Single piece line plan for SRAMs is a yielding framework for low power circuit assortments. There is bringing down spillage and reduced exchanging intensity of the bitline with a decrease in chip zone. A basic extent of dynamic impact difficulty is open amidst the perused or makes activity. Utilizing the single piece line approach, the extent of power depleted is diminished by

half of the dynamic control utilized in bitline exchanging. In any case, augmentation in inspire the chance to time is seen as a control amidst the read and structures endeavors [1]. Another 9T cell SRAM is proposed in [2] with investigated activity having a differential regard the sense speaker. This cell appears on changed events decrease in read and shape control utilization near to bring down spillage control. Another game plan in [3] presents a 9T bit cell for lower voltage practices with supply investigation approach. Amidst the make undertaking, the commitment from the bit-lines debilitates the draw up course of action of the bit cell. High enhanced make edges are acquired and task at a low voltage is developed with no additional gear. A distinctive arrangement differential SRAM cell is advanced with a definitive goal to perform read activity near to single-

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 23 December 2018

finished Plan make development. parameters, for example, hold and spare mode power, SNM and spillage current have been utilized for relationship. SRAMs with lower number of transistors have besides been relied upon to accomplish low power targets. Reference has conceived a 8T SRAM cell with single finished endeavor. Both the read and make practices are performed utilizing the single piece line. It solidifies a 6T cell with a read support including 2 transistors. This structure separates the coupled rework er amidst the read technique. Utilizing this method, the read complain edge objectives of the standard 6T and 8T SRAMs are kept up a key partition from. A 9T SRAM cell which is examined irritate free with single finished methodology for bit-interleaving application has been presented in [6]. Updated frame edge adjacent pieces bury leaving setup, which does not meddle with read limit is picked up utilizing an investigation cutoff plan of making. The association between the current and the quality is limited by passing on a read-decoupled bolster system. In like manner, climbing with an enhanced read execution and read undertaking.

#### **II.PROPOSED SYSTEM**

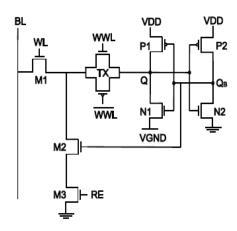

A 9T SRAM cell with a single piece line is arranged as showed up in Fig.1. A single piece line 'BL' is used for the two exercises of scrutinizing and forming. The other control signals are word-line control hail WL, form word line signal WWL and read enable RE. The cell focus contains several cross-coupled inverters that store the data bit regard. The read path includes transistors M1, M2, M3 and make route contains out of transistor M1 and a transmission gateway TX. The inspiration driving transmission portal is to decouple the inverter consolidate

# R

#### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 23 December 2018

in the midst of read and hold strategies for movement. The essential test is making a motivating force into the cell using a solitary piece line. In a SRAM cell including differential piece lines, the 'Make 1' assignment is cultivated by creating a 0 into the contrary end of the cross-coupled inverter. Regardless, accepting in a manner of speaking one piece line is accessible, making a 1 with no make help technique ends up troublesome because of the limit drop across over access transistor M1. Consequently, one of the NMOS in the inverter couple is related with a floating center point VGND, which cripples the yield center. In hold mode and read mode, the VGND hail is related with circuit ground.

Fig.1.Single bit line 9T SRAM Cell

A. Hold Mode: The make control signals WL and WWL and read control hail RE are harmed. VGND is connected with ground terminal. As the section transistor is OFF, the inverter couple is withdrawn from the bit-line. This enhances the static uproar edges.

**B. Read Mode:** The control signals WL and RE are enabled for scrutinizing the set away data. VGND is related with ground terminal. WWL signal is disabled, which withdraws the inverter couple from the bit-line. This partition is the inspiration driving why

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 23 December 2018

scrutinized SNM is almost in indistinguishable class from hold SNM for the 9T SRAM. If a 0 is secured in the cell, QB=1, bit-line BL discharges through transistors M1, M2 moreover, M3.

C. Compose Mode: The form control signs, WL and WWL are enabled to trade data from the bit-line BL to the inverters (Q and QB). Peruse enable banner RE is weakened and VGND center point is drifting. The passage transistor M1 and transmission portal TX store the regard on the bit-line into the SRAM cell.

#### III.SIMULATION SETUP

A. Read Stability: The dependability amidst investigating of a cell is depicted as Read static tumult edge (RSNM) or the best estimation of clamor because of DC that the SRAM can remain with no change of the set away information bit. The yields Q and QB

will be given bustle sources (DC Voltage) and DC examination is performed to get the butterfly bend [2]. The RSNM is settled as  $1/\sqrt{2}$  times the side of the best square that fits in the turn i.e. length of the square's corner to corner.

B. Compose Ability: The limit of shaping into a SRAM is settled utilizing the make edge as looks for after. The charging of the bit-line is done popular to contain the information to be stacked into the cell and the word line is changed from voltage estimations of 0 to 1. Make edge is the time when the information bits Q and QB flip. Another parameter to be surveyed is the frame trip point. It is the most lifted voltage respect present on the bit-line which will result in change of the cell substance.

**C. Read Access Time:** It is handled as the time required between the incitation of the word-line to the modification in the bit-line

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 23 December 2018

regard which was in the pre-changed state to the set away piece regard. The edges for count are taken as 10% of low voltage regard and 90% of high voltage regard.

**D.** Compose Access Time: The time required for forming a 1 is the time length between commencements of word line WL and when the set away piece regards at Q changes to 1. This is called Write-1 get the opportunity to time. In like manner, for forming a 0 it is the time taken between order of WL and when the set away piece a motivating force at Q changes to 0. This is named as Write-0 get the chance to time. The make get the opportunity to time for 0 and 1 fluctuates for the single piece line assignment. The cutoff points are identical to those considered for read get the chance to time figuring.

**E. Power Consumption:** The entire power exhausted in the SRAM cell is enlisted as

the entire of the power utilized for charging and discharging the bit-lines and the power required to activate the diverse control signals. It might be figured by evaluating the total current taken from the source and after that finding the consequence of current drawn and supply voltage.

F. Hold SNM: The quality of the SRAM in the hold mode is given by the Hold SNM. It is portrayed as the DC noise that can be persisted by the SRAM cell without a degradation of the set away data bit in the midst of the hold mode. Its estimation is done using the butterfly twist technique. SNM is the width of the side of greatest square that fits in the butterfly twist.

#### **IV.CONCLUSION**

A strong single piece line low power 9T SRAM cell is all things considered masterminded and taken a stab at its right

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 23 December 2018

errand. The sorted out cell is separated and a twofold piece line 9T SRAM regarding specific execution parameters. The cell shows a decent soundness in read and structures assignments. The SNM is nearly the equal for both single and twofold piece line cells. A decrease in the control use is comparatively seen. The composed cell debilitates 8.54% less power showed up contrastingly in connection to twofold piece line SRAM. The zone of the cell will in like way be less, there being a lone piece line, rather than two. The read get to times of the two cells are in like way essentially indistinguishable, with the read 0 activity putting aside less time for the single piece line cell. The central exchange off saw is in regards to make inspire the chance to time i.e. the masterminded cell has more prominent make inspire the chance to time emerged from futile line SRAM cells. Hence

we can express that the orchestrated 9T single piece line cell, while keeping up the diverse execution parameters like the present twofold piece line configuration, demonstrates a lower control use and also has an inconsequential lesser zone.

#### REFERENCES

[1] Amandeep Singh Dhindsa, Suman Saini, "A Novel differential 9T cell SRAM with reduced sub-threshold leakage power", IEEE International Conference on Advances in Engineering & Technology Research (ICAETR - 2014).

[2] Jay Narayan, R.K.Sharma, "A Novel Single Ended 8T SRAM with Improved Noise Margins and Stability", Recent Advances in Engineering and Computational Sciences (RAECS), 2014.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 05 Issue 23 December 2018

- [3] Basavaraj Madiwalar, Dr. Kariyappa B.S, "Single Bit-line 7T SRAM cell for Low power and High SNM", International Mutli-Conference on Automation, Computing, Communication, Control and Compressed Sensing (iMac4s), 2013.

- [4] H V Ravish Aradhya, B. V. Vishwas, "A Novel SRAM Cell Design for Low Power Applications", in June-2015.

- [5] Sheng Lin, Yong-Bin Kim, Fabrizio Lombardi, "A 32nm SRAM Design for Low Power and High Stability", 51st Midwest Symposium on Circuits and Systems, 2008.