Design of full adder using VHDL

# <sup>1</sup>Rashmi Kumari, <sup>2</sup>Swapnil Rai, <sup>3</sup>Subha Kaushik

<sup>1</sup> Student of ECE Dept. in Dronacharya College of Engineering, Gurgaon under MDU University <sup>1</sup>rashmi.15217@ggnindia.dronacharya.info

<sup>2</sup>Student of ECE Dept. in Dronacharya College of Engineering, Gurgaon under MDU University <sup>2</sup>swapnil.15236@ggnindia.dronacharya.info

<sup>3</sup>Student of ECE Dept. in Dronacharya College of Engineering, Gurgaon under MDU University <sup>2</sup>subha.15254@ggnindia.dronacharya.info

### **ABSTRACT**

In thi paper we are going to design full adder using VHDL. The acronym VHDL stands for VHSIC (Very High Speed Integrated Circuits) Hardware Description Language. This paper includes the design of full adder with behavioral modelling in VHDL, truth table and results are verified with simulation software Xilinx.

## Keywords:

VHDL, VHSIC, full adder, behavioral modelling, simulation, xilinx

#### **INTRODUCTION**

The digital systems include lots of digital systems on a chip and board. This paper implements the design of full adder using VHDL language. The VHDL is very flexible hardware description language. It offers multiple kinds of modeling to describe the hardware of the circuit we wants to implements. In this paper we are using behavioral modelling in designing full adder. Behavioral style of modelling specifies the behavior of an entity with the help of sequentially executed statements.

## **FULL ADDER**

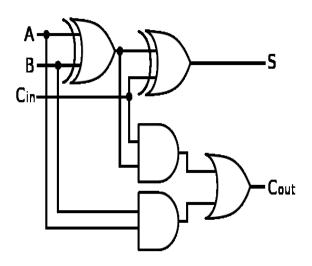

Full adder is a digital device which adds binary numbers and accounts for values carried in as well as out. A one-bit full adder adds three one-bit numbers, often written as A, B and Cin; A and B are the operands, and Cin is a bit carried in from the previous less significant stage. The full adder is usually a component in a cascade of adders, which add 8, 16, 32, etc. bit binary numbers. The circuit produces a two-bit output, output carry and sum typically represented by the signals Cout and S. A full adder can be implemented in lots of ways such as with a custom transistor-level circuit or composed of other gates.

## **BOOLEAN EXPRESSION**

$S = A \oplus B \oplus Cin$

$Cout = (A.B) + (Cin \cdot (A \oplus B))$

Available at http://internationaljournalofresearch.org

Fig. Circuit Diagram of full adder

| INPUT |   |     | OUTPUT |      |

|-------|---|-----|--------|------|

| A     | В | Cin | S      | Cout |

| 0     | 0 | 0   | 0      | 0    |

| 0     | 0 | 1   | 1      | 0    |

| 0     | 1 | 0   | 1      | 0    |

| 0     | 1 | 1   | 0      | 1    |

| 1     | 0 | 0   | 1      | 0    |

| 1     | 0 | 1   | 0      | 1    |

| 1     | 1 | 0   | 0      | 1    |

| 1     | 1 | 1   | 1      | 1    |

Fig. Truth Table of Full Adder

## Program in VHDL

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

- ---- any Xilinx primitives in this code.

- --library UNISIM;

- --use UNISIM.VComponents.all;

entity full is

Port (a: in STD\_LOGIC; b: in STD\_LOGIC; Cin: in STD\_LOGIC;

```

S: out STD_LOGIC;

Cout: out STD_LOGIC);

end full;

architecture Behavioral of full is

```

```

begin

process(A,B,Cin)

begin

if(A='0' \text{ and } B='0' \text{ and } Cin='0') then

S < = '0':

Cout<='0':

elsif(A='0' \ and \ B='0' \ and \ Cin='1') then

S < ='1':

Cout<='0':

elsif(A='0' \ and \ B='1' \ and \ Cin='0') then

S < ='1':

Cout<='0';

elsif(A='0' \ and \ B='1' \ and \ Cin='1') then

S<='0':

Cout<='1':

elsif(A='1' \ and \ B='0' \ and \ Cin='0') then

S < ='1';

Cout<='0':

elsif(A='1' \ and \ B='0' \ and \ Cin='1') then

S<='0':

Cout<='1':

elsif(A='1' \ and \ B='1' \ and \ Cin='0') then

S < = '0':

Cout<='1':

else

S < ='1';

Cout<='1';

end if;

```

end Behavioral;

end process;

### **CONCLUSION**

We have used VHDL coding for design of full adder. VHDL offers very high flexibility as it is the only most flexible Hardware description language. It offers flexibility in design reuse and move design between multiple vendors tools. VHDL facilitates a top-down design methodology using synthesis design at high implementation-independent level, Delay decision on implementation details, we can

Available at http://internationaljournalofresearch.org

easily explore design alternatives, solve architecture problems before implementation and automatic mapping of a high-level description technology specific implementation. [3]. Design and implementation of Full Adder Using Vhdl and Verification in Analog Domain, Rupesh Prakash Raghate, Swapnil S.Rajurkar, Priyanka U Badhe, Pravin L, Turale

### **REFERENCES**

[4]. Engineersworld.worldpress.com

[1]. En.wikipedia.org

[5]. Tehlab.com/VHDL Code Full Adder/

[2]. Engr.mun.ca

[6].www2.cs.siu.edu