International Journal of Research (IJR) e-ISSN: 2348-6848, p- ISSN: 2348-795X Volume 2, Issue 09, September 2015 Available at http://internationaljournalofresearch.org

# A Novel Multi Level Converter Unified Power-Quality (MC-UPQC) Conditioning System on Line Loading, Losses, and Voltage Stability of Radial Distribution Systems

# Popuri Krishna Chaitanya\*1;Tajuddin Sayyad<sup>2</sup> & Dr. Abdul Ahad<sup>3</sup>

<sup>1</sup>M.tech (P.S) Student Department Of EEE, Nimra College Of Engineering & Technology

<sup>2</sup> Asst. Professor Department Of EEE, Nimra College Of Engineering & Technology

<sup>3</sup>Professor & Head Of The Department, Nimra College Of Engineering & Technology

<sup>1</sup><u>chaitanyapkc@gmail.com</u>; <sup>2</sup><u>tajuddin.sayyad@gmail.com</u>

#### Abstract:

This paper presents a new unified power-quality conditioning system (MC-UPQC), capable of simultaneous compensation for voltage and current in multi-bus/multi-feeder systems. In this configuration, one shunt voltage-source converter (shunt VSC) and two or more series VSCs exist. The system can be applied to adjacent feeders to compensate for supply-voltage and load current imperfections on the main feeder and full compensation of supply voltage imperfections on the other feeders. In the proposed configuration, all converters are connected back to back on the dc side and share a common dc-link capacitor. Therefore, power can be transferred from one feeder to adjacent feeders to compensate for sag/swell and interruption. The proposed topology can be used for simultaneous compensation of voltage and current imperfections in both feeders by sharing power compensation capabilities between two adjacent feeders which are not connected. The system is also capable of compensating for interruptions without the need for a battery storage system and consequently without storage capacity limitations. The performance of the MC-UPQC as well as the adopted control algorithm is illustrated by simulation. The simulation results show that a significant amount of power-loss reduction, under voltage mitigation, and the enhancement of voltage stability margin can be obtained with an appropriate placement of the MC-UPQC in a distribution network. The performance comparison of the MC-UPQC with one previously reported design approach shows that it is more efficient in under voltage mitigation.

#### Introduction

With increasing applications of nonlinear and electronically switched devices in distribution systems and industries, power-quality (PQ) problems, such as harmonics, flicker, and imbalance have become serious concerns. In addition, lightning strikes on transmission lines, switching of capacitor banks, and various network faults can also cause PQ problems, such as transients, voltage sag/swell, and interruption. On the other hand, an increase of sensitive loads involving digital electronics and complex process controllers requires a pure sinusoidal supply voltage for proper load operation.

Recently, multi converter FACTS devices, such as an interline power-flow controller (IPFC) and the generalized unified power-flow controller (GUPFC) are introduced. The aim of these

**International Journal of Research (IJR)** e-ISSN: 2348-6848, p- ISSN: 2348-795X Volume 2, Issue 09, September 2015

Available at http://internationaljournalofresearch.org

devices is to control the power flow of multi lines or a sub network rather than control the power flow of a single line by, for instance, a UPFC. When the power flows of two lines starting in one substation need to be controlled, an interline power flow controller (IPFC) can be used. An IPFC consists of two series VSCs whose dc capacitors are coupled. This allows active power to circulate between the VSCs. With this configuration, two lines can be controlled simultaneously optimize the to network utilization.

The GUPFC combines three or more shunt and series converters. It extends the concept of voltage and power-flow control beyond what is achievable with the known two-converter UPFC. The simplest GUPFC consists of three converters-one connected in shunt and the other two in series with two transmission lines in a substation. The basic GUPFC can control total five power system quantities, such as a bus voltage and independent active and reactive power flows of two lines. The concept of GUPFC can be extended for more lines if necessary. The device may be installed in some central substations to manage power flows of multi lines or a group of lines and provide voltage support as well. By using GUPFC devices, the transfer capability of transmission lines can be increased significantly.

#### **Proposed MC-UPQC System**

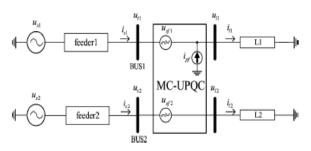

A. Circuit Configuration The single-line diagram of a distribution system with an MC-UPQC is shown in Fig.

Fig.1 Single-line diagram of a distribution system with an MC-UPQC.

As shown in this figure, two feeders connected to two different substations supply the loads L1 and L2. The MC-UPQC is connected to two buses BUS1 and BUS2 with voltages of  $u_{t1}$ and  $u_{t2}$ , respectively. The shunt part of the MC-UPQC is also connected to load L1 with a current Supply voltages are denoted  $i_{l1}$ of bv  $u_{s1}$  and  $u_{s2}$  while load voltages are  $u_{l1}$  and  $u_{l2}$ . feeder currents are denoted Finally, by  $i_{s1}$  and  $i_{s2}$  and load currents are  $i_{l1}$  and  $i_{l2}$ . Bus voltages  $u_{t1}$  and  $u_{t2}$  are distorted and may be subjected to sag/swell. The load L1 is a nonlinear/sensitive load which needs a pure sinusoidal voltage for proper operation while its current is non-sinusoidal and contains harmonics. The load L2 is a sensitive/critical load which needs a purely sinusoidal voltage and must be fully protected against distortion, sag/swell, and interruption. These types of loads primarily include production industries and critical service providers, such as medical centers, airports, or broadcasting centers where voltage interruption can result in severe economical losses or human damages.

#### B. MC–UPQC Structure

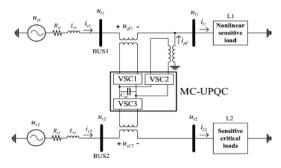

The internal structure of the MC–UPQC is shown in Fig.

**International Journal of Research (IJR)**

e-ISSN: 2348-6848, p- ISSN: 2348-795X Volume 2, Issue 09, September 2015 Available at http://internationaljournalofresearch.org

Fig.2 Typical MC-UPQC used in a distribution system.

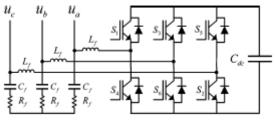

It consists of three VSCs (VSC1, VSC2, and VSC3) which are connected back to back through a common dc-link capacitor. In the proposed configuration, VSC1 is connected in series with BUS1 and VSC2 is connected in parallel with load L1 at the end of Feeder1. VSC3 is connected in series with BUS2 at the Feeder2 end. Each of the three VSCs in Fig. 2 is realized by a three-phase converter with a commutation reactor and high-pass output filter as shown in Fig.

Fig.3 Schematic structure of a VSC.

The commutation reactor  $(L_f)$  and high- pass output filter  $(R_f, C_f)$  are connected to prevent the flow of switching harmonics into the power supply. As shown in Fig. all converters are supplied from a common dc-link capacitor and connected to the distribution system through a transformer. Secondary (distribution) sides of the series-connected transformers are directly connected in series with BUS1 and BUS2, and the (distribution)side of the secondary shuntconnected transformer is connected in parallel

with load L1. The aims of the MC-UPQC shown in Fig are:

1) to regulate the load voltage  $(u_{l1})$  against sag/swell and disturbances in the system to protect the nonlinear/sensitive load L1;

2) to regulate the load voltage  $(u_{l2})$  against sag/swell, interruption, and disturbances in the system to protect the sensitive/ critical load L2;

3) to compensate for the reactive and harmonic components of nonlinear load current  $(i_{l1})$ .

In order to achieve these goals, series VSCs (i.e., VSC1 and VSC3) operate as voltage controllers while the shunt VSC (i.e., VSC2) operates as a current controller.

C. Control Strategy

As shown in Fig., the MC-UPQC consists of two series VSCs and one shunt VSC which are controlled independently. The switching control strategy for series VSCs and the shunt VSC are selected to be sinusoidal pulse width-modulation (SPWM) voltage control and hysteresis current control, respectively. Details of the control algorithm, which are based on the d–q method, will be discussed later. Shunt-VSC: Functions of the shunt-VSC are:

1) to compensate for the reactive component of load L1 current;

2) to compensate for the harmonic components of load L1 current;

3) to regulate the voltage of the common dc-link capacitor.

Fig. shows the control block diagram for the shunt VSC.

The measured load current  $(i_{l\_abc})$  is transformed into the synchronous dq0 reference frame by using

$$i_{l\_dq0} = T^{dq0}_{abc} i_{l\_abc}$$

.

where the transformation matrix is shown, at the bottom of the page.

By this transform, the fundamental positivesequence component, which is transformed into dc quantities in the d and q axes, can be easily extracted by low-pass filters (LPFs). Also, all harmonic components are transformed into ac quantities with a fundamental frequency shift

$$\begin{split} &i_{l\_d} = \overline{i}_{l\_d} + \overline{i}_{l\_d} \\ &i_{l\_q} = \overline{i}_{l\_q} + \overline{i}_{l\_q} \end{split}$$

where  $i_{l\_d}, i_{l\_q}$  are d-q components of load current,  $i_{l\_d}, i_{l\_q}$

are dc components, and  $i_{l\_d}, i_{l\_d}$  are the ac components of

$$\overline{i}_{l\_d}, \overline{i}_{l\_q}$$

If  $i_s$  is the feeder current and  $i_{pf}$  is the shunt VSC current and knowing  $i_s = i_l - i_{pf}$ , then d-q components of the shunt VSC reference current are defined as follows:

$$\begin{split} i^{\text{ref}}_{pf\_d} &= i_{l\_d} \\ i^{\text{ref}}_{pf\_q} &= i_{l\_q}. \end{split}$$

Consequently, the d-q components of the feeder current are

$$i_{s\_d} = \overline{i}_{l\_d}$$

$i_{s\_q} = 0.$

This means that there are no harmonic and reactive components in the feeder current. Switching losses cause the dc-link capacitor voltage to decrease. Other disturbances, such as the sudden variation of load, can also affect the dc link. In order to regulate the dc-link capacitor voltage, a proportional–integral (PI) controller is used as shown in Fig. The input of the PI controller is the error between the actual capacitor voltage  $(u_{de})$  and its reference value  $(u_{de}^{ref})$ . The output of the PI controller [i.e.,  $\Delta i_{de}$ ] is added to the d component of the shunt-VSC reference current to form a new reference current as follows:

$$\begin{cases} i_{pf\_d}^{\text{ref}} = \tilde{i}_{l\_d} + \Delta i_{dc} \\ i_{pf\_q}^{\text{ref}} = i_{l\_q} \end{cases}$$

As shown in Fig., the reference current is then transformed back into the abc reference frame. By using PWM hysteresis current control, the output-compensating currents in each phase are obtained

$$i_{pf\_abc}^{\text{ref}} = T_{dq0}^{abc} i_{pf\_dq0}^{\text{ref}}; (T_{dq0}^{abc} = T_{abc}^{dq0^{-1}}).$$

Series-VSC: Functions of the series VSCs in each feeder are:

1) to mitigate voltage sag and swell;

2) to compensate for voltage distortions, such as harmonics;

3) to compensate for interruptions (in Feeder2 only).

The control block diagram of each series VSC is shown in Fig. The bus voltage  $(u_{t-abc})$  is detected and then transformed into the synchronous dq0 reference frame using

$$u_{t\_dq0} = T_{abc}^{dq0} u_{t\_abc} = u_{t1p} + u_{t1n} + u_{t10} + u_{th}.$$

Where

$$\begin{cases} u_{t1p} = \begin{bmatrix} u_{t1p\_d} & u_{t1p\_q} & 0 \end{bmatrix}^T \\ u_{t1n} = \begin{bmatrix} u_{t1n\_d} & u_{t1n\_q} & 0 \end{bmatrix}^T \\ u_{t10} = \begin{bmatrix} 0 & 0 & u_{00} \end{bmatrix}^T \\ u_{th} = \begin{bmatrix} u_{th\_d} & u_{th\_q} & u_{th\_0} \end{bmatrix}^T \end{cases}$$

International Journal of Research (IJR) e-ISSN: 2348-6848, p- ISSN: 2348-795X Volume 2, Issue 09, September 2015 Available at http://internationaljournalofresearch.org

$u_{t1p}, u_{t1n}$  and  $u_{t10}$ are fundamental frequency negative-. and zero-sequence positive-, components, respectively, and  $u_{\rm th}$  is the harmonic component of the bus voltage. According to control objectives of the MC-UPQC, the load voltage should be kept sinusoidal with a constant amplitude even if the bus voltage is disturbed. Therefore, the expected load voltage in  $(u_{l\_dq0}^{exp})$ the synchronous dq0 reference frame only has one value.

$$u_{l\_dq0}^{\exp} = T_{abc}^{dq0} u_{l\_abc}^{\exp} = \begin{bmatrix} U_m \\ 0 \\ 0 \end{bmatrix}$$

where the load voltage in the abc reference frame  $(u_{l-abc}^{exp})_{is}$

$$u_{l\_abc}^{\exp} = \begin{bmatrix} U_m \cos(\omega t) \\ U_m \cos(\omega t - 120^\circ) \\ U_m \cos(\omega t + 120^\circ) \end{bmatrix}.$$

The compensating reference voltage in the synchronous dq0 reference frame  $(u_{sf\_dq0}^{ref})$  is defined as

$$u_{sf\_dq0}^{ref} = u_{t\_dq0} - u_{t\_dq0}^{exp}$$

.

This means  $u_{t1p\_d}$  in should be maintained at

$U_m$  while all other unwanted components must be eliminated. The compensating reference voltage is then transformed back into the abc reference frame. By using an improved SPWM voltage control technique (sine PWM control with minor loop feedback), the output compensation voltage of the series VSC can be obtained.

# **Simulation Results**

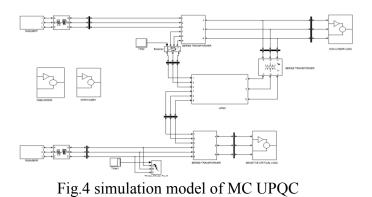

The proposed MC-UPQC and its control schemes have been tested through extensive case study

simulations using PSCAD/ EMTDC. In this section, simulation results are presented, and the performance of the proposed MC-UPQC system is shown.

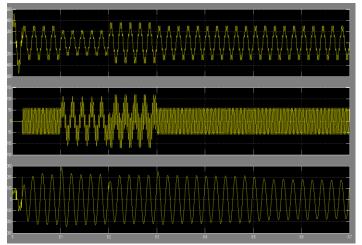

Fig.5 Simulation results for an upstream fault on Feeder2: BUS2 voltage, compensating voltage, and loads L1 and L2 voltages.

International Journal of Research (IJR) e-ISSN: 2348-6848, p- ISSN: 2348-795X Volume 2, Issue 09, September 2015

Available at http://internationaljournalofresearch.org

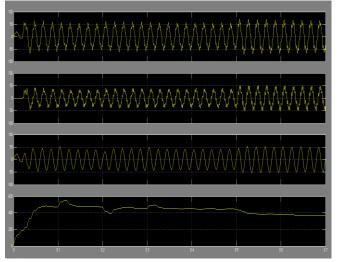

Fig.6 Simulation results for load change: nonlinear load current, Feeder1 current, load L1 voltage, load L2 voltage, and dc-link capacitor voltage.

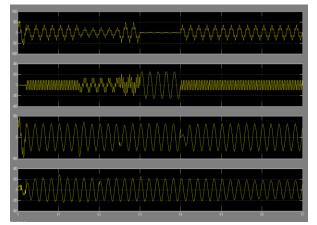

Fig.7 Nonlinear load current, compensating current, Feeder1 current, and capacitor voltage.

D. Distortion and Sag/Swell on the Bus Voltage Let us consider that the power system in Fig. 4 consists of two three-phase three-wire 380(v)(rms, L-L), 50-Hz utilities. The BUS1 voltage  $(u_{t1})$  contains the seventh-order harmonic with a value of 22%, and the BUS2 voltage  $(u_{t2})$ contains the fifth order harmonic with a value of 35%. The BUS1 voltage contains 25% sag between 0.1 s < t < 0.2 s and 20% swell between 0.2 s < t < 0.3 s. The BUS2 voltage contains 35% sag between 0.15 s < t < 0.25 sand 30% swell between 0.25 s < t < 0.3 s. The nonlinear/sensitive load L1 is a three-phase rectifier load which supplies an RC load of 10 $\Omega$ and 30 F. Finally, the critical load L2 contains a balanced RL load of 10 $\Omega$  and 100mH.

The MC–UPQC is switched on at t=0.02 s. The BUS1 voltage, the corresponding compensation voltage injected by VSC1, and finally load L1 voltage

# Conclusion

In this paper, a new configuration for simultaneous compensation of voltage and current in adjacent feeders has been proposed. The new configuration is named multi-converter unified power-quality conditioner (MC-UPQC). The performance of the MC-UPQC is evaluated under various disturbance conditions and it is shown that the proposed MC-UPQC offers the following advantages:

1) power transfer between two adjacent feeders for sag/swell and interruption compensation;

compensation for interruptions without the need for a battery storage system and, consequently, without storage capacity limitation;

sharing power compensation capabilities between two adjacent feeders which are not connected.

# REFERENCES

[1] Impact of Unified Power-Quality Conditioner Allocation on Line Loading, Losses, and Voltage Stability of Radial Distribution Systems Sanjib Ganguly, *Member, IEEE*

International Journal of Research (IJR) e-ISSN: 2348-6848, p- ISSN: 2348-795X Volume 2, Issue 09, September 2015 Available at http://internationaljournalofresearch.org

[2] M. Rastogi, R. Naik, and N. Mohan, "A comparative evaluation of harmonic reduction techniques in three-phase utility interface of power electronic loads," IEEE Trans. Ind. Appl., vol. 30, no. 5, pp. 1149–1155, Sep./Oct. 1994.

[3] F. Z. Peng, "Application issues of active power filters," IEEE Ind. Appl. Mag., vol. 4, no. 5, pp. 21–30, Sep./Oct. 1998.

[4] H. Akagi, "New trends in active filters for power conditioning," IEEE Trans. Ind. Appl., vol. 32, no. 6, pp. 1312–1322, Nov./Dec. 1996.

# BIBLIOGRAPHY

**Popuri Krishna Chaitanya:** pursuing M.Tech in Nimra College of engineering and technology, Jupudi, Ibrahimpatnam. His specialization in power systems. He graduated in Electrical and Electronics Engineering from Usharama College of Engineering & Technology, Telaprolu. Mail ID chaitanyapkc@gmail.com

**Tajuddin Sayyad:** is currently working as anASSISTANT PROFESSORin Electrical and

Electronics Engineering department at Nimra College of engineering and technology (NCET) Jupudi, Ibrahimpatnam. He obtained his M TECH degree in Digital systems and computer electronics. MAIL ID tajuddin.sayyad@gmail.com

Dr.Abdul Ahad : Mtech. P.hd (NITK) is an eminent PROFESSOR & HEAD OF EEE, nimra group of colleges. he received M.Tech and was conferred Doctorate from NITK SURATKAL. He is expertised in power electronics, power systems, special machines, Electrical machines& industrial applications. He has over a 15 years of teaching experience .He trains various students for various competitive exams like IES ,IAS, GATE , AP GENCO, AP TRANSCO, DISCOMS and no of national competitive exams. He is the chair person of several national and technical symposiums. He published more than 20 international journals and attended several international conferences. His prime interest is in research .to his credit he guided scores of UG AND PG students in their projects and right now he is guiding two P,hd scholars.