Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 12 August 2016

# Reduced Power Electronic Componets Using a New Cascade Structure in PV cell based three phase Multilevel Converter fed Induction Motor Drive Application

# Y.R.N.Satya Kumar

M-tech Student Scholar Department of Electrical & Electronics Engineering, Gudlavalleru Engineering College, Gudlavalleru; Krishna (Dt); A.P, India.

#### **Abstract:**

Multilevel inverters have an attracted a great deal of attenuation in medium voltage and high power application Due to their lower switching losses, EMI, high efficiency. Power electronic inverter become popular for various industrial drives applications. The multi-level inverter system is very promising in ac drives. Large electrical drives and utility application require advanced power electronics converter to meet the high power demands. As a result, multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations.In this paper, a new configuration of a three-phase 25 -level multilevel voltage source inverter fed induction motor drive applications introduced. The benefits of multilevel inverters are clear for medium-voltage drives industrial applications and are being considered for future naval ship propulsion systems. Considering the cascaded inverter to be one unit, it can be seen that a higher number of voltage levels are available for a given number of semiconductor devices. Finally an asymmetrical configuration is proposed with this we are getting 25 levels with ten switches and same configuration is implemented to Induction Machine Drive to check the drive performance. The results are obtained through Matlab/Simulink software package. Index Terms—Cascade. full-bridge converter. multilevel converter, optimal structure, total harmonic distortion (THD), Indcution Motor.

#### I. INTRODUCTION

Multilevel inverters are composed of a number of power electronic switches and DC voltage sources that produce a stepped voltage waveform in its output. Generally, multilevel inverters are divided into three categories as follows: neutral-point clamped inverter (NPC), flying capacitor inverter (FC), and cascaded Hbridge inverter (CHB). These inverters can surrender higher power with lower dv/dt and di/dt in output waveform which is to reduce EMI noise and Size of the output filter. Therefore,

Mr D. Vijay Arun

Assistant Professor

Department of Electrical & Electronics Engineering,

Gudlavalleru Engineering College,

Gudlavalleru; Krishna (Dt); A.P., India.

using theseinverters is very common nowadays. In recent years, several architectures have been proposed for cascade multilevel inverters [1-4]. This kind of inverters can produce more voltage levels and also provide higher quality of power in its output. As a result, this kind of inverter is considered more than other kinds of inverters. Cascade inverters are made of series separate single phase inverters with separate dc voltage sources. On the other hand, this inverter consists of a number of basic blocks (sub multilevel inverter) that each of these blocks has similar control system. One of the major advantages of this type of inverters is the ability of its modulation. So, if an error occurs in one of the blocks, it can replace or fix by using a control system, but there are some disadvantages such as high number of dc voltage sources and power electronic switches [5-7]. Increasing the number of power electronic switches leads to increase the number of driver circuits too. Both of these issues caused to increase in complexity, size, and cost of the circuit. Thus, reducing the number of power electronic switches is very vital and should be considered.

The most common initial application of multilevel converters has been in traction, both in locomotives and track-side static converters [8]. More recent applications been for power system converters VARcompensation and stability enhancement, active filtering, high-voltage motor drive, high-voltage dc transmission and most recently for medium voltage induction motor variable speed drives. Many multilevel converter applications focus on industrial medium-voltage motor drives, utility interface for renewable energy systems, Flexible AC Transmission System (FACTS) and traction drive systems. In recent years, multilevel inverters have received more attention in industrial applications, such as motor drives, static VAR compensators and renewable energy systems. Compared to the traditional two-level voltage source inverters, the stepwise output voltage is the major advantage of multilevel inverters [9]. This advantage results in higher power quality, better electromagnetic compatibility, lower

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 12 August 2016

switching losses, higher voltage capability, and needlessness of a transformer at distribution voltage level, thereby reducing the costs. In all the cases, the output voltage contains distortions [10-11].

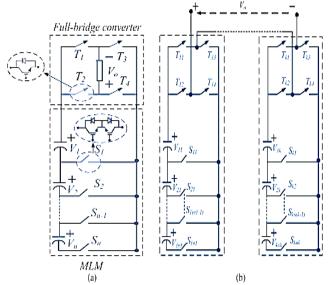

In [12], a new structure for the multilevel converter has been proposed with a reduced number of power electronic components. The structure of the proposed submultilevel converter is shown in Fig. 1(a), which consists of a multilevel module (MLM) and a full-bridge converter. As is shown in Fig. 1(b), for increasing the number of levels in output voltage, the proposed submultilevel converter has been extended in series. The first until the kth MLM consist of n1, n2, . . . , nk bidirectional switches, respectively. In this structure, the number oflevels and power IGBTs are given by the following equations, respectively [13],

Fig. 1. (a) Basic unit . (b) Proposed multilevel converter topology.

# II. RECOMMENDED STRUCTURE

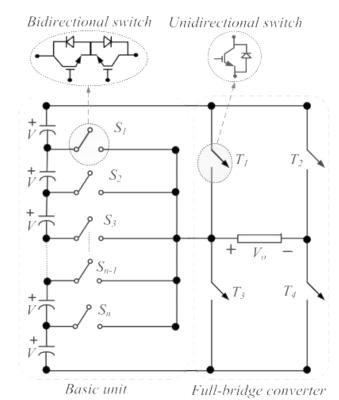

The recommended structure for a submultilevel converter is shown in Fig. 2. This topology consists of a full-bridge converter and a basic unit. The basic unit includes n bidirectional switches and (n + 1) capacitors. For bidirectional switches, several structures have been designed. For the proposed topology, the common emitter configuration is utilized, which is composed of two switches with each switch having an antiparallel diode and an IGBT. This structure requires only one gate driver circuit. In addition, the switches in afull-bridge converter are unidirectional, which consists of an IGBT and an antiparallel diode.

However, this topology requires a large number of power IGBTs and gate driver circuits. In addition, the maximum blocked voltage by bidirectional switches is high.

Fig. 2. Proposed submultilevel converter.

Fig. 3. Kind of output voltage waveform (Vo) for the proposed submultilevel converter.

TABLE I

Magnitudes of Vo For Various Switching States

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 12 August 2016

| state  | Switches states |       |  |           |       |       |       |       |       | Output  |

|--------|-----------------|-------|--|-----------|-------|-------|-------|-------|-------|---------|

|        | $S_I$           | $S_2$ |  | $S_{n-1}$ | $S_n$ | $T_I$ | $T_2$ | $T_3$ | $T_4$ | voltage |

| 1      | 0               | 0     |  | 0         | 0     | 1     | 1     | 0     | 0     | 0       |

| 2      | 0               | 0     |  | 0         | 1     | 0     | 0     | 0     | 1     | V       |

| 3      | 1               | 0     |  | 0         | 0     | 0     | 1     | 0     | 0     | -V      |

| 4      | 0               | 0     |  | 1         | 0     | 0     | 0     | 0     | 1     | 2V      |

| 5      | 0               | 1     |  | 0         | 0     | 0     | 1     | 0     | 0     | -2V     |

|        |                 |       |  |           |       |       |       |       |       |         |

| (2n+2) | 0               | 0     |  | 0         | 0     | 1     | 0     | 0     | 1     | (n+1)V  |

| (2n+3) | 0               | 0     |  | 0         | 0     | 0     | 1     | 1     | 0     | -(n+1)V |

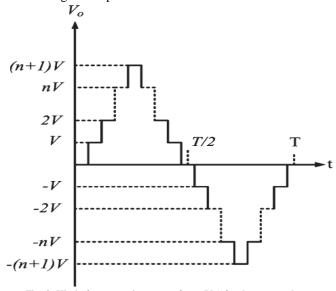

The kind of output voltage waveform for the proposed submultilevel converter is shown in Fig. 5. The magnitude of output voltages (Vo) for different switching states in the recommended submultilevel topology is presented in Table I. In this table, 1 means that the corresponding switch is turned ON, and 0 indicates the OFF-state. In the proposed submultilevel converter, the values of capacitor voltages are equal. Therefore, this converter is called a symmetrical submultilevel converter. In this structure, the number of levels can be calculated as follows:

$$N_{\text{level}} = 2n + 3$$

In addition, the total numbers of IGBTs (NIGBTs) and gate drivers (Ndriver) are given by the following equations, respectively:

$$N_{\text{IGBTs}} = 2n + 4$$

$N_{\text{driver}} = n + 4$

where n represents the number of bidirectional switches in the basic unit. In the recommended submultilevel converter, the maximum output voltage (Vomax) is

$$V_{o_{\text{max}}} = (n+1) \times V$$

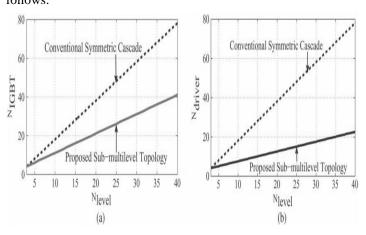

Fig. 4(a) compares the number of IGBTs versus the number of levels in the recommended submultilevel converter with a conventional symmetric cascade topology. This figure shows that the proposed topology requires the least number of IGBTs. Fig. 4(b) compares the number of drivers and indicates that the recommended structure needs a minimum number of drivers than conventional symmetrical topology. It is noticeable that

there are two types of power losses in a multilevel converter, which are named as follows:

#### A. Conduction Losses

In a multilevel converter, the conduction losses are the lossesthat occur while the power electronic elements are in the ON-state and conducting current. In the proposed submultilevel topology, depending on the output voltage, the number of devices (IGBTs and diodes) that are in current path in any instant of time varies between two and three, so that in the worst case (from the view point of losses), two IGBTs and one diode are in current path and in the best case, only two IGBTs are in the current path. Generally, the power loss during the conduction is evaluated by

$$P_{\text{cond}} = V_{\text{on}}(t).I(t)$$

where Von(t) is the ON-state voltage drop by the current that flows through the device, and I(t) is the conducting current. Generally, conduction losses of a transistor (Pcond,T) and diode (Pcond,D) are obtained as follows, respectively,

$$P_{\text{cond},T} = \left[ V_{\text{on},T}(t) + R_T . I^{\beta}(t) \right] . I(t)$$

$$P_{\text{cond},D} = \left[ V_{\text{on},D}(t) + R_D . I(t) \right] . I(t)$$

Von,T and Von,D are the ON-state voltage of the transistor and the diode, respectively. RT and RD are the equivalent resistance of the transistor and the diode, respectively. Moreover,  $\beta$  is a constant related to the specification of the transistor. In the proposed submultilevel topology, one IGBT and one diode of the bidirectional switches are in current path in any instant of time. It is noticeable that there is not a bidirectional switch in the highest level. Using (11)–(13), the average conduction power loss of the bidirectional switches of the proposed submultilevel structure Pcond,B is obtained as follows:

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 12 August 2016

Fig. 4. Required number of (a) NIGBTs; (b) Ndriver to realize Nlevel voltages in the proposed submultilevel and symmetric cascade converter.

#### B. 25-Level Proposed Cascade Topology

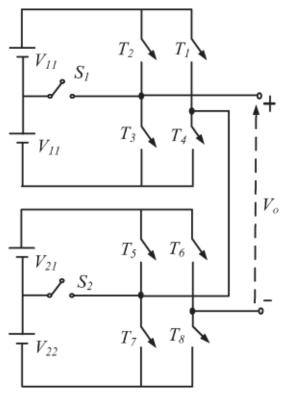

Fig.5 shows a 25-level structure according to the proposed cascade topology. It is noticeable that two lamps have been connected in parallel and the values of dc sources are V1 = 8 V and V2 = 40 V. Therefore, the maximum output voltage is 96 V. Fig. 25 shows the blocking voltage on S1, S2, (T1 - T4), and (T5 - T8) switches, which are 8, 40, 16, and 80 V, respectively. In addition, this figure indicates that the maximum blocked voltage by bidirectional switches depends on S2 switch, which is equal to 40 V. These results indicate that the theoretical

Fig.5. 25-level cascade converter. **III.INDUCTION MOTOR**

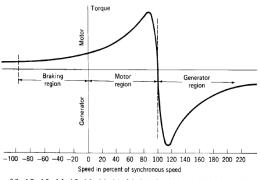

Induction Motor (1M) An induction motor is an example of asynchronous AC machine, which consists of a stator and a rotor. This motor is widely used because of its strong features and reasonable cost. A sinusoidal voltage is applied to the stator, in the induction motor, which results in an induced electromagnetic field. A current in the rotor is induced due to this field, which creates another field that tries to align with the stator field,

causing the rotor to spin. A slip is created between these fields, when a load is applied to the motor.

Compared to the synchronous speed, the rotor speed decreases, at higher slip values. The frequency of the stator voltage controls the synchronous speed [12]. The frequency of the voltage is applied to the stator through power electronic devices, which allows the control of the speed of the motor. The research is using techniques, which implement a constant voltage to frequency ratio. Finally, the torque begins to fall when the motor reaches the synchronous speed. Thus, induction motor synchronous speed is defined by following equation,

=

Where f is the frequency of AC supply, n, is the speed of rotor; p is the number of poles per phase of the motor. By varying the frequency of control circuit through AC supply, the rotor speed will change.

Fig.6.Speed torque characteristics of induction motor.

#### IV.MATLAB/SIMULATION RESULTS

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 12 August 2016

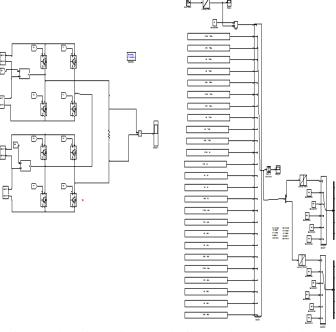

Fig.7.Matlab/Simulation model of the 25-level Caseded Converter.

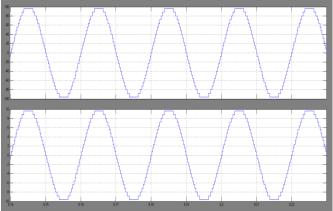

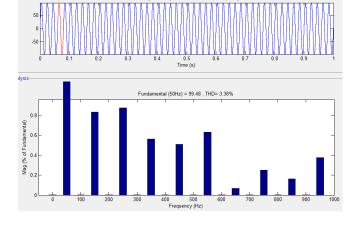

Fig.8.Output voltage and current of the caseded 25-level inverter.

Fig.9.THD for 25 level inverter voltage.

$\label{lem:fig.10.Matlab/Simulation Model of Three phase 25 level inverter with \\Induction Motor drive.$

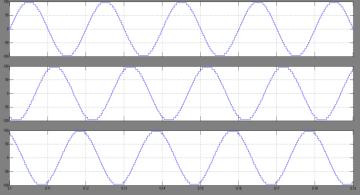

Fig.11.Three phase Inverter phase a,b,c voltages.

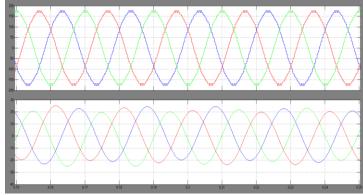

Fig.12.three phase voltage and current.

# International Journal of Research

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 12 August 2016

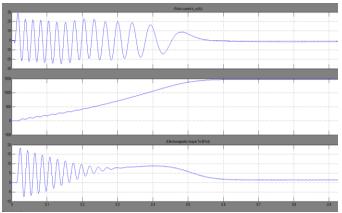

Fig.13. Armaturecurrent, speed and electromagnetic torque of the induction motor.

Figs.13.Shows the high performance inductionmachine drive characteristics Stator Current, Speed, Electromagnetic Torque respectively.

#### V.CONCLUSION

This paper presents Asymmetrical multilevel converter. The proposed converter produces more voltage levels with less number of switches compared to H- bridge configuration. This will reduce number of gate drivers and protection circuits which in turn reduces the cost and complexity of the circuit. Finally a three phase model of the proposed circuit is implemented to Induction Machine Drive for Optimizing the Characteristics of the Drive and check the performance of entire system are shown and simulation results are presented. THD also well within IEEE standards.

#### REFERENCES

- [1] J. Rodriguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [2] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high-power applications," IEEE Trans. Ind. Appl., vol. 36, no. 3, pp. 834–841, May/Jun. 2000.

- [3] Z. Du, B. Ozpineci, L. M. Tolbert, and J. N. Chiasson, "DC–AC cascaded H-bridge multilevel boost inverter with no inductors for electric/hybrid electric vehicle applications," IEEE Trans. Ind. Appl., vol. 45, no. 3, pp. 963–970, May/Jun. 2009.

- [4] G. Buticchi, D. Barater, E. Lorenzani, C. Concari, and G. Franceschini, "A nine-level grid-connected converter topology for single-phase transformerless PV systems," IEEE Trans. Ind. Electron., vol. 61, no. 8, pp. 3951–3960, Aug. 2014.

- [5] N. A. Azez, A. Dey, K. Mathew, and J. Mathew, "A medium-voltage inverter-fed IM drive using multilevel 12-sided polygonal vectors, with nearly constant switching frequency current hysteresis controller," IEEE Trans. Ind. Electron., vol. 61, no. 4, pp. 1700–1709, Apr. 2014.

- [6] W. Song and A. Q. Huang, "Fault-tolerant design and control strategy for cascaded H-bridge multilevel converter-based STATCOM," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2700–2708, Aug. 2010.

- [7] Y. Xiaoming and I. Barbi, "Fundamentals of a new diode clamping multilevel inverter," IEEE Trans. Power Electron., vol. 15, no. 4, pp. 711 718, Jul. 2000.

- [8] M. N. Abdul Kadir, S. Mekhilef, and H. W. Ping, "Dual vector control strategy for a three-stage hybrid cascaded multilevel inverter," J. Power Electron., vol. 10, no. 2, pp. 155–164, 2010.

- Power Electron., vol. 10, no. 2, pp. 155–164, 2010. [9] J. Hunag and K. Corzine, "Extended operation of flying capacitor multilevel inverters," IEEE Trans. Power Electron., vol. 21, no. 1, pp. 140 147, Jan. 2006.

- [10] K. K. Gupta and S. Jain., "A multilevel Voltage Source Inverter (VSI) to maximize the number of levels in output waveform," Elect. Power Energy Syst., vol. 44, no. 1, pp. 25–36, Jan. 2012.

- [11] Y.-S. Lai and F. S. Shyu, "Topology for hybrid multilevel inverter," Proc. Inst. Elect. Eng.—Electron. Power Appl., vol. 149, no. 6, pp. 449–458. Nov. 2002.

- [12] M. T. Haque, "Series sub-multilevel voltage source inverters (MLVSIs) as a high quality MLVSI," in Proc. SPEEDAM, 2004, pp. F1B-1–F1B-4.

- [13] E. Babaei, S. H. Hosseini, G. B. Gharehpetian, M. T. Haque, and M. Sabahi, "Reduction of DC voltage sources and switches in asymmetrical multilevel converters using a novel topology," J. Elect. Power Syst. Res., vol. 77, no. 8, pp. 1073–1085, Jun. 2007.