# International Journal of Research

### **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

## Design of Efficient 64-Bit Parallel PrefixBrentKung Adder

<sup>1</sup>JAKKULA RADHIKA, M.Tech., VLSI, E.C.E Dept., CMR INSTITUTE OF TECHNOLOGY,

Mr.P.PAVAN KUMAR, Assistant Professor, E.C.E Dept., CMR INSTITUTE OF TECHNOLOGY,

Dr. A. BALAJI NEHRU, Professor, E.C.E Dept, CMR INSTITUTE OF TECHNOLOGY.

ABSTRACT: A parallel-prefix adder gives the most excellent performance in VLSI design. However, performance of Brent-kung adder through black cell takes large area. So, gray cell can be replaced instead of black cell which gives the Efficiency inBrent-kungAdder. The proposed system hastwo stages of operations they are preprocessing stage and generation stage. The preprocessing stagehaving propagate generate.Generation stage focuses on generation and final result. In ripple carry adder each bit having addition operation is waited for the preceding bit addition operation. In efficient Brent - Kungadder, addition operation does not wait for preceding bit addition operation and modification is done at gate level toimprove the speed and decreases the area.

INDEX TERMS: Ripple carry adder, EfficientBrent-Kung adder, Black cell, Gray cell

#### **I INTRODUCTION**

Ripple carry adder is used for the addition task i.e., if N-bits addition operation is performed by the full adder with N- bits. In ripple carry adder each full adder operation consists of sum and carry, that carry will be given to next bit full adder operation, that processes is continuous till the N<sup>th</sup> bit operation. The N-1<sup>th</sup> bit full adder operation carry will be given to the N<sup>th</sup> bit full adder operation present in the ripple carry adder. [1]

Addition procedure is the main process in digital signal processing and control systems. The high-speed and accuracy of a processor or system depends on the adder performance. Multiplexer is combinational circuit which consists of multiple inputs and a single output. In general purpose processors and DSP processors the addition

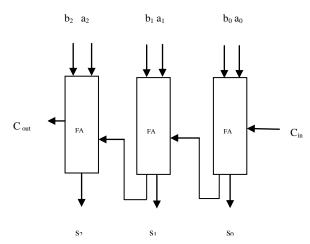

The 3-bit ripple carry adder is shown in Fig.1. The first bit carry is given to second bit full adder and similarly the second bit carry is given to the third bit full adder. The addition process is performed from least significant bit to most significant bit in ripple carry adder[1]. Configuration logic and routing resources in FieldProgrammable Gate Array.

Fig.1: Three Bit Ripple Carry Adder

#### II BRENT-KUNG ADDER

BrentKung adder is used for high performance addition operation. The Brentkung is the parallel prefix adder used to perform the addition operation [3]. It is looking like tree structure to perform the arithmetic operation. The Brent-kung adder consists of black cells and gray cells. [2] Each black cell consists of two AND gates and one OR gate [4]. Each gray cell consists of only one AND gate.p<sub>i</sub> denotes propagate and it consists of only one AND gate[5] given in equation 1. g<sub>i</sub> denotes generate and it consists of one AND gate and OR gate given in equation 2. [6]

## **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

$$p_i = A_i \text{ XOR } B_i \text{ -----} (1)$$

$$g_i = A_i \text{ AND } B_i -----(2)$$

G<sub>i</sub> denotes carry generate and it consists of one AND gate and OR gate given in equation 3 used for first black cell. [8]

$$G_i=p_i OR [g_i AND c_{in}] --- (3)$$

#### **IIIPROPOSED BRENTKUNG ADDER**

The proposed Brent-kung adder is flexible to speed up the binary addition and the arrangementlooks like tree structure for the high performance of arithmetic operations.

Field programmable gate arrays [FPGA's] are mostly used in recent years because they improve the speed of microprocessor based applications like mobile communication, DSP and telecommunication. Research on binary operation fundamentals and motivation gives development of devices. The construction of efficientBrent-kung adder consists oftwo stages. They are preprocessing stage and generation stage.

#### **Pre-Processing Stage:**

In the pre-processing stage, generate and propagate are from each pair of the inputs. The propagate gives "XOR" operation of input bits and generates gives "AND" operation of input bits [7]. The propagate  $(P_i)$  and generate  $(G_i)$  are shown in below equations 4 & 5.

$$P_i=A_i XOR B_i$$

----- (4)

$$G_i=A_i$$

AND  $B_i$  ----- (5)

#### **Generation Stage:**

In this stage, carry is generated for each bit is called carry generate ( $C_g$ ) and carry is propagate for each bit is called carry generate ( $C_p$ ). The carry propagate and carry

generate is generated for the further operation, final cell present in the each bit operate gives carry. The last bit carry will help to sum of the next bit simultaneously till the last bit. The carry generate and carry propagate are given in below equations 6 & 7.

$$C_p = P_1 \text{ AND } P_0 - (6)$$

$$C_g = G_1 \text{ OR } (P_1 \text{ AND } G_0) ----- (7)$$

The above carry propagate  $C_p$  and carry generation  $C_g$  in equations 6&7 is black cell and the below shown carry generation in equation 8 is cell i.e., gray cell. The carry propagate is generated for the further operation. The final cell present in the each bit operation gives carry. The last bit carry will lead tosum of the next bit simultaneously till the last bit. This carry is used for the next bit sum operate, the carry generate is given in below equations 8.

$$C_g = G_1 \text{ OR } (P_1 \text{ AND } G_0) ----- (8)$$

The carry of a first bit is XORed with the next bit of propagates then the output is given as sum and it is shown in equation 9.

$$S_i=P_i \text{ XOR } C_{i-1}$$

----- (9)

It is used for two thirty-two bit addition operations and each bit undergoes preprocessing stage and generation stage then gives the final sum.

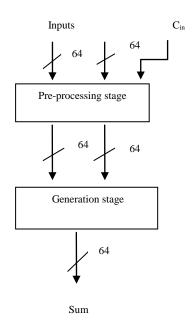

The first input bits goes under preprocessing stage and they will produce propagate and generate. These propagates and generates undergoes generation stage produces carry generates and carry propagates then gives final sum. The step by step process of efficientBrent-kung adderis shown in Fig.2.

## arch

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

Fig.2: Block Diagram

The efficient Brent-kungadder arrangement is looking like tree structure for the high performance of arithmetic operations and it is the high speed adder which focuses on gate level logic. It designs with a reduction of number of gates. So, it decreases the delay and memory used in this architecture.

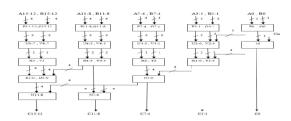

The efficient Brent-kung adder is shown in fig.3 which improves the speed and decrease the area for the operation of 16-bit addition. The input bits A<sub>i</sub> and B<sub>i</sub> concentrates on generate and propagate by XOR and AND operations respectively. The propagates and generates undergoes the operations of black cell and gray cell and gives the carry C<sub>i</sub>. That carry is XORed with the propagate of next bit, that gives sum.

The properties of the operations are evaluated in parallel with accept the trees to overlap which leads to parallelization. The architecture of Efficient Brent-kung adder gives the less delay and less memory for the operation of 16-bit addition.

Fig.4: 64-bit Efficient Brent-kung Adder

The architecture of 64-bit Efficient Brent-kung adder is shown in Fig.4. The logical circuit is using multiple adders to find the ans i.e., sum of N-bit numbers. Each addition operation has a carry input  $(C_{in})$  which is the previous bit carry output  $(C_{out})$ .

Research on binary addition innovatively motivates gives development of devices. Many parallel prefix networks describe the literature of parallel addition operation. The parallel prefix adders are Brent-kung, Kogge-stone, brent-kung, Sklansky, etc., The fast and accurate performance of an adder gives toused in the very large scale integrated circuits design and digital signal processors.

#### IV SIMULATION RESULTS

The Efficient Brent-kung adder is design with an VHDL (very high speed integration hardware description language). Xilinx project navigator 14.1 is used and Simulation results of 16-bit efficient Brent-kungare shown in Fig.5.

Fig.5: 16-

Fig.6: 64-

Fig.3: 16-Bit Efficient Brent-kung Adder

Available online: http://internationaljournalofresearch.org/

## arch

### **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

The architecture of 64-bit Efficient Brentkung adder is shown in Fig.4 and the Simulation results is shown in Fig.6.

The design of adders is done on VHDL. The memory and delay performance Efficient Brent-kungadder (EBK) is shown in Table.1

| Adder      | Delay(ns) | Memory used(MB) |

|------------|-----------|-----------------|

| 8-bit      | 11.0      | 101             |

| Efficient  | 11.2      | 181             |

| Brent-kung |           |                 |

| adder      |           |                 |

| 16-bit     |           |                 |

| Efficient  | 12.2      | 184             |

| Brent-kung |           |                 |

| adder      |           |                 |

| 64-bit     |           |                 |

| Efficient  | 13.275    | 208.9           |

| Brent-kung |           |                 |

| adder      |           |                 |

Table.1: Delay and memory used in EBK

#### **V CONCLUSION**

In this paper, new approaches to design an efficient Brent-kung adder look like tree structure and cells in the carry generation stage are decreased to speed up the binary addition. It concentrates on gate levels to perk upthe speed and decreases the memory used. The proposed adder addition operation

offers elude great advantage in reducing delay.

#### REFERENCES

- [1] Pakkiraiah chakali, madhu kumar patnala "Design of high speed Brent Kung based carryselect adder" IJSCE march 2013

- [2] David h,k hoe, Chris Martinez and sri jyothsna vundavalli "Design and characterization of parallel prefix adders using FPGAs", Pages.168- 172, march2011 IEEE.

- [3] K.Vitoroulis and A.J. Al-Khalili, "performance of parallel prefix adders implemented with FPGA technology," IEEE Northeast Workshop on circuits and systems, pp.498-501, Aug. 2007.

- [4] Haridimos t.vergos, Member, IEEE and Giorgos Dimitrakopoulos, Member, IEEE,"On modulo 2<sup>n</sup>+1 adder design"IEEE Trans on computers, vol.61, no.2, feb 2012

- [5] Giorgos Dimitrakopoulos and Dimitris Nikolos, "High-Speed Parallel-Prefix VLSI Ling Adders" IEEE Trans on computers, vol.54, no.2, Feb. 2005.

- [6] S.Knowles, "Afamily of adders," Proc. 15 Symp. Comp. Arith., pp. 277-281, June 2001.

- [7] R.BrentandH.Kung, "Aregular layout for parallel adders," IEEE Trans. Computers, vol. C-31,no.3, pp. 260-264, March 1982.

- [8] R.E. Brent and M.J. Kung, "Parallel Prefix Computation," J. ACM, vol. 27, no. 4, pages 831-838, Oct. 1980.