### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

## An Area Efficient Multiplier Design Using Fixed-Width Replica Redundancy

### Syamala Tejas Reddy

Student\*, Department of ECE, Nimra Institute of Science & Technology, Andhra Pradesh.

### P Omsan

M.Tech(Ph.D), Department of ECE, Nimra Institute of Science & Technology, Andhra Pradesh.

Abstract: In this paper, proposedAn Area Efficient Multiplier Design Using Fixed-Width Replica Redundancy by adopting algorithmic noise tolerant (ANT) architecture with the fixed-width multiplier to build the reduced precision replica redundancy block (RPR). The proposed ANT architecture can meet the demand of high precision, low power consumption, and area efficiency. We design the fixed-width RPR with error compensation circuit via analysing of probability and statistics. Using the partial product terms input of correction vector and minor input correction vector to lower the truncation errors. hardware error compensation complexity of circuit can be simplified. In a  $16 \times 16$  bit ANT multiplier, circuit area in our fixed-width RPR can be lower and power consumption in our ANT design can be saved as compared with the state-of-art ANT design.

Key words: Algorithmic noise tolerant (ANT), fixed-width multiplier, reduced-precision replica (RPR), voltageoverscaling(VOS),error tolerant adder(ETA),main digital signal processing(MDSP).

### I. INTRODUCTION

Rapid growth of portable and wireless computing systems in recent years drives

Available online: <a href="http://internationaljournalofresearch.org/">http://internationaljournalofresearch.org/</a>

the need for ultralow powersystems. To lower the power dissipation, supplyvoltage scaling [1] is widely used as an effective low-power technique since the power consumption in **CMOS** circuits proportional to the square of supply voltage. deep-However, submicrometerprocess technologies, noise interference problems have raised difficulty to design the reliable and efficient microelectronics systems; hence, the design techniques to enhance noise tolerance have been widely developed [2]-[8]. An aggressive low-power technique, referred to as voltage over scaling (VOS), was proposed in lower supply voltage beyond critical supply voltage without sacrificing the throughput. However, VOS leads to severe degradationin signal-tonoise ratio (SNR). A novel algorithmic noise tolerant (ANT) technique combined VOS main block with reduced-precision replica (RPR), which combats softerrors effectively while achieving significant energy saving. Some ANT deformation designs are presented in [5]-[9]the ANT design concept is further extended to system level. However, the RPR designs in the ANT are in a customized manner, which are not easily adopted and repeated. The RPR designs in the ANT designs can operate in a very fast manner, but their hardware complexity is too complex. As a

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

result, the RPR design in the ANT design is still the most popular design because of its simplicity. However, adopting with RPR should still pay extra area overhead and power consumption. In this paper, we further proposed an easy way using the fixed-width RPR to replace the full-width RPR block. Using the fixed-width RPR, the computation error can be corrected with lower power consumption and lower area overhead. We take use of probability, and partial product weight statistics, find analysis the approximate compensation vector for a more precise RPR design. In order not to increase the path delay, we restrict the compensation circuit in RPR must not be located in the critical path. As a result, we can realize the ANT design with smaller circuit area, lower power consumption, and lower critical supply voltage.

Fig1: ANT architecture

II.PROPOSEDANT

MULTIPLIER DESIGN

USING FIXED-WIDTH RPR

In this paper, we further proposed the fixed-width RPR toreplace the full-width RPR block in the ANT design [2], as shown in Fig.2, which can not only provide higher computation precision, lower power consumption, and lower area overhead in RPR, but also perform with higher SNR, more area efficient, lower operating supply voltage, and lowerpower consumption in realizing the ANT architecture. We demonstrate our fixed-

width RPR-based ANT design in an ANT multiplier. The fixed-width designs are usually applied in DSP applications to avoid infinite growth of bit width. Cutting off *n*-bit least significant bit (LSB) output is a popular solution to construct a fixedwidth DSP with *n*-bit input and *n*-bit output. The hardware complexity and power consumption of a fixed-width DSP is usually about half of the full-length one. However, truncation of LSB part results in which needsto rounding error, be compensated precisely. Many literatures have been presented to reduce truncation error with constant correction value with variable correction value. The circuit complexity to compensate with constant corrected value can be simpler than that of variable correction value; however. the variable correction approaches are usually more precise, their compensation method is to compensate the truncation error between the full-length multiplier andthe fixed-width multiplier. However, in the fixed-width RPR of an ANT multiplier, the compensation error we need to correct is the overall truncation error of MDSP block. Unlike, compensation method is to compensate the truncation error between the full-length MDSP multiplier and the fixed-width RPR multiplier. In nowadays, there aremany fixed-width multiplier designs applied to the full-width multipliers.

Fig2: Proposed ANT Architecture with fixed width RPR.

### **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

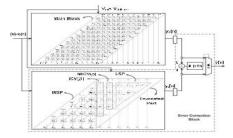

However, there is still no fixedwidth RPR design applied to the ANT multiplier designs. To achieve more precise compensation, error we compensate the truncation error with variable correction value. We construct the error compensation circuit mainly using the partial product terms with the largest weight in the least significantsegment. The error compensation algorithm makes use ofprobability, statistics, and regression analysis to findthe approximate compensation value [16]. To hardwarecomplexity, the compensation vector in the partial productterms with the largest weight in the least significant segmentis directly inject into the fixedwidth RPR, which does notneed extra compensation logic gates [17]. To further lower thecompensation error, we also consider the impact of truncated products with the second most significant bits on the errorcompensation. We propose an error compensation circuit using a simple minor input correction vector to compensation theerror remained. In order not to increase the critical path delay,we locate the compensation circuit in the noncritical path of the fixed-width RPR. As compared with the full-width RPRdesign in [15], the proposed fixed-width RPR multiplier notonly performs with higher SNR but also with lower circuitryarea and lower power consumption.A Proposed Precise Error Compensation Vector forFixed-Width RPR DesignIn the ANT design, the function of RPR is to correct theerrors occurring in the output of MDSP and maintain the SNRof whole system while lowering supply voltage. In the caseof using fixed-width RPR to realize ANT architecture, wenot only lower circuit area and power consumption, butalso accelerate the computation speed as compared with

theconventional full-length RPR. However, we need to compensatehuge truncation error due to cutting off many hardwareelements in the LSB part of MDSP.In the MDSP of *n*-bit ANT Baugh— Wooley array multiplier, its two unsigned *n*-bit inputs of X and Y can be expressed ashe (n/2)-bit unsigned full-width Baugh-Wooley partial product array can be divided into four subsets, which are mostsignificant (MSP), input part correction vector [ICV(B)].

Fig3:  $16 \times 16$  bit ANT multiplier is implemented with the 8-bit fixed width Replica redundancy block.

# III. APPLICATION OF ERROR TOLERANT ADDER IN DIGITAL SIGNAL PROCESSING

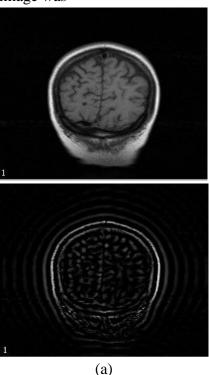

In image processing and many other DSP applications, fast Fourier transformation (FFT) is a very important function. The computational process of FFT involves a large number of additions and multiplications. It is therefore a good platform for embedding our proposed ETA. To prove the feasibility of the ETA, we replaced all the common additions involved in a normal FFT algorithm with our proposed addition arithmetic. As we all know, a digital image is represented by a matrix in a DSP system, and each element of the matrix represents the color of one pixel of the image. To compare the quality of images processed by both the

### **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

conventional FFT and the inaccurate FFT that had incorporated ourproposed ETA, we devised the following experiment. An image was

# Fig4: Images after FFT and inverse FFT. (a) Image processed with conventionalmultiplier and (b) image processed with the proposed multiplier.

first translated to a matrix form and sent through a standard system that made used of normal FFT and normal reverse FFT. The matrix output of this system was then transformed back to an image and presented in Fig. The matrix of the same image was also processed in a system that used the inaccurate FFT and inaccurate reverse FFT. where both FFTs incorporated the 16-bit multiplier described in Section, with the processed image given in Fig. 4(b). Although the two resultant matrices of the same image were different, the two pictures obtained (see Fig.4) look almost the same. Fig.4 (b) is slightly darker and contains horizontal bands of different shades of grey.

### IV.SIMULATION RESULTS

Fig: Array Multiplier Output Result

Fig: Fixed Width Multiplier Output Result

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

Fig: top module output result

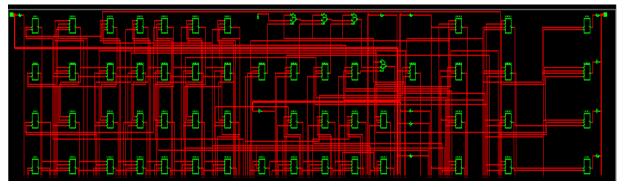

#### V. SYSTHESIS RESULTS

Fig: Internal schematic

| Device Utilization Summary (estimated values) |      |           |             | Ŀ   |

|-----------------------------------------------|------|-----------|-------------|-----|

| Logic Utilization                             | Used | Available | Utilization |     |

| Number of Slices                              | 120  | 4656      |             | 2%  |

| Number of 4 input LUTs                        | 213  | 9312      |             | 2%  |

| Number of bonded IOBs                         | 47   | 232       |             | 20% |

**Fig: Device Utilization Summary**

### VI. CONCLUSION

In this paper, the concept of error tolerance is introduced in VLSI design. A novel type of adder, the error-tolerant adder, which trades certain amount of accuracy for significant power saving and performance improvement, is proposed. Extensive comparisons conventionaldigital adders showed that the proposed multiplier outperformed the conventional adders in both power consumption and speed performance. The potential applications of the multiplier fall mainly in areas where there is no strict requirement on accuracy or where

superlow power consumption and highspeed performance are more important than accuracy. One example of such applications is in the DSP application for portable devices such as cell phones and laptops.

### REFERENCES

- [1] A. B. Melvin, "Let's think analog," in *Proc. IEEE Comput. Soc. Annu.Symp. VLSI*, 2005, pp. 2–5.

- [2] International Technology Roadmap for Semiconductors [Online]. Available: <a href="http://public.itrs.net/">http://public.itrs.net/</a>

- [3] A. B. Melvin and Z. Haiyang, "Errortolerance and multi-media," in *Proc.* 2006

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 13 September 2016

- Int. Conf. Intell. Inf. Hiding and Multimedia SignalProcess., 2006, pp. 521–524.

- [4] M. A. Breuer, S. K. Gupta, and T. M. Mak, "Design and error-tolerancein the presence of massive numbers of defects," *IEEE Des. TestComput.*, vol. 24, no. 3, pp. 216–227, May-Jun. 2004.

- [5] M. A. Breuer, "Intelligible test techniques to support error-tolerance," in *Proc. Asian Test Symp.*, Nov. 2004, pp. 386–393.

- [6] K. J. Lee, T. Y. Hsieh, and M. A. Breuer, "A novel testing methodologybased on error-rate to support error-tolerance," in *Proc. Int. Test Conf.*,2005, pp. 1136–1144.

- [7] I. S. Chong and A. Ortega, "Hardware testing for error tolerant multimediacompression based on linear transforms," in *Proc. Defect andFault Tolerance in VLSI Syst. Symp.*, 2005, pp. 523–531.[8] H. Chung and A. Ortega, "Analysis and testing for error tolerant motionestimation," in *Proc. Defect and Fault Tolerance in VLSI Syst. Symp.*,2005, pp. 514–522.

- [9] H. H. Kuok, "Audio recording apparatus using an imperfect memorycircuit," U.S. Patent 5 414 758, May 9, 1995.

- [10] T. Y. Hsieh, K. J. Lee, and M. A. Breuer, "Reduction of detected acceptable faults for yield improvement via error-tolerance," in *Proc.Des.*, *Automation and Test Eur. Conf. Exhib.*, 2007, pp. 1–6.

- [11] K. V. Palem, "Energy aware computing through probabilisticswitching: A study of limits," *IEEE Trans. Comput.*, vol. 54, no. 9, pp.1123–1137, Sep. 2005.

- [12] S. Cheemalavagu, P. Korkmaz, and K. V. Palem, "Ultra low energycomputing via probabilistic algorithms and devices: CMOS deviceprimitives and the energy-

- probability relationship," in *Proc.* 2004 Int.

- Conf. Solid State Devices and Materials, Tokyo, Japan, Sep. 2004, pp.402–403.

- [13] P. Korkmaz, B. E. S. Akgul, K. V. Palem, and L. N. Chakrapani, "Advocating noise as an agent for ultra-low energy computing: Probabilistic complementary metal-oxide-semiconductor devices and their characteristics," *Jpn. J. Appl. Phys.*, vol. 45, no. 4B, pp. 3307–3316, 2006.

- [14] J. E. Stine, C. R. Babb, and V. B. Dave, "Constant addition utilizingflagged prefix structures," in *Proc. IEEE Int. Symp. Circuits and Systems(ISCAS)*, 2005.

- [15] L.-D. Van and C.-C. Yang, "Generalized low-error area-efficient fixedwidthmultipliers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 25,no. 8, pp. 1608–1619, Aug. 2005.

- [16] M. Lehman and N. Burla, "Skip techniques for high-speed carry propagationin binary arithmetic units," *IRE Trans. Electron. Comput.*, vol.EC-10, pp. 691–698, Dec. 1962.

- [17] O. Bedrij, "Carry select adder," *IRE Trans. Electron. Comput.*, vol.EC-11, pp. 340–346, 1962.

- [18] O. MacSorley, "High speed arithmetic in binary computers," *IRE Proc.*,vol. 49, pp. 67–91, 1961.

- [19] Y. Kiat-Seng and R. Kaushik, *Low-Voltage*, *Low-Power VLSI Subsys-tems*. New York: McGraw-Hill, 2005.