Available at <a href="https://edupediapublications.org/jourr">https://edupediapublications.org/jourr</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

# Comparative Analysis of reduced switches MLI with Cascaded H-bridge Multi-level inverter

#### <sup>1</sup>P. RAVI TEJA & <sup>2</sup>B.N.CH.V.CHAKRAVARTHI

<sup>1</sup>M-Tech, Dept.:- ELECTRICAL POWER ENGINEERING, VISHNU INSTITUTE OF TECHNOLOGY, BHIMAVARAM, AP.

<sup>2</sup>ASSISTANT PROFFESOR (PHD), Dept.:-ELECTRICAL AND ELECTRONICS ENGINEERING, VISHNU INSTITUTE OF TECHNOLOGY, BHIMAVARAM, AP.

Abstract: Recently, the evolution of single phase multilevel inverters has been escalation due to its preference over traditional one. This paper represents the Cascaded H bridge multi-level inverter implemented with the pulse width modulation techniques and the multilevel inverter with the reduced number of switches. The Multilevel inverter performance is high compared to the conventional two level inverters due to their reduced harmonic distortion and less amount electromagnetic interference. In this scenario, Cascaded H Bridge MLI is preferred and the performance of the inverter can be improved by using different pulse width modulation techniques. The main disadvantage of the Cascaded MLI is complexity, requiring a great number of power devices and passive components, and a rather complex control circuitry. So in order to overcome the complexity nature the reduced switches multi-level inverters are proposed in this paper. So that the topology [1] and the proposed topology multi-level inverters are compared with the Cascaded H bridge MLI. These methods are modelled by using the MATLAB/SIMULINK and the THD of these inverters are compared.

**Index Terms -** cascade inverter, multilevel, PWM, and THD.

## 1. INTRODUCTION

The voltage source inverters produce an output voltage or current with levels either 0 or ±Vdc. They are known as the two-level inverter. To produce a quality output voltage or a current wave form with less amount of ripple content, they require high switching frequency. In high- power and high voltage applications these two level inverters, however, have some limitations in operating at high frequency mainly due to switching losses and constraints of

device ratings. These limitations can be overcome using multilevel inverters. There are 3 types of multilevel inverters named as diode clamped multilevel inverter, flying capacitor multilevel inverter and cascaded multilevel inverter. These three types of multilevel inverters require more no. of components such as switches, clamping diodes and capacitors. As the number of voltage levels m grows the number of active switches increases according to  $2\times(m-1)$  for the cascaded H-

Available at https://edupediapublications.org/jourr

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

bridge multilevel inverters. Multilevel inversion is a power conversion strategy in which the output voltage is obtained in steps thus bringing the output closer to a sine wave and reduces the total harmonic distortion (THD).

# II. CASCADED H-BRIDGE **INVERTER**

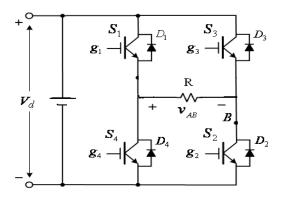

The cascade H-bridge inverter is a cascade of H-bridges, or H-bridges in a series configuration. A single H-bridge inverter is shown in fig (1) and three phase cascaded H-bridge inverter for seven-level inverter is shown in fig (2). Fig (1) and fig (2) shows the basic power circuit of single H-bridge inverter and the cascade of Hbridge inverter for seven-level inverter respectively. An N level Cascaded H bridge inverter consists of series connected (N-1)/2 number of cells in each phase. Each cell consists of single phase H bridge inverter with separate dc source. There are four active devices in each cell and can produce three levels 0, Vdc/2 and -Vdc/2. Higher voltage levels can be obtained by connecting these cells in cascade and the phase voltage Van is the sum of voltages of individual cells.

$$Van = V1 + V2 + V3 + :::: + Vn.$$

Fig.1 Configuration of single-phase Hbridge inverter

Cascaded Seven Level H-Bridge Inverter

A three-phase CMI topology is essentially composed of three identical phase legs of the series-chain of H-bridge converters, which can possibly generate different output voltage waveforms and offers the potential for AC system phasebalancing. A series of single-phase full bridges makes up a phase for the inverter.

For real power conversions, (ac to dc and dc to ac), the cascaded-inverter needs separate dc sources. The structure of separate dc sources is well suited for

e-ISSN: 2348-795X Volume 03 Issue 14

Available at <a href="https://edupediapublications.org/jourr">https://edupediapublications.org/jourr</a> October2016

p-ISSN: 2348-6848

various renewable energy sources such as fuel cell, photovoltaic, and biomass, etc.

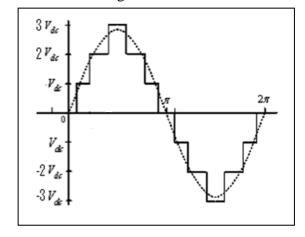

Fig.3 Output wave form of single phase 7 level cascaded inverter

The output wave form of the seven level inverter is shown in the fig.3.As the amount of levels increases in the inverter there is a possibility of the occurrence of the sinusoidal output. The multi-level output is more accurate and as the number of levels increases the smooth waveform

Table.1 Switching sequence for 1–Φ7 level Cascade inverter

The table 1 shows the switching pattern of the 7 level Cascaded MLI.

## III. MODULATION TECHNIQUES:

There are different control techniques available for a CHB MLI [13, 15]. Among all those techniques, PWM control technique which produces less total harmonic distortion (THD) values is most preferable.

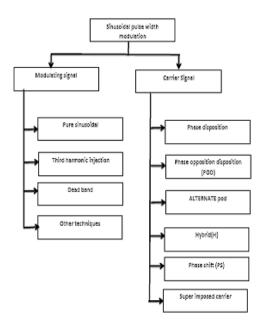

Fig.4 Control Techniques for a Cascaded H-Bridge MLI

| Output  | S1 | S2 | <b>S</b> 3 | S4 | S5 | <b>S</b> 6 | S7 | <b>S</b> 8 | <b>S</b> 9 | S10 | S11 | S12 |

|---------|----|----|------------|----|----|------------|----|------------|------------|-----|-----|-----|

| voltage |    |    |            |    |    |            |    |            |            |     |     |     |

| -3Vdc   | 0  | 1  | 1          | 0  | 0  | 1          | 1  | 0          | 0          | 1   | 1   | 0   |

| -2Vdc   | 0  | 1  | 1          | 0  | 0  | 1          | 1  | 0          | 1          | 1   | 0   | 0   |

| -Vdc    | 0  | 1  | 1          | 0  | 1  | 1          | 0  | 0          | 1          | 1   | 0   | 0   |

| 0Vdc    | 1  | 0  | 1          | 0  | 1  | 0          | 1  | 0          | 1          | 0   | 1   | 0   |

| Vdc     | 1  | 0  | 0          | 1  | 0  | 0          | 1  | 1          | 0          | 0   | 1   | 1   |

| 2Vdc    | 1  | 0  | 0          | 1  | 0  | 0          | 1  | 1          | 1          | 0   | 0   | 1   |

| 3Vdc    | 1  | 0  | 0          | 1  | 1  | 0          | 0  | 1          | 1          | 0   | 0   | 1   |

Available at <a href="https://edupediapublications.org/jourr">https://edupediapublications.org/jourr</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

Fig.5 Classification of Sinusoidal PWM

In PWM technique also, sinusoidal PWM is used for generating triggering pulses to MLI. In sinusoidal PWM pure sinusoidal wave as modulating signal and multi carrier signal which is of triangular in shape have been considered. For an m-level MLI, (m-1) carrier signals are required. Multi carrier PWM techniques have sinusoidal signal as reference wave and triangular as carrier signals

Amplitude Modulation

Ma = Am/Ac(m-1)

Frequency Modulation

Mf= Fc/Fr

Ma = Amplitude of modulation wave

Mf = Amplitude of carrier wave

Fc = Frequency of carrier wave

Fr = Frequency of Reference wave

In this topology we use the carrier wave modulation technique and sinusoidal modulation technique for the 7 level cascaded h bridge multi-level inverter and the THD value is calculated and compared with the proposed topology

The THD value of the 7 level cascaded H bridge inverter implemented with carrier wave modulation technique is 18,16%

## IV TOPOLOGY[1]:

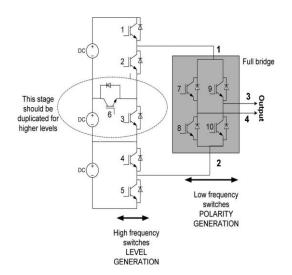

Fig.6 Configuration of Topology[1]

Here

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

The topology[1] shown in the fig 6 is a hybrid multilevel topology separates the output voltage into two parts. One part is named level generation part and is responsible for level generating in positive polarity. This part requires highfrequency switches to generate required levels. The switches in this part high-switching-frequency should have capability .The other part is called *polarity* generation part and is responsible for generating the polarity of the output voltage, which is the low-frequency part operating at line frequency.

| S.NO | LEVEL  | DC INPUT |

|------|--------|----------|

|      | NUMBER | VOLTAGES |

| 1    | 7      | E,E,E    |

| 2    | 9      | E,2E,E   |

| 3    | 11     | E,2E,2E  |

| 4    | 13     | E,3E,2E  |

The topology[1] uses isolated dc supplies. Therefore, it does not voltage-balancing problems due to fixed dc voltage values Switching sequences in this converter are easier than its counter parts. According to its inherent advantages, it does not need to generate negative pulses for negative cycle control. Thus, there is no need for extra conditions for controlling the negative voltage. Instead, the reversing full-bridge converter performs this task, and the required level is produced by the high-switching-frequency component of the inverter. Then, this level is translated to negative or positive according to output voltage requirements.

One of the promising advantages of the topology[1] is that it requires less highswitching-frequency components. Highswitches frequency and diodes expensive and are more prone to be damaged than low-frequency switches.As the number of high-frequency switches is increased, the reliability of the converter is decreased. It can clearly be inferred that the number of components of the topology[1] is lower than that of other topologies even more so as the voltage levels increase and it will decrease tremendously with higher voltage levels.

## IV PROPOSED TOPOLOGY:

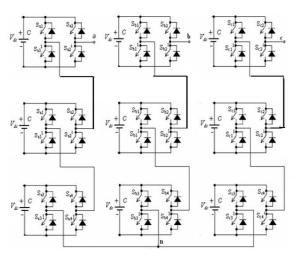

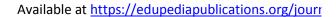

Fig7: Three phase pattern of the proposed topology

Available at https://edupediapublications.org/jourr

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

The 7 level Inverter is designed with the less number of switches such that the complexity nature of the inverter reduces which in turn improves the output waveform of the system.

Table.2 List of DC input voltages to voltage levels

| Level    | Switching Pattern |    |            |    |    |            |    |    |

|----------|-------------------|----|------------|----|----|------------|----|----|

| Voltages | <b>S</b> 1        | S2 | <b>S</b> 3 | S4 | S5 | <b>S</b> 6 | S7 | S8 |

| +3E      | 1                 | 0  | 0          | 1  | 1  | 0          | 0  | 1  |

| +2E      | 1                 | 0  | 0          | 1  | 1  | 0          | 1  | 0  |

| +E       | 1                 | 0  | 0          | 1  | 0  | 1          | 0  | 1  |

| 0        | 1                 | 0  | 1          | 0  | 1  | 0          | 1  | 0  |

| -E       | 0                 | 1  | 1          | 0  | 1  | 0          | 1  | 0  |

| -2E      | 0                 | 1  | 1          | 0  | 0  | 1          | 0  | 1  |

| -3E      | 0                 | 1  | 1          | 0  | 0  | 1          | 1  | 0  |

To obtain number of levels at the output side the values of DC sources has to consider as per Table 2. The proposed topology can easy to develop as compared to the cascaded H-bridge multilevel inverters and THD also reduced as compared to the cascade inverters.

Table.3 Switching pattern of the 7 level inverter

The switching pattern of the 7 level proposed topology is as follows such that the level outputs of the inverter are obtained.

The switching pattern for 7-level inverter is tabulated in the Table 3 indicates switch is in ON position, 0 indicates switch is in OFF position. From the below table the gate pulses are evaluated for each switch.

#### **V SIMULATION RESULTS:**

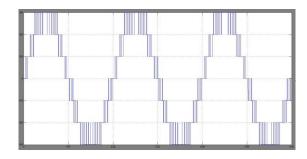

The simulation results of the 7 level cascaded H bridge inverter by using the carrier wave pulse width modulation technique and the topology[1] along with the simulation results of the proposed topology are shown below.

## Cascaded 7 level MLI:

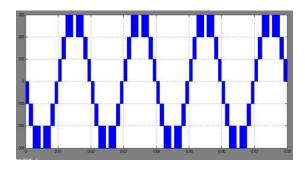

Fig8: Output voltage of the 7 level Cascaded MLI

(carrier pulse width modulation)

## Topology[1]:

Available at <a href="https://edupediapublications.org/jourr">https://edupediapublications.org/jourr</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

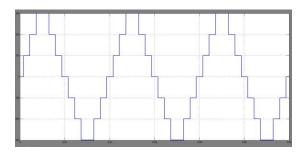

Fig7: Output Voltage of the 7 level Topology[1]

# **Proposed Topology:**

Fig8: Output voltage of the proposed topology

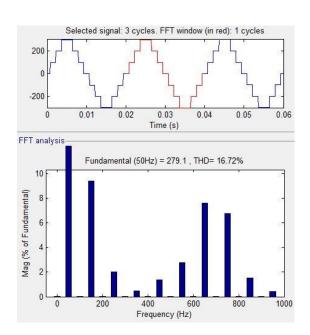

The output voltages of the multilevel inverters are shown above. The FFT analysis of the cascaded MLI and the Asymmetrical MLI are also compared which gives the THD value of both the inverters.

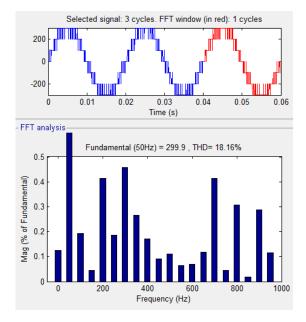

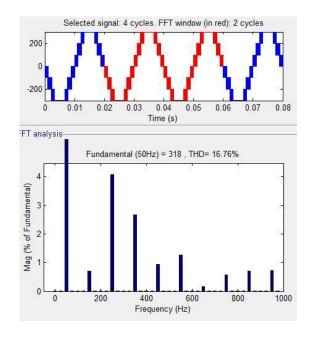

## **FFT ANALYSIS:**

The FFT Analysis shows the level of reduction of the harmonic content in the inverters ie the harmonics are measured in the form of the Total Harmonic Distortion (THD).

Fig9: FFT Analysis of the 7 level new topology MLI

Fig10: FFT Analysis of the topology[1] (Carrier wave modulation)

Available at https://edupediapublications.org/jourr

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

Table 5: THD Comparison

## **Proposed Topology:**

Fig11: FFT Analysis of the Proposed MLI

From the above FFT Analysis the THD value of the cascaded H bridge inverter is 18.16% which is reduced to 16.78% by using the topology[1] which gets reduced to 16.72% by using the proposed topology.

| Inverter type        |                     | Diode-<br>clamp | Flying<br>capacitor | CHBMLI   | Topology[1] | Proposed<br>Topology |

|----------------------|---------------------|-----------------|---------------------|----------|-------------|----------------------|

| Main<br>switching    | switching frequency |                 | (M-1)× 2            | (M-1)× 2 | (M-1)       | (M+1)                |

| devices              | Low<br>frequency    | 0               | 0                   | 0        | 4           | 0                    |

| Main diodes          |                     | (M-1)×2         | (M-1)×2             | (M-1)×2  | (M-1)+4     | (M+1)                |

| Clamping Diodes      |                     | (M-1)×<br>(M-2) | 0                   | 0        | 0           | 0                    |

| DC bus Capacitors    |                     | (M-1)           | (M-1)               | (M-1)/2  | 0           | 0                    |

| Balancing Capacitors |                     | 0               | (M-1)×<br>(M-2)/2   | 0        | 0           | 0                    |

Table 4: Comparison of different MLI

| Inverter type | CHBMLI | Topology[1] | Proposed Topology |

|---------------|--------|-------------|-------------------|

| THD           | 18.23% | 16.76%      | 16.72%            |

By which we can say that the value of THD gets reduced from 18.16% to 16.72% by using the proposed topology than the Cascaded multi level inverter

## VI CONCLUSION:

The simulations of the seven-level Cascaded H bridge inverter, topology[1] and proposed topology[1] are successfully executed by using multi carrier pulse width modulation technique..The reduction of THD values are shown above from simulation results. This proposed topology can be further extended by using different modulation techniques such as SHE PWM, Space Vector Modulation etc.

#### **References:**

[1]Ehsan Najafi, Member IEEE and Abdul Halim Mohamed Yatim Senior Member IEEE.,.."Design and Implementation of a New Multilevel Inverter Topology, IEEE TRANSACTIONS ON **INDUSTRIAL** ELECTRONICS, VOL.59, NO. 11 Nov 2012

[2]Pharne I.D. and Bhosale Y.N., "A Review on Multilevel Inverter Topology, " IEEE Conference on Power, Control and Embedded Systems, pp.700-703, 2013.

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

[3]Yi-Hung Liao, Member, IEEE, and Ching-Ming Lai, Member, IEEE, "Newly-Constructed Simplified Single-Phase Multistring Multilevel Inverter Topology for Distributed Energy Resources.," IEEE TRANSACTIONS ON POWER ELECTRONICS, Vol. 26, NO. 9, SEPTEMBER 2011.

- [3]Muhammad. H. Rashid, Power Electronics Circuits, Devices and Applications, Third Edition, Person Prentice Hall, pp.40-6430, 2004.

- [4] Husam. K. Al. H, "Investigation of a cascade multilevel inverter as advanced static compensator," Department of electrical engineering and computer engineering, University of Manitoba, Canada, August 2002

- [5] E. Villanueva, P. Correa, M. Pacas, "Control of a Single-Phase Cascaded H-Bridge Multilevel Inverter for Grid-Connected Photovoltaic Systems", IEEE Trans. Industrial Electronics, Vol. 56, pp. 4399-4406, 2009.

- [6] Rodriguez J, Lai JS, Peng FZ. Multilevel inverters: survey of topologies, controls, and applications. IEEE Trans Ind Appl 2002;49(4):724–38.

[7]Mohan N, Undeland T. M, and Robbins W.P. 2003, Power Electronics: converters, applications and design, Third Edition. John Wiley and sons.

- [8] Franquelo LG, Rodriguez J, Leon JI, Kouro S, Portillo R, Prats MAM. The age of multilevel converters arrives. IEEE Ind Electron Mag 2008;2(2):28–39.

- [9] Malinowski Mariusz, Gopakumar K, Rodriguez Jose, Pérez Marcelo A. A survey on cascaded multilevel inverters. IEEE Trans Ind Electron 2010;57(7).

- [10] Colak Ilhami, Kabalci Ersan, Bayindir Ramazan. Review of multilevel voltage source inverter topologies and control schemes. Energy Convers Manage 2011;52:1114–28.

- [11] Nabae A, Takahashi I, Akagi H. A new neutral-point clamped PWM inverter. IEEE Trans Ind Appl IA 1981(17):518–23.

- [12] Lai JS, Peng FZ. Multilevel converters a new breed of power converters. IEEE Trans Ind Appl 1996;32:509–17.

- [13] Sirisukprasert S, Xu Z, Zhang B, Lai JS, Huang AQ. A high-frequency 1.5 MVA H bridge building block for cascaded multilevel converters using emitter turn-off thyrister. Proc IEEE-APEC 2002:27–32.

- [14] Corzine Keith A, Wielebski Mike W, Peng Fang Z, Wang Jin. Control of cascaded multilevel inverters. IEEE Trans Power Electron 2004;19(3).

- [15] Power Electronics Handbook. 2nd ed. Academic Press; 2007. p 451.

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October2016

[16] Panda AK, Suresh Y. Research on cascade multilevel inverter with single DC source by using three-phase transformers. Int J Electr Power Energy Syst 2012;40(1):9–20.

[17]Munduate A, Figueres E, Garcera G. Robust model-following control of a threelevel neutral point clamped shunt active filter in the medium voltage range. Int J Electr Power Energy Syst 2009;31(10):577–88.

[18] Elgamal ME, Lotfy A, Ali GEM. Voltage profile enhancement by fuzzy controlled MLI UPFC. Int J Electr Power Energy Syst 2012; 34(1):10–8.

[19] Jih-Sheng Lai, Fang Zhen g Peng, "Multilevel converters a new breed of power converters," Industry Application Conference, Thirtieth IAS Annual Meeting, Conference Record of the IEEE, pp.2348-2356, August 2002.

## Authors:

P.RAVI TEJA Completed B.TECH in Electrical and Electronics Engineering in 2012 from Sri Vasavi Engineering College Bhimavaram, Affiliated to JNTU

Kakinada and M.tech in Electrical and Power Engineering in 2015 from Vishnu Institute of Technology affiliated to Jawaharlal Nehru Technological University Kakinada. His areas of interest include Power System Protection, PI controller and Power Electronics.

B.N.CH.V. Chakravarthi received his in Bachelor degree Electrical Engineering Electronics from Akula Gopayya Engineering College. Tadepalligudem, Andhra Pradesh, India in the year 2006. He completed his Master of Technology in Power Electronics at Nova Engineering College, Jangareddigudem, Andhra Pradesh, India in the year 2011. His area of interests includes Power Industrial drives and FACTS Controllers. He published two papers on Multilevel Inverters. He is a member of ISTE, IAENG. He is currently working as Assistant Professor in Electrical and Electronics Engineering Department at of Vishnu institute Technology Bhimavaram, Andhra Pradesh, India.