Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October 2016

### An Effective Finite Field Multiplier Utilising Redundant Illustration

<sup>1</sup>S.NARESH KUMAR, <sup>2</sup>B.NAGARAJU, <sup>3</sup>B.BALA KRISHNA, <sup>4</sup> Dr.B.S.R.MURTHY

<sup>1</sup> M.Tech Student, DEPT OF ELECTRONICS & COMMUNICATION ENGINEERING. GANDHI ACADEMY OF TECHNICAL EDUCATION, Ramapuram (Katamommu Gudem), Chilkur(M), Kodad, Telangana 508206

<sup>2</sup> M.TECH, Assistant Professor, DEPT OF ELECTRONICS & COMMUNICATION ENGINEERING. GANDHI ACADEMY OF TECHNICAL EDUCATION, Ramapuram (Katamommu Gudem), Chilkur(M), Kodad, Telangana 508206

<sup>3</sup> M.TECH, Assistant Professor, HOD, DEPT OF ELECTRONICS & COMMUNICATION ENGINEERING. GANDHI ACADEMY OF TECHNICAL EDUCATION, Ramapuram (Katamommu Gudem), Chilkur(M), Kodad, Telangana 508206

<sup>4</sup>Phd,Professor, & Principal. GANDHI ACADEMY OF TECHNICAL EDUCATION, Ramapuram (Katamommu Gudem), Chilkur(M), Kodad, Telangana 508206

#### **ABSTRACT:**

Through efficient projection of signal-flow graph (SFG) from the suggested formula, a very regular processor-space flow-graph (PSFG) comes. Redundant basis (RB) multipliers over Galois Field() have acquired huge recognition in elliptic curve cryptography (ECC) mainly due to their minimal hardware cost for squaring and modular reduction. Within this paper, we've suggested a manuscript recursive decomposition formula for RB multiplication to acquire highthroughput digit-serial implementation. It's proven the suggested high-throughput structures are the most useful one of the corresponding designs, for FPGA and ASIC implementation. By determining appropriate cut-sets, we've modified the PSFG superbly and carried out efficient feed-forward cut-set retiming to derive three novel multipliers which not just involve considerably a shorter period-complexity compared to existing ones but additionally require less area and fewer power consumption in comparison using the others. The synthesis recent results for field programmable gate array (FPGA) and application specific integrated circuit (ASIC) realization from the suggested designs and competing existing designs are in comparison. It's proven the suggested designs are capable of as much as 94% and 60% savings of area-delaypower product (ADPP) on FPGA and ASIC implementation over the very best of the present designs, correspondingly. Both theoretical analysis and synthesis results read the efficiency of suggested multipliers within the existing ones.

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14

October 2016

Keywords: ASIC, digit-serial, finite field multiplication, FPGA

#### I. INTRODUCTION

International Journal of Research

Furthermore, multiplication on the finite field may be used further to do other field procedures, e.g., division, exponentiation, and inversion. Multiplication over could be implemented on the general purpose machine, but it's costly to utilize a general purpose machine to apply cryptographic systems on price-sensitive consumer items. The majority of the real-time programs, therefore, need hardware implementation of finite field arithmetic procedures for those benefits like low-cost and-throughput rate [1]. Finite field multiplication over Galois Field is really a fundamental operation frequently experienced in modern cryptographic systems like the elliptic curve cryptography (ECC) and error control coding. Besides, a minimal-finish microprocessor cannot satisfy the real-time dependence on different programs since word-period of these processors is simply too small in comparison using the order of typical finite fields utilized in cryptographic systems. The option of basis to represent field elements, namely the polynomial basis, normal basis, triangular basis and redundant basis (RB) includes a major effect on the

performance from the arithmetic circuits [2]. The multipliers according to RB have significant attention recently acquired because of their several positive aspects. Furthermore they provide free squaring, normally basis does, but additionally involves lower computational complexity and could be implemented in highly regular computing structures. Several digit-level serial/parallel structures for RB multiplier over happen to be reported within the last years after its introduction by Wu et al. A competent serial/parallel multiplier using redundant representation continues to be little-serial presented. A word-parallel (BSWP) architecture for RB multiplier continues to be as stated by Namin et al. Other RB multipliers also provide been produced by exactly the same authors for lowering the complexity of implementation as well as for high-speed realization. We discover the hardware utilization efficiency and throughput of existing structures of could be enhanced by efficient style of formula and architecture. Within this paper, we goal at showing efficient digit-level serial/parallel designs for top-throughput finite field multiplication over according to

# **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October 2016

RB. We've planned the formula to 3 different architectures high-speed by mapping the parallel formula to some regular 2-dimensional signal-flow graph adopted (SFG) array, by appropriate projection of SFG to at least onedimensional processor-space flow graph (PSFG), and the option of feed-forward cutset to boost the throughput rate. We've suggested a competent recursive decomposition plan for digit-level RB multiplication, and according to we have derived parallel calculations for throughput digit-serial multiplication. Our suggested digit-serial multipliers involve considerably area-time-power less complexities compared to corresponding existing designs. Field programable gate array (FPGA) has developed like a mainstream devoted computing platform. FPGAs however don't have abundant quantity of registers for use within the multiplier [3]. Therefore, we've modified the suggested formula and architecture for decrease in register-complexity designed for the implementation of RB multipliers on FPGA platform. Aside from these we present a minimal critical-path digit-serial

RB multiplier for high throughput programs.

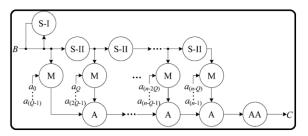

Fig.1. Framework of the PSFG

II. PROPOSED SYSTEM

Efficient one inch all reported calculations for digit-serial multiplication, we discover the hardware utilization efficiency and throughput of existing structures of might be enhanced further by efficient style of formula and architecture. For efficient realization of the digit-serial RB multiplier, we are able to perform feed-forward cut-set retiming inside a regular interval within the PSFG. Within the lately suggested RB multipliers, both operands and therefore are decomposed into numerous blocks to attain digit-serial multiplication, and then the partial items akin to these blocks are added together to get the preferred product word. Even though the existing formula is easily the most Because of cut-set retiming, the minimum time period of each clock period is reduced The PSFG, is planned towards the high-throughput digit-serial RB multiplier, known to as suggested structure-I (PS-I). PS-I consist of three modules, namely the part-permutation module (BPM), partial product generation module (PPGM) and

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14

October 2016

finite field accumulator module. The BPM performs rewiring of items of operand to give its output to partial product generation models (PPGU)s based on the S nodes of PSFG. The AND cell, XOR cell and register cell of PPGM carry out the purpose of M node, A node and delay enforced through the retiming of PSFG, correspondingly. Structures and processes of AND cell, XOR cell and register cell, correspondingly. The input operands are given to PPGU in staggered manner to satisfy the timing requirement in systolic pipeline. accumulator includes parallel bit-level accumulation cells. The recently received input will be added using the formerly accrued result and it makes sense kept in the register cell for use throughout the next cycle [4]. Accordingly, two regular PPGUs within the structure could be emerged right into a new regular PPGU. Featuring its two AND cells and 2 XOR cells (the very first PPGU requires just one XOR cell). The functions of AND cell, XOR cell and register cell overlap with individuals described. The critical road to the dwelling We are able to further transform the PSFG lessen the latency and hardware complexity of PS-I. To get the suggested structure. The critical path and throughput of

PS-II overlap with individuals of PS-I. Similarly, PS-II can be simply extended to bigger values of to possess low register-complexity structures. Therefore, we are able to introduce a manuscript cut-set retiming to lessen the critical path further. It may be observed the cut-set retiming enables to do the part-addition and bit-multiplication concurrently [5].

The suggested high-throughput structure (PS-III) of RB multiplier thus derived is. It includes PPGUs, and every PPGU includes one AND cell, one XOR cell and 2 register cells. The suggested structure yields the very first creation of preferred result cycles following the first input is given towards the structure, as the successive outputs can be found in each cycles.

We discover that PS-I and PS-II outshine another structures both in FPGA and ASIC platforms when it comes to area, some time and power complexities. Besides, due to their low area-time-power complexities and throughput rate, PS-I and PS-II may be used in a variety of real-time Specifically for **FPGA** programs. implementation, it's recommended to make use of either PS-I/II (for ) in line with the area constraint and speed dependence on

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14

October 2016

programs. For ASIC implementation, PS-I and PS-II or PS-III are preferred for his or efficiency in area-time-power her complexities. For programs needing greatest throughput, PS-III is the greatest choice. In conclusion, we are able to distinct structures based on the needs of various application conditions.

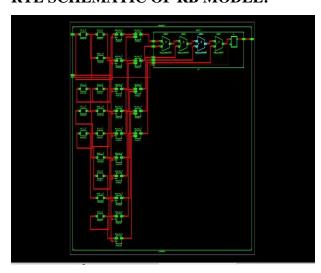

### RTL SCHEMATIC OF RB MODEL:

#### **Simulation Form:**

|                       |               |                                         | 4.00000 us                                                     |

|-----------------------|---------------|-----------------------------------------|----------------------------------------------------------------|

| Name                  | Value         | 10 us                                   | ļius ļ2us ļ3us 4us ļ5us ļ6us                                   |

| ▶ 🕌 a[9:0]            | 0000001111    | mmm                                     | 000001111                                                      |

| ▶ 🛂 b[9:0]            | 1000101010    | 22222222                                | 1000101010                                                     |

| ▶ 🛂 c[19:0]           | 00000010000   | XXXXXXXXXXXXXXXXX                       | 0000010000001110110                                            |

| l∰ dk                 | 2             |                                         |                                                                |

| ▶ 👹 mu1[4:0,19:0]     | [0000000000]  | [00000000000000000000000000000000000000 | [00000000000000000000000000000000000000                        |

| ▶ 😽 shift_n[4:0,19:0  | [0100010101   | [0ZZZZZZZZZZZZ00                        | [010001010100000000000000010010100000000                       |

| ▶ 😽 pu1[4:0,19:0]     | [00000000000] | [0XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX | [00000000000000000000000000000000000000                        |

| <b>a</b> u1[4:0,19:0] | [00000000000] | [00000000000000000000000000000000000000 | [00000000000000000000000000000000000000                        |

| ▶ 🕌 si1[4:0,19:0]     | [0000010001   | [00000ZZZZZZZZ                          | [00000 1000 10 10 10 10 0000,000000 1000 10 10 100000,00000]   |

| ▶ 👹 temp[5:0,19:0]    | [0000010001   | [00000ZZZZZZZZ                          | [00000 1000 10 10 10 10 00000,000000 1000 10 10 1000000,00000] |

| ▶ 🛂 a1[19:0]          | 00000000000   | 0000000000ZZZ                           | 000000000000001111                                             |

| ▶ 👹 b1[19:0]          | 00000000001   | 0000000000ZZZ                           | 00000000010001010                                              |

|                       |               |                                         |                                                                |

|                       |               |                                         |                                                                |

|                       |               | X1: 4.000000 us                         |                                                                |

#### III. CONCLUSION

By appropriate projection of SFG of suggested formula and determining appropriate cut-sets for feed-forward cut-set retiming, three novel high-throughput digitserial RB multipliers are derived to attain considerably less area-time-power complexities compared to existing ones. The suggested structures have different areatime-power trade-off behavior. Therefore, one inch the 3 suggested structures could be selected with respect to the dependence on the applying conditions. We've suggested a manuscript recursive decomposition formula for RB multiplication to derive highthroughput digit-serial multipliers. Furthermore, efficient structures with low register-count happen to be derived for arearestricted implementation especially for implementation in FPGA platform where registers aren't abundant. The outcomes of synthesis reveal that suggested structures is capable of saving as high as 94% and 60%, correspondingly, of ADPP for FPGA and ASIC implementation, correspondingly, over the very best of the present designs.

#### REFERENCES

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October 2016

- [1] N. R. Murthy and M. N. S. Swamy, "Cryptographic applications of brahmaqupta-bha skara equation," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 53, no. 7, pp. 1565–1571, 2006.

- [2] A. Reyhani-Masoleh and M. A. Hasan, "Low complexity word-level sequential normal basis multipliers," *IEEE Trans. Comput.*, vol. 54, no. 2, pp. 98–C110, Feb. 2005.

- [3] A. H. Namin, H. Wu, and M. Ahmadi, "An efficient finite field multiplier using redundant representation," *ACMTrans. Embedded Comput. Sys.*, vol. 11, no. 2, Jul. 2012, Art. 31.

- [4] H.Wu, M. A. Hasan, I. F. Blake, and S. Gao, "Finite field multiplier using redundant representation," *IEEE Trans. Comput.*, vol. 51, no. 11, pp. 1306–1316, Nov. 2002.

- [5] A. H. Namin, H. Wu, and M. Ahmadi, "An efficient finite field multiplier using redundant representation," ACMTrans. Embedded Comput. Sys., vol. 11, no. 2, Jul. 2012, Art. 31.