Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October 2016

## Design Of A Parallel Self-Timed Adder Utilizing Recursive Manner

<sup>1</sup> KONDI VEERASWAMY, <sup>2</sup> Mr.RADHAKRISHNAAN, <sup>3</sup> NAGA NAIK,

<sup>1</sup> M.Tech Student, Dept Of Electronics & Communication Engineering Brilliant Grammar School Educational Society's Group Of Institutions-Integrated Campus Abdullapurmet (V), HayathNagar (M), R.R Dt. Hyderabad – 501505

<sup>2</sup>M.TECH,(PHD),Associate Professor, Dept Of Electronics & Communication Engineering Brilliant Grammar School Educational Society's Group Of Institutions-Integrated Campus Abdullapurmet (V), HayathNagar (M), R.R Dt. Hyderabad – 501505

<sup>3</sup> M.TECH, Assoscoiate Professor, HOD, Dept Of Electronics & Communication Engineering Brilliant Grammar School Educational Society's Group Of Institutions-Integrated Campus Abdullapurmet (V), HayathNagar (M), R.R Dt. Hyderabad – 501505

### **ABSTARCT:**

technology reduces proportionally As reduced to a nanometer rated power, delay, and frequency field becomes the main The parameters for the analysis and design of any Circles. This summary provides a parallel lane one self timed Snake. It is based on a formula frequently Performance and multiple bilateral bits. This process Parallel to these pieces that have no chain hoist To post. Therefore, achieving a logarithmic efficiency design Because of the random laboratory conditions with the outside no exact circles accelerate or seemingly forward scheme. Processing and application functional along detection **Termination** and module. Implementation is common And now we do not have any functional restrictions High

fanouts. Excessive door required a fan though, but this Inevitable for good governance is not synchronized and managed through the use of Transistors connected in parallel. Simulations have An industry carried out using common tools Check out the practical application and the superiority of the proposal Current snakes closer asynchronous.

#### 1.INTRODUCTION:

Bilateral addition is the most important process The processor performs. Most adders have It is designed circuits simultaneously though There is great interest in an hour less circuits [1] .Asynchronous Circles assumes no quantization Weather. Therefore, they have a logic design potential for It is also free of many of the problems of speed limit

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14

October 2016

(Asynchronous) circuits. In principle, the logic flow in asynchronous The circuits that control the other party, wave line (or money ratepipelining Max-Aye) is a technique That can be applied through the inlet pipe before departure And the proposed stabilized department manages the automatic lane one input load of pipes separated by the propagation And the delay of inertia of the doors of the circuit path. the rest of this is organized briefly as follows. Section The second provides an overview of snakes in the scheduled breath. Section The third shows the buildings of the PSTA. Part IV presents CMOS implementation of the PSTA. Department Vprovides Simulation results .. Section VI reaches a conclusion.

#### 2. SELF TIME ADDER:

The self-timer for logic circuits based on time Assumptions right to run., Self-timer Snakes have the ability to run faster for the average Dynamic data, feeling the early termination can be avoided The need for a mechanism case worse delay Circles simultaneously. A.Pipelined snakes through a single lane data encryption: And asynchronous REQ / ACK handshake can be used for The adder allow the block, and the establishment flow To transport signals.

Mostof cases double track railway transport It is used for internal agreement bitwiseflow pregnancy Departures. These dual rail signals representing more than two (invalid, 0.1) logical values, so that they can Generate bit for use in the level of understanding that Little has been completed. touched Final completion When reception of all Acksignals bit (high). and carrycompletion is snake sensor an example of pipelinedadder [8], which uses the full adder (FA) Functional Adapted mobile rail fordual blocks. On the other hand, Isproposed snake speculative end in [9]. Used What logic it is called frustration and early termination of toselect Re correct execution of a fixed number of DELAYLINES. However, the logic implementation is frustrating Tohigh expensive because the fan in the hard requirements.B.Delay snakes coding using two rails: Snakes and vipers asynchronous delay sensitive (DI) DI assertbundling restrictions or operations. Therefore, they can correctlyoperate in the presence of Bounded but unknown gate and wire delays [2]. there are And many variants of snakes DI, DI ripple as carryadder (Dirca) and DI Collector Bmnicol expected (DICLA). addersuse DI dual carriageway coding is assumed to increase complexity. Though

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14

October 2016

double lane dual coding The complexity of the wiring, which canstill be used to produce Effective almost circles as such variables rail the single The use of bio-logic or NMOS designs only. Example And it has 40 transistors in the snake bit Dirca In [8] uses conventional CMOS whilethe RCA 28 transistors.Similar CLA, and DICLA known to carry the deployment, Generate, andkill equations in terms of dual carriageway coding [8]. They do not carry signals in a series connectthe But organized hierarchicaltree. Thus. Which could potentially run faster when there is a long period a further improvement is provided carrychain. A Note that logic can benefit dualrailencoding From the solution of any logic 0 or 1 lane path. Dual No need to wait for both tracks being evaluated. Thus, It is possible to further accelerate the download look forward Deportation departments send / implement comrades generate reference to the murder Level in the tree. Thisis put in [8] and referred DICLA acceleration circuit (DICLASP).

**3.LITERATURE REVIEW:**

In "Is it time for clock less chips?

[Asynchronous processor chips]"

Vendors are revisiting an old concept - the

clockless chip - as they look for new processor approaches to work with the growing number of cellular phones, PDAs, and other high-performance, batterypowered devices. Clockless processors, also called asynchronous or self-timed, don't use the oscillating crystal that serves as the regularly "ticking" clock that paces the work done by traditional synchronous processors. Rather than waiting for a clock tick, clockless-chip elements hand off the results of their work as soon as they are finished. However, clockless chips still generate concerns - such as a lack of development tools and expertise as well as difficulties with synchronous interfacing chip technology - that proponents must address before their commercial use can widespread.

In "Implementation of basic arithmetic operations using cellular automaton" This paper presents hardware architecture to perform the basic arithmetic operation addition using Cellular Automata (CA). This age old problem of addition were previously solved by ripple circuit or carry look ahead circuit or by using a combination of them. of Each these circuits is purely combinational in nature and their

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14

October 2016

complexity is centered on the number of logic gates and the associated gate delays. On the contrary, in our CA based design the complexity is mainly centered on the number of clock cycles required to finish the computation instead of the gate delays. To keep the design complexity within a feasible limit, the system designers are forced to look for simple, regular, modular, and reusable building blocks for implementing various complex functions. The homogeneous structure of Cellular Automata (CA) first introduced by J. von Neumann [1] in the early 50's, is a right candidate to fulfill all the above objectives. To this end we are Cellular motivated to use Automata Machine (CAM) [2] to arrive at the easily implementable parallel processing architecture in VLSI. In this paper, our focus is on addition operation since in ALU all other arithmetic operations can be derived in terms of addition operation only. The carry bits generated during addition are efficiently handled and as a result of which parallelism mechanism is embedded for the sake of convenience and efficiency. Each of the adder circuits previously used is purely in combinational nature and their complexity as shown in table 1 [3-6] is centered on the number of logic gates and the associated gate delays. On the contrary, in our design the complexity is mainly centered on number of clock cycles required to finish the computation instead of the gate delays.

#### **DESIGN OF PASTA**

In this section, the architecture and theory behind PASTA is presented. The adder first accepts two input operands to perform half additions for each bit. Subsequently, it iterates using earlier generated carry and sums to perform half-additions repeatedly until all carry bits are consumed and settled at zero level.

#### A. Architecture of PASTA

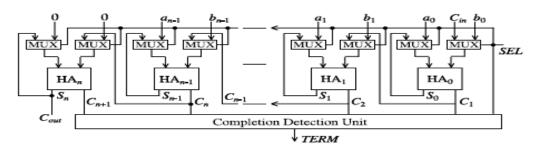

The general architecture of the adder is shown in Fig. 1. The selection input for two-input multiplexers corresponds to the Req handshake signal and will be a single 0 to 1 transition denoted by SEL. It will initially select the actual operands during SEL = 0 and will switch to feedback/carry paths for subsequent iterations using SEL = 1. The feedback path from the HAs enables the multiple iterations to continue until the completion when all carry signals will assume zero values.

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October 2016

Fig. 1. General block diagram of PASTA.

#### B. State Diagrams

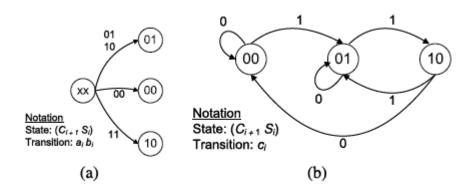

In Fig. 2, two state diagrams are drawn for the initial phase and the iterative phase of the proposed architecture. Each state is represented by (Ci+1 Si) pair where Ci+1, Si represent carry out and sum values, respectively, from the ith bit adder block. During the initial phase, the circuit merely works as a combinational HA operating in fundamental mode. It is apparent that due to the use of HAs instead of FAs, state (11) cannot appear During the iterative phase (SEL = 1), the feedback path through multiplexer block is activated. The carry

transitions (Ci) are allowed as many times as needed to complete the recursion. From the definition of fundamental mode circuits, the present design cannot be considered as a fundamental mode circuit as the inputoutputs will go through several transitions before producing the final output. It is not a Muller circuit working outside fundamental mode either as internally, several transitions will take place, as shown in the state diagram. This is analogous to cyclic sequential circuits where gate delays are utilized to separate individual states [4].

Fig. 2. State diagrams for PASTA. (a) Initial phase. (b) Iterative phase.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October 2016

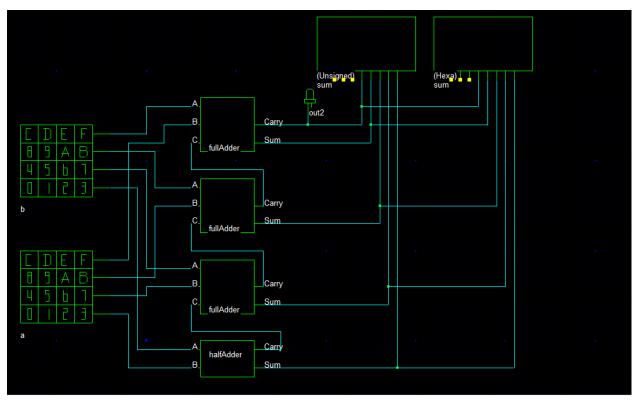

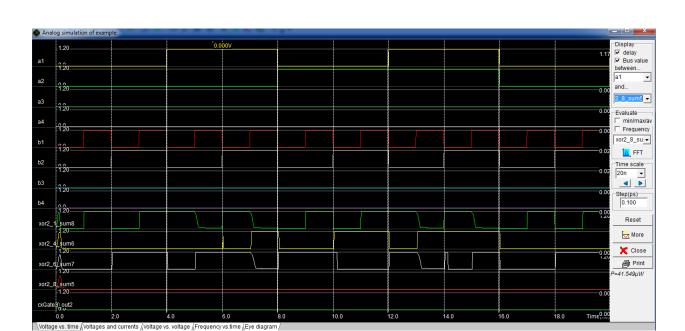

### **SIMULATION RESULTS:**

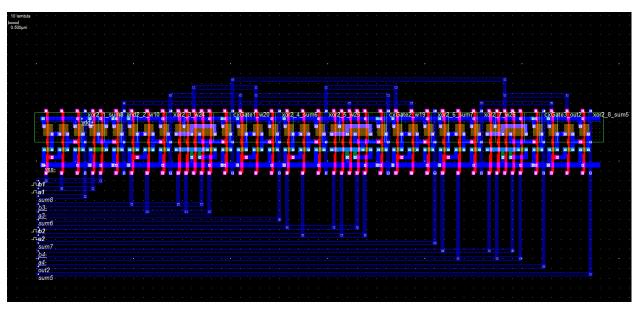

### LAYOUT:

### **SIMULATION GRAPH:**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14 October 2016

#### **CONCLUSION:**

This efficient brief presents an implementation of a PASTA. Initially, the theoretical foundation for a single-rail wavepipelined adder is established. Subsequently, the architectural design and **CMOS** implementations are presented. The design achieves a very simple n-bit adder that is area and interconnection-wise equivalent to the simplest adder namely the RCA. Moreover, the circuit works in a parallel manner for independent carry chains, and thus achieves logarithmic average time performance over random input values. The completion detection unit for the proposed adder is also practical and efficient. Simulation results are used to verify the advantages of the

proposed approach.

#### REFERENCES

[1] D. Geer, "Is it time for clockless chips? [Asynchronous processor chips]," *IEEE Comput.*, vol. 38, no. 3, pp. 18–19, Mar. 2005.

[2] J. Sparsø and S. Furber, *Principles of Asynchronous Circuit Design*. Boston, MA, USA: Kluwer Academic, 2001.

[3] P. Choudhury, S. Sahoo, and M. Chakraborty, "Implementation of basic arithmetic operations using cellular automaton," in *Proc. ICIT*, 2008, pp. 79–80.

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 14

October 2016

- [4] M. Z. Rahman and L. Kleeman, "A delay matched approach for the design of asynchronous sequential circuits," Dept. Comput. Syst. Technol., Univ. Malaya, Kuala Lumpur, Malaysia, Tech. Rep. 05042013, 2013.

- [5] M. D. Riedel, "Cyclic combinational circuits," Ph.D. dissertation, Dept. Comput. Sci., California Inst. Technol., Pasadena, CA, USA, May 2004.

- [6] R. F. Tinder, Asynchronous Sequential Machine Design and Analysis: Comprehensive Development of the Design and Analysis of Clock-Independent State Machines and Systems. San Mateo, CA, USA: Morgan, 2009.

- [7] W. Liu, C. T. Gray, D. Fan, and W. J. Farlow, "A 250-MHz wave pipelined adder in 2-µm CMOS," IEEE J. Solid-State Circuits, vol. 29, no. 9, pp. 1117–1128, Sep. 1994.

- [8] F.-C. Cheng, S. H. Unger, and M. Theobald, "Self-timed carrylookahead adders," IEEE Trans. Comput., vol. 49, no. 7, pp. 659–672, Jul. 2000.

- [9] S. Nowick, "Design of a low-latency adder using asynchronous speculative completion," IEE Proc. Comput. Digital Tech., vol. 143, no. 5, pp. 301-307, Sep. 1996.

- [10] N. Weste and D. Harris, CMOS VLSI Design: A Circuits and Systems Perspective. Reading, MA, USA: Addison-Wesley, 2005. [11] C. Cornelius, S. Koppe, and D. Timmermann, "Dynamic circuit techniques in deep submicron technologies: Domino logic reconsidered," in *Proc. IEEE ICICDT*, Feb. 2006, pp. 1–4.

- [12] M. Anis, S. Member, M. Allam, and M. Elmasry, "Impact of technology scaling on CMOS logic styles," IEEE Trans. Circuits Syst., Analog Digital Signal Process., vol. 49, no. 8, pp. 577–588, Aug. 2002.