Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

# **Design of Fastest Multiplier Using Delay Efficient Carry** Skip Adder

<sup>1</sup>P.Vasavi, M.Tech Scholar, Aditya College of engineering, Surampalem,

<sup>2</sup>G.Veerapandu, Associate professor, ECE, Aditya College of engineering, Surampalem,

ABSTRACT: Design of a high performance and high density multiplier is presented. This multiplier is constructed by using the Delay efficient carry skip adder. In previous we read about the designing of multipliers using the ripple carry adders and carry select adders. By using the ripple carry adders and carry select adders the propagation delay is high. In this paper, we present a carry skip adder (CSKA) structure that has a higher speed yet lower energy consumption compared with the conventional one. The speed enhancement is achieved by applying concatenation and increment schemes to improve the efficiency of the conventional (Conv-CSKA) CSKA structure. addition, instead of utilizing multiplexer logic, the proposed structure makes use of AND-OR- Invert (AOI) and OR-AND-Invert (OAI) compound gates for the skiplogic. The structure may be realized with both fixed stage size and variable stage size styles, where in the latter further improves the speed and energy parameters of the adder. The proposed multiplier design involves significantly less delay than the recently proposed multipliersusing carry select adders. Also, the results of multipliers designed by using both carry skip adderand carry select adder are compared. The results are synthesized using Xilinx 13.2 Software and simulated using Model sim Software.

#### INTRODUCTION

ADDERS are a key building block in arithmetic andlogic units (ALUs) [1] and hence increasing their speedand reducing their power/energy consumption strongly affect he speed and power consumption of processors. There are many works on the

subject of optimizing the speed and power of these units, which have been reported in [2]-[9].

Obviously, it is highly desirable to achieve speeds atlow-power/energy higher consumptions, which is a challenge for the designers of general purpose processors.

One of the effective techniques to lower the powerconsumption of digital circuits is to reduce the supply voltagedue to quadratic dependence of the switching energy onthe voltage. Moreover, the sub threshold current, which is the main leakage component in OFF devices, has an exponential dependence on the supply voltage level through thedrain-induced barrier lowering effect [10]. Depending on theamount of the supply voltage reduction, the operation of ON devices may reside in the super threshold, near-threshold, or sub threshold regions. Working in the super threshold region provides us with lower delay and higher switching leakagepowers compared with the near/sub threshold regions.

In the sub threshold region, the logic gate and leakage powerexhibit delay exponential dependences on the supply and thresholdvoltages. Moreover, these voltages are (potentially) subject toprocess and environmental variations in the nano scale technologies. The variations increase uncertainties in the aforesaidperformance parameters.

In addition, the small sub threshold current causes a large delay for the circuits operating in the sub threshold region [10].Recently, the near-threshold region has been consideredas a region that provides a more desirable trade off point between delay and power dissipation compared with that of the sub threshold one, because it results in lower delay

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

compared with the sub threshold region and significantly lowersswitching and leakage powers compared with the super threshold region. In addition, near-threshold operation, which uses supply voltage levels near the threshold voltage of transistors [3], suffers considerably less from the processand environmental variations compared with the sub threshold region.

The dependence of the power (and performance) on thesupply voltage has been the motivation for design of circuits with the feature of dynamic voltage and frequency scaling. In these circuits, to reduce the energy consumption, the systemmay change the voltage (and frequency) of the circuit basedon the workload requirement [5]. For these systems, thecircuit should be able to operate under a wide range supplyvoltage levels. Of course, achieving higher speeds at lowersupply voltages for the computational blocks, with the adderas one the main components, could be crucial in the design ofhigh-speed, yet energy efficient, processors.

To improve the performance of the adder structures at low supply voltage levels, some methods have been proposed in [7]-[9]. In [7]–[9], an adaptive clock stretching operation has been suggested. The method is based on the observation that the critical paths in adder units are rarely activated. Therefore, the slack time between the critical paths and the off-critical paths may be used to reduce the supply voltage. Notice that the voltage reduction must not increase the delays of the noncritical timing paths to become larger than the period of the clock allowing us to keep the original clock frequency at a reduced supply voltage level. When the critical timing paths in the adder are activated, the structure uses two clock cycles to complete the operation. This way the power consumption reduces considerably at the cost of rather small throughput degradation. In [7], the efficiency of this

method for reducing the power consumption of the RCA structure has been demonstrated.

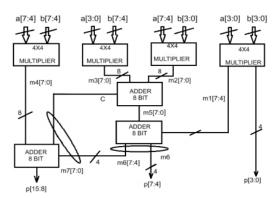

FIGURE.1 PROPOSED SYSTEM

In electronics, Multiplication is the most important arithmetic operation in signal processing applications. All the signal and processing operations multiplication. As speed is always a constraint in the multiplication operation, increase in speed can be achieved by reducing the number of steps in the computation process. The speed of multiplier determines the efficiency of such a system. In any system design, the three main constraints which determine the performance of the system are speed, area and power requirement. In arithmetic operation, adder is the basic hardware unit. So adder performance affects the overall system-performance. Carry Select Adder (CSLA) is widely used in many data processors for high speed application and in digital circuits to perform arithmetic operations.

The carry-select adder generally consists of two ripple carry adders and a multiplexer. Adding two n-bit numbers with a carry-select adder is done with two adders (therefore two ripple carry adders) in order to perform the calculation twice, one time with the assumption of the carryin being zero and the other assuming it will be one.

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

The number of bits in each carry select block can be uniform, or variable. In the uniform case, the optimal delay occurs When variable, the block size should have a delay, from addition inputs A and B to the carry out, equal to that of the multiplexer chain leading into it, so that the carry out iscalculated just in time. The delay is derived from uniform sizing, where the ideal number of full-adder elements per block is equal to the square root of the number of bits being added, since that will yield an equal number of MUX delays.

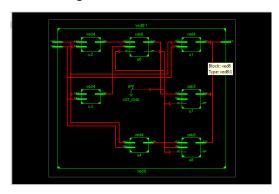

The R.T.L schematic diagram of 8x8 multiplier with carry skip adder is shown in below figure.

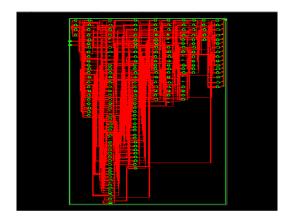

The technology schematic of 8x8 multiplier with carry skip adder is shown in below figure. It consists of LUT'S.

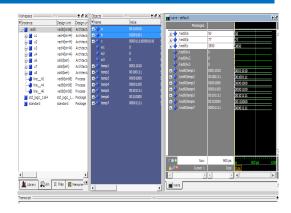

The output of 8x8 multiplier with carry skip adder in below figure.

#### **CONCLUSION:**

This multiplier is constructed by using the Delay efficient carry skip adder. In previous we studied about the designing of multipliers using the ripple carry adders and carry select adders. By using the ripple carry adders and carry select adders there are some disadvantages. In this paper, we present a carry skip adder (CSKA) structure that has a higher speed yet lower energy consumption compared with the conventional one. The speed enhancement is achieved by applying innovative techniques. The proposed multiplier design involves significantly less delay than the recently proposed multipliers using carry select adders. Also, the results of multipliers designed by using both carry skip adder and carry select adder are compared. The results are synthesized using Xilinx 13.2 Software and simulated using Modelsim Software.

#### REFERENCES

[1] I. Koren, Computer Arithmetic Algorithms, 2nd ed. Natick, MA, USA: A K Peters, Ltd., 2002.

[2] R. Zlatanovici, S. Kao, and B. Nikolic, "Energy-delay optimization of 64-bit carry-lookahead adders with a 240 ps 90 nm CMOS design example," IEEE J. Solid-State Circuits, vol. 44, no. 2, pp. 569–583,

Feb. 2009.

[3] S. K. Mathew, M. A. Anders, B. Bloechel, T. Nguyen, R. K.

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

Krishnamurthy, and S. Borkar, "A 4-GHz 300-mW 64-bit

integer execution ALU with dual supply voltages in 90-nm CMOS," IEEE J. Solid-State Circuits, vol. 40, no. 1, pp. 44–51, Jan. 2005.

- [4] V. G. Oklobdzija, B. R. Zeydel, H. Q. Dao, S. Mathew, and R. Krishnamurthy, "Comparison of high-performance VLSI adders in the energy-delay space," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 6, pp. 754–758, Jun. 2005.

- [5] B. Ramkumar and H. M. Kittur, "Low-power and area-efficient carry select adder," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2, pp. 371–375, Feb. 2012.

- [6] M. Vratonjic, B. R. Zeydel, and V. G. Oklobdzija, "Low- and ultra low-power arithmetic units: Design and comparison," in Proc. IEEE Int. Conf. Comput. Design, VLSI Comput. Process. (ICCD), Oct. 2005,

pp. 249-252.

- [7] C. Nagendra, M. J. Irwin, and R. M. Owens, "Area-time-power tradeoffs in parallel adders," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 43, no. 10, pp. 689–702, Oct. 1996.

- [8] Y. He and C.-H. Chang, "A power-delay efficient hybrid carrylookahead/carry-select based redundant binary to two's complement converter," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 1, pp. 336–346, Feb. 2008.

- [9] C.-H. Chang, J. Gu, and M. Zhang, "A review of 0.18 µm full adder performances for tree structured arithmetic circuits," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 6, pp. 686–695, Jun. 2005.

- [10] D. Markovic, C. C. Wang, L. P. Alarcon, T.-T. Liu, and J. M. Rabaey, "Ultralow-power design in near-threshold region," Proc. IEEE, vol. 98, no. 2, pp. 237–252, Feb. 2010.