# **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

# Unique Style to Achieve a Built-In Self-Test (The Best) Is Possible Uart By Ca-Lfsr

#### 1. P Raghava, 2. Mr.P.V.Vara Prasad Rao

<sup>1</sup>PG Scholar, Department of ECE, SLC's Institute of Engineering and Technology, Piglipur Village, Hayathnagar Mandal, Near Ramoji Film City, Ranga Reddy District, Hyderabad, Telangana

<sup>2</sup>Assosciate Professor, Department of ECE, SLC's Institute of Engineering and Technology, Piglipur Village, Hayathnagar Mandal, Near Ramoji Film City, Ranga Reddy District, Hyderabad, Telangana

#### **ABSTRACT:**

In today's life the manufacturing process is very complicated, including considering industries The test capability as a condition to ensure the reliability of the functions of each of the departments that have been designed. One of the It is called built in the most popular autonomous test techniques, test (the best). The best is a design that allows style To test the system itself automatically with the somewhat larger size of the system. Universal Asynchronous Receiver and Transmitter (UART) with the ability to enable the beast has a UART test target on the same chip and not External devices are required to perform the test. This document focuses on the (pattern generator) test of the TPG circuit From Best, in this document, performance as a result of the simulation is achieved by allowing the BIST architecture through **UART** VHDL programming sufficient to compensate for the additional hardware required in the beast architecture. East The generation of random test technical pattern automatically, so it can provide less trial time compared to the

Available online: http://internationaljournalofresearch.org/

outside Applied test pattern and helps to achieve higher productivity both at the end.

**Key Words:** VLSI, BIST, UART, VHDL, Cellular automata.

#### **INTRODUCTION:**

Reception and a Universal Asynchronous Transmitter (UART) is a type of serial communication Protocol; Used primarily for short-distance, low-speed, low cost, and data exchange between the computer and Peripherals. The use of the UART for serial data transfer via asynchronous data transfer In parallel with the series in the transmitter with some extra overhead that reduces the use of a shift register and vice versa, in Addressee. It is usually connected between the processor and peripheral, to the UART processor Look like an 8 bit parallel read / write port.

This document focuses on the design with the UART chip architecture to allow the use of the CA beast (Cellular Thermoplastic) LFSR with the help of the VHDL language. Built-in self-test or better, is a technique for Hardware design features and additional

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

programs in integrated circuits that enable them to perform Self-test, ie their own use of their own process test circuits, thereby reducing dependency External automatic test equipment (ATE) [6]. It is best to design in front of the technical (circuit) processing ability of test, Because it makes the electrical test of the chip easier, faster and more efficient, and less expensive. The BIST concept applies to almost any type of circuit, Even in practice it can vary the widest diversity of the product it caters to.

#### RELATED WORK

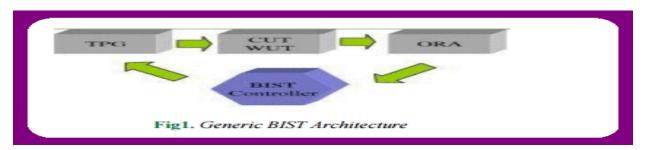

BIST is an on-chip test logic that is utilized to test the functional logic of a chip. A generic approach to BIST is shown in Figure 1. BIST solution consists of a Test Pattern Generator (TPG), a circuit to be tested, a way to analyze the results, and a way to compress those results for simplicity and handling. With the rapid increase in the design complexity, BIST has become a major design consideration in Design-For-Testability (DFT) methods and is becoming increasingly important in today's state of the

art SoC's.Achieving high fault Coverage while maintaining an acceptable design overhead and keeping the test time within limits is of utmost importance. BIST help to meet the desired goals. The brief introductions of BIST architecture component are given below.

Circuit under Test (CUT) It is the portion of the circuit tested in BIST mode. It can be sequential, combinational or a memory. It is delimited by their Primary Input (PI) and Primary Output (PO).

**Test Pattern Generator** (**TPG**) It generates patterns for the CUT. It is a dedicated circuit or a microprocessor. The patterns may be generated in pseudorandom or deterministically.

**Test Response Analysis (TRA/ORA)** It analyses the value sequence on PO and compares it with the expected output.

**BIST Controller Unit (BCU)** It controls the test execution; it manages the TPG, TRA and reconfigures the CUT and the multiplexer.

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

#### PROPOSED TPG

In previous design normal LFSR design used in TPG circuit, But proposed design consist the Cellular Automata LFSR is used. Test pattern generation is the most critical operations of BIST. Test patterns used in most implementations are pseudo-random in nature i.e. the random numbers generated algorithmically and are repeatable [4]. This is a desired characteristic, as truly random test patterns will lead to different fault coverage in every execution [2]. LFSRs are most commonly used to build TPGs [6] but recently there has been interest in CA for test pattern generation. CA generates test vectors which are more random in nature. Highly random vectors help in detection of faults such as the stuckopen faults, delay faults etc. which cannot be easily detected by vectors generated by LFSR.

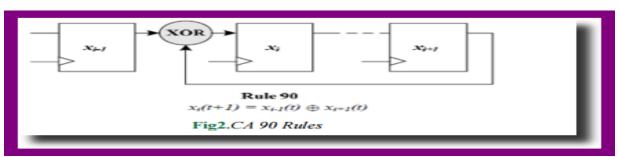

CA LFSR Cellular Automata (CA) consists of a collection of cells/nodes formed by flip-flops which are logically related to their nearest neighbors using XOR gates [2] [4]. When the value of a node is determined only by two neighboring cells the CA is known as one-dimensional linear CA (for the rest of the text one-dimensional linear CA is referred as a CA). The logical relations which relate a node to its neighbors are known as rules and they de-fine the characteristics of a CA. There are many rules which can be used to construct a CA register, the most popular being rules 90 illustrated in Figure.

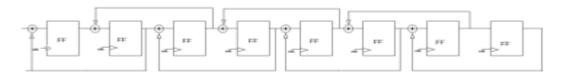

The CA LFSR is designed by using CA rule 90, which generate the random values in TPG for UART; the CA LFSR is shown in figure 3.

Fig3. CA LFSR

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

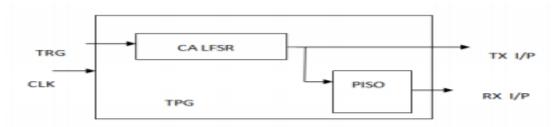

When the trg signal goes high, a new data is obtained from the CA LFSR which is fed in parallel to the input of the transmitter, and the ca lfsr output is given to PISO (parallel

in serial out) block in TPG, it generates the serial data to UART receiver input. The complete TPG block is shows in fig.

Fig4. TPG block

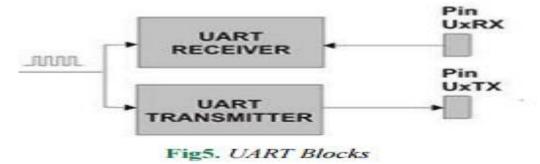

UART Universal asynchronous receive transmit (UART) is an asynchronous serial receiver/transmitter. It is a piece of computer hardware that commonly used in PC serial port to translate data between parallel and serial interfaces. The UART takes bytes of data and transmits the individual bits in a sequential fashion. At the receiving point, UART re-assembles the bits into complete bytes. Asynchronous

transmission allows data to be transmitted without having to send a clock signal to the receiver. Thus, the sender and receiver must agree on timing parameters in advance and special bits are added to each word, which is used to synchronize the sending and receiving units. In general, UART contains of two main block, the transmitter and receiver block.

#### **UART Transmitter Section**

# **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

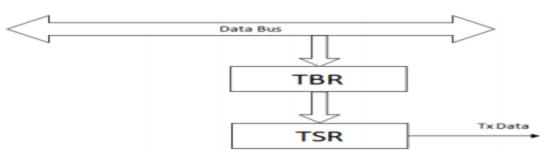

Fig6. UART Transmitter Section

The Block diagram of UART Transmitter is as shown in figure. The data is loaded from Data Bus into TBR (Transmit Buffer Register) and from TBR to TSR (Transmit Shift Register), based on the control and status signals produced by the Control unit.

The Size of TSR is taken in such a way that, it should accommodate the START and STOP bits along with the Data bits which are loaded from the Data Bus.

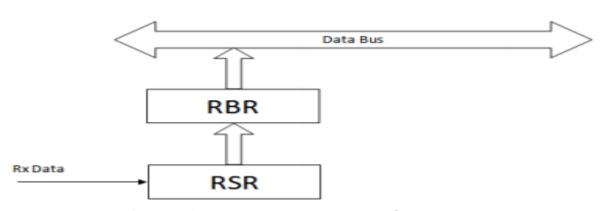

**UART** Receiver Section

Fig7. UART receiver section architecture

The Block diagram of UART Receiver is as shown in figure. The data receiving will be captured using receiving baud clock and then loaded into RSR (Receive Shift Register) and from RSR to RBR (Receive Buffer Register), and then to Data Bus, based on the control and status signals

produced by the Control unit. The Size of RSR is taken in such a way that, it should accommodate the START and STOP bits along with the Data bits which are loaded from the Data Bus

#### **UART BIST Design**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

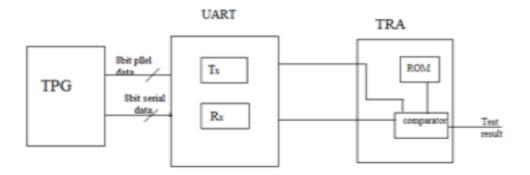

Fig8. Enabled BIST UART Design

When the trigger signal goes high then only a new value is generated in the LFSR. This LFSR will generate (28 -1) different pseudorandom values, The parallel output "TX i/p" is fed to the transmitter and the serial output is fed to the receiver section of the UART. When the trg signal goes high, a new data is obtained from the LFSR which is fed in parallel to the input of the transmitter. After a certain number of clock cycles, the same data is obtained at the output of the transmitter as serial data. This serial data is shifted in the SIPO of the comparator and this is the sipo\_op data. This sipo\_op is compared with the ROM data (romd). The shaded regions in the figure shows the time of comparison. Depending on the comparison, the result (i.e. rslt) is generated. If the both sipo\_op and romd are same then rslt=1, else rslt=0. As the receiver provides 8-bit parallel output, a SIPO is not required in this case. The output from the receiver "rop" is directly compared with

romd. The shaded regions in the figure too show the comparison time. In all the shaded regions, except the last one romd and rop are same and so the rslt is 1 in all those cases. But in the last comparison, due to the intentionally stored incorrect data in the ROM the comparison results in rslt=0. Henceforth comparison procedure is stopped and the CUT is announced to be faulty.

#### ROM:

ROM is used to store the 8-bit pseudo random patterns, in order, that will be obtained as the output from the Transmitter and Receiver sections of the developed UART. The data that are obtained as the outputs of the receiver and the transmitter are compared with the data stored at the corresponding addresses of the ROM by the comparator which verifies whether the CUT is working properly or not.

**CONCLUSION** This paper implements the BIST Enabled UART with cellular automata

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November 2016

LFSR as TPG and total design Using VHDL language, enabled BIST test the UART transmitter and receiver modules by comparing both outputs at TRA unit.

#### REFERENCES

- [1] S. Zhang, R. Byrne, J.C. Muzio, D.M. Miller, "Why cellular automata are better than LFSRs as built-in self-test generators for sequential-type faults", IEEE International Symposium on Circuits and Systems, Vol. 1,1994

- [2] C. Stroud, A Designer's Guide to Built-In Self-Test, Kluwer Academic Publishers, Bos-ton MA, 2002

- [3] M.L. Bushnell, V.D. Agrawal, Essentials of Electronics Testing for Digital, Memory & Mixed Signal VLSI Circuits, Kluwer Aca-demic Publishers, Boston MA, 2000

- [4] K. Furuya, E.J. McCluskey, "Two-Pattern test capabilities of autonomous TPG circuits,"

- [5] Proc. of International Test Conference, pp 704 711, 1991.

- [6] P.H. Bardell, W.H. McAnney, J. Savir, Built-in test for VLSI: Pseudorandom Techniques, John Wiley and Sons, New York, 1987

Available online: http://internationaljournalofresearch.org/

- [7] D. Bhavsar and R. Heckelman, "Self Testing by Polynomial Division," Proc. IEEE International Test Conference, pp. 208 216, 1981.

- [8] "Linear Feedback Shift Register," en.Wikipedia.org