# Implementation of Low Power Full Adder Using Semi XOR Semi XNOR on 120 nm Technology

Veena Tiwari.<sup>#1</sup>, Mohd. Abuzer Khan<sup>\*2</sup>

<sup>#</sup>Electronics & Communication, R.G.P. V Bhopal L.K.C.T. Indore M.P. India <sup>1</sup>tiwariveena87@gmail.com <sup>2</sup>abuzerlkct@gmail.com

*Abstract:* In present work a new XNOR gate using three transistors has been presented, which shows powerdissipation of  $550.7272\mu$ W in 0.12µm technology with supply voltage of 1.5V. Minimum level for highoutput of 2.05V and maximum level for low output of 0.084V have been obtained. A single bit full adderusing eight transistors has been designed using proposed XNOR cell, which shows power dissipation of  $581.542\mu$ W. Minimum level for high output of 1.97V and maximum level for low output of 0.24V isobtained for sum output signal. For carry signal maximum level for low output of 0.32V and minimum level for high output of 3.2V have been achieved. Simulations have been performed by using TPICE based on0.12µm CMOS technology. Power consumption of proposed XNOR gate and full adder has beencompared with earlier reported circuits and proposed circuit's shows better performance in terms of powerconsumption and transistor count.

#### Keywords: CMOS, exclusive-OR (XOR), exclusive-NOR (XNOR), full adder, low power, pass transistor logic. Introduction Therefore, binaryadders are crucial building

With exponential growth of portable electronic devices like laptops, multimedia and cellulardevice, research efforts in the field of low power VLSI (very large-scale integration) systemshave increased many folds. With the rise in chip density, power consumption of VLSI systems is also increasing and this further, adds to reliability and packaging problems. Packaging andcooling cost of VLSI systems also goes up with high power dissipation. Now a day's low powerconsumption along with minimum delay and area requirements is one of important designconsideration for IC designers. There are three major source of power consumption in CMOSVLSI circuits: 1) switching power due to charging and discharging of capacitances, 2) shortcircuit power due to current flow from power supply to ground with simultaneous functioning of p-network and n-networks, 3) static power due to leakage currents.Binary addition is basic and most frequently used arithmetic operation microprocessors, in digitalsignal processors (DSP) and applicationintegrated (ASIC) specific circuits etc.

Therefore, binaryadders are crucial building blocks VLSI in circuits and efficient implementation of these addersaffects the performance of entire system. In recent years various types of adder using differentlogic styles have been proposed [1-12]. Standard CMOS 28 transistor adder using pull up and pull-down network with 14 NMOS transistors and 14 PMOS transistors is most widely reported [1]. In [2] a 16 transistors full adder cell with XOR/XNOR, pass transistor logic (PTL) and transmission gate is reported. Complementary pass-transistor logic (CPL) with 32 transistors having high power dissipation and better driving capability is reported in [4]. Transmission gate CMOS adder (TGA) based on transmission gates using 20 transistors is reported in [5]. Main disadvantage of TGA is that it requires double transistors count that of pass transistor logic for implementations of same logic function. A transmission function full adder (TFA) based on transmission function theory used 16 transistors [6]. Multiplexer based adder (MBA) having 12 transistors and elimination of direct path to power supply is reported in [7]. Static energy

recovery full (SERF) adder using 10 transistors with reduced power consumption at the cost of higher delay is presented in [8]. Another design of full adder with 10 transistors using XOR/XNOR gates is also reported in [9]. A hybrid CMOS logic style adder with 22 transistors is reported [10]. In [11] a full adder

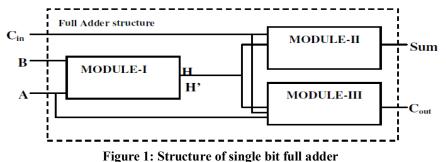

circuit using 22 transistors based on hybrid pass logic (HPSC) is presented. Full adder for embedded applications using three inputs XOR is also reported in [12]. The function of full adder is based on following equation, given three single bit inputs as A, B, Cin and it generates two outputs of single bit Sum and Cout.

The exclusive-OR (XOR) and exclusive-NOR (XNOR) gates are the basic building blocks of afull adder circuit. The XOR/XNOR gates can be implemented using AND, OR, and NOT gateswith high redundancy [1]. Optimized design of these gates enhances the performance of VLSIsystems as these gates are utilized as sub blocks in larger circuits. XNOR/XOR design with lessnumber of transistors, lesser power dissipation and delay are highly desirable for efficientimplementation of the large VLSI system. XOR gate based on eight transistors and six transistorshave been used in many earlier designs [1, 13]. Four transistors PTL based XOR gates withlimited driving capabilities have been reported in [14]. Different designs for XOR and XNORgates using four transistors have been presented in [9, 15-17]. Design for three inputs XOR gateinstead of two inputs has been reported in [18]. XOR/XNOR design with ten transistors based ontransmission gates has been reported in [19]. XOR/XNOR circuits with dualfeedback for rectification of degraded logic problem have been reported in [20, 21]. Different power efficient adder designed with body biasing techniques has been reported in [22]. Further, CMOS adder designs with 9 and 10 transistors have been presented in [23]. At circuit level, an

optimized design is desirable having less numbers of transistors, small power consumption and adequate output voltage swing. Here, in present work a new XNOR gate with three transistors has been proposed. A single bit full adder having eight transistors based on proposed XNOR module and one multiplexer block having two transistors has been presented. The rest of paper is organized as follows: In Section II, a new three transistors XNOR gate has been reported and single bit full adder circuit based on XNOR gates and multiplexer has been designed. In section III results of proposed XNOR cell and single bit full adder designed in previous section have been presented and compared with previous reported circuits. Section IV concludes the work.

## **II. SYSTEM DESCRIPTION**

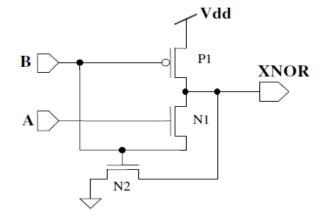

Proposed design of XNOR with three transistors has been shown in Figure 2. In XNOR circuit, the gate lengths of all three transistors have been taken as  $0.35\mu$ m. Width (Wn) of NMOStransistors N1 and N2 has been taken  $5.0\mu$ m and  $1.0\mu$ m respectively. Width (Wp) for transistor P1has been taken as  $2.0\mu$ m. In proposed XNOR, when A=B=0 output is high because transistor P1is on and N1, N2 transistors

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November2016

are off. With input combinations of A=0 and B=1 circuit shows lowoutput as transistor P1 is off and output node is discharged by transistor N2, which is in oncondition. In case when A=B=1, output node shows high logic as transistor N1 is on and highlogic is passed to output. Width (Wn) of N1 is made large to provide low resistance and due towhich signal B is passed to output with less delay, whereas P1 gives higher resistance and higherdelay to pass the Vdd signal. For N1 transistor width has been increased which provides reductionin threshold voltage as shown in equation (5) [24]. Due to thisdecrease in Vt the degradation in he output logic is reduced and signal shows sufficient voltage swing.

Further, due to higher delay provided by PMOS transistor (P1), drain source voltage (Vds) of N1 is increased gradually. Transistor N1 operates in non-saturation region and then goes to saturation region. On resistance of MOS transistor consists of the series combination of Rd (drain resistance) and Rs (source resistance) and channel resistance. As for superior switching action

higher Vgs is desirable. Transistor N1 has larger width, less resistance and higher Vgs so switching is very fast in this case. When Vds is less than Vgs-Vt but greater than zero the channel resistance in non saturation region is given as by [25].

In another case when A=1 and B=0 both transistors (P1 & N1) are on and output node is discharged rapidly by N1 and N2 transistors. In this case with A=1 transistor N1 turns on which further turn on the transistor N2 and a conducting path is provided by N1 and N2. This connectivity of output node with ground discharges the output node. The switching speed of N1 is higher than N2 because delay is inversely proportional to channel width [1]. Due to on condition of transistor N1 the gate voltage of N2 increase above its threshold voltage and transistor N2 also goes in on condition. In this position the circuit is just behaving like an inverter with A=1 as input and gives output as low logic. Transistor P1 is just acting as load resistance with grounded gate input (B=0).

Figure 2: Design of proposed 3 transistors XNOR gate

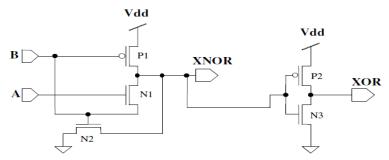

XOR operation can be obtained with addition of additional inverter. Signals levels are also restored to Vdd in the proposed design by addition of inverter with little increase in power consumption. Complete XNOR/XOR module with five transistors has been shown in Figure 2. Typical values of transistor widths (Wp= $2.0\mu m$ ) for P2 and (Wn = $1.0\mu m$ ) for N3 have been taken for inverter section. Simulations of XNOR gate and XNOR/XOR cell also have been carried out with varying supply voltage from [3.3 - 1.8] V.

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November2016

Figure 3: Design of proposed XNOR/XOR cell

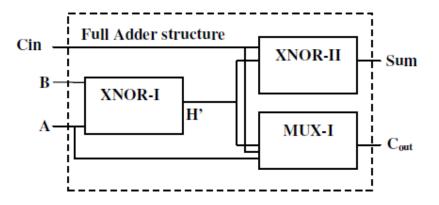

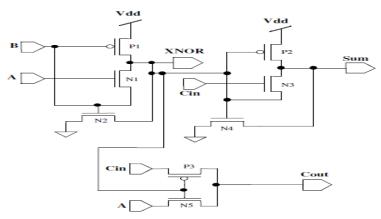

Full adder circuit can be implemented with different combinations of XOR/XNOR modules and two multiplexer [2, 17] but this approach has not been used in current work as proposed XNOR/XOR cell shows high power consumption than single XNOR gate. Proposed full adder circuit has been implemented by two XNOR gates and one multiplexer block as shown in block diagram of Figure 4(a). Sum is generated by two XNOR gates and Cout is generated by two transistors multiplexer block. The single bit full adder using proposed XNOR gates with eight transistors has been implemented and shown in Figure 4(b). For multiplexer section typical values of width (Wn& WP) 1.0µm & 2µm for NMOS and PMOS transistors have been taken with gate length of 0.35µm. Simulations have been performed using SPICE based on TSMC 0.35µm CMOS technology with supply voltage of 3.3V.

Figure 4: Full adder using two XNOR gates and multiplexer Block diagram

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 03 Issue 17 November2016

Figure 5: Full adder using two XNOR gates and multiplexer Circuit diagram

## **III. RESULTS AND DISCUSSIONS**

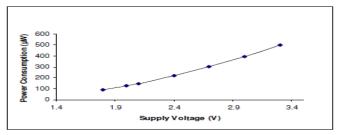

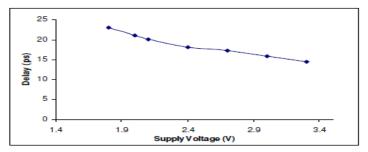

The power consumption, delay and output voltage levels with varying supply voltage [3.3 - 1.8] V for proposed XNOR gate [Figure 2]. Power consumption varies from [500.727 - 89.931] µW with variations in supply voltage from [3.3 - 1.8] V as shown in Figure 5. Delay varies from [14.466 - 23.050] ps with variations in supply voltage from [3.3 - 1.8] V and has been shown in Figure 6. Power consumption has been reduced due to reduced transistor count and reduced capacitance in the XNOR circuit. Short circuit currents are also quite low in the circuit as direct path from supply to ground is eliminated. It has been observed from Figure 6 & 7 that power consumption reduces, whereas delay increase with reduction in supply voltage. The proposed XNOR gate provide sufficient output voltage levels and noise margin of approximately 2V has been obtained with 3.3V supply.

Figure 6: Power consumption of XNOR gate with supply voltage

Figure 7: Delay of XNOR gate with supply voltage

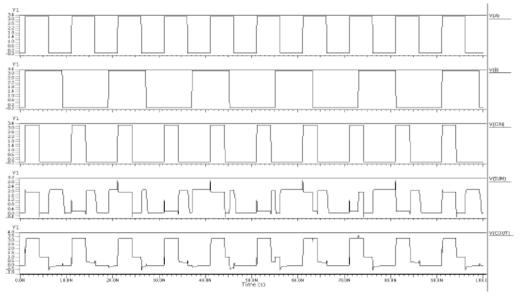

power consumption, output delay and output voltage levels for sum and carry signals for eight transistors single bit adder. Proposed adder circuit shows power consumption of 581.542  $\mu$ W with

acceptable level of output. Figure 8 shows the input and output waveform results for full adder circuit. Proposed full adder has less internal capacitance due to reduce number of transistors and shows reduced power consumption. A wide range of simulation has been done form 3.3 V to 1.8 V to see levels of output signal circuit which shows acceptable voltage levels are obtained with proposed circuits.

Figure 8: Input and output patterns for proposed full adder

## **IV. CONCLUSIONS**

In current work, a new low power XNOR gate with three transistors have been reported which shows power dissipation of 500.7272  $\mu$ W. Compared with earlier reported XNOR gates, proposed circuit shows less power consumption and better output signal levels with reduce transistor count. A single bit full adder with 8 transistors based on proposed XNOR gate has been presented which show power consumption of 581.542 $\mu$ W with maximum output delay of 15.1311 ps. Proposed full adder has been compared with earlier reported circuits and reported circuit shows reduced power consumption with less number of transistors.

## V. Reference

[1] Y. Leblebici, S.M. Kang, CMOS Digital Integrated Circuits, Singapore: McGraw Hill, 2nd edition,1999.

[2] A. M. Shams and M. Bayoumi, "A novel highperformance CMOS1-bit full adder cell," IEEETransaction on

Circuits Systems II, Analog Digital Signal Process, vol. 47, no. 5, pp. 478–481, May2000.

[3] Ahmed M. Shams and Magdy A, "A structured approach for designing low power adders,"Conference Record of the Thirty-First Asilomar Conference on Signals, Systems & Computers, vol.1, pp.757-761, Nov. 1997.

[4] R. Zimmermann, and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic,"IEEE J. Solid State Circuits, vol. 32, no. 7, pp. 1079-1090, Jul. 1997.

[5] N. Weste and K. Eshraghian, Principles of CMOS VLSI Design, A System Perspective, Addison-Wesley, 1993.

[6] N. Zhuang and H. Wu, "A new design of the CMOS full adder," IEEE J. Solid-State Circuits, vol.27, no. 5, pp. 840–844, May 1992.

[7] Yingtao Jiang Al-Sheraidah, A. Yuke Wang Sha, E. and Jin-Gyun Chung, "A novel multiplexerbasedlow-power full adder," IEEE Transactions on Circuits and Systems: Express Briefs, vol. 51, no.7, pp.345-348, Jul. 2004.

[8] R. Shalem, E. John, and L. K. John, "A novel low-power energy recovery full adder cell," in Proc.Great Lakes Symposium on VLSI, pp. 380–383, Feb. 1999.

[9] H. T. Bui, Y. Wang, and Y. Jiang, "Design and analysis of low-power 10-transistor full adders usingXOR-XNOR gates,"

IEEE Transactions Circuits Systems II, Analog Digital Signal Process, vol. 49,no. 1, pp. 25–30, Jan. 2002.

[10] S. Goel. A. Kumar, M. A. Bayoumi, "Design of robust, energy –efficient full adders for deep submicrometer design using hybrid-CMOS logic style," IEEE Transactions on Very Large ScaleIntegration (VLSI) Systems, vol.14, no.12, pp.1309-1321,Dec. 2006.

[11] Zhang, M., J. Gu and C.H. Chang, "A novel hybrid pass logic with static CMOS output drive fulladdercell," IEEE Int. Symposium on Circuits Systems, vol. 5, pp. 317-320, May 2003.

[12] Chiou-Kou Tung, Yu-Cherng Hung, Shao-Hui Shieh, and Guo-Shing Huang, "A Low-Power High-Speed Hybrid CMOS Full Adder for Embedded System," IEEE conference on Design andDiagnostics of Electronic Circuits and Systems, pp. 1-4, 2007.

[13] D. Radhakrishnan, "Low-voltage low-power CMOS full adder," in Proc. IEE Circuits DevicesSystem, vol. 148, pp. 19-24, Feb. 2001.

[14] J.-M. Wang, S.-C. Fang, and W.-S. Feng, "New efficient designs for XOR and XNOR functions on the transistor level," IEEE J. Solid-State Circuits, vol. 29, no. 7, pp. 780–786, Jul. 1994.

[15] H. T. Bui, A. K. Al-Sheraidah, and Y.Wang, "New 4transistors XOR and XNOR designs," in Proc.2nd IEEE Asia Pacific Conference, ASIC, pp. 25–28, Aug. 2000.

[16] H.T. Bui, Y. Wang, Y. Jiang , "Design and analysis of 10-transistor full adders using novel XOR–XNOR gates," in Proc. 5th International Conference on Signal Process., vol. 1, pp. 619–622, Aug.21–25, 2000.International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.4, December 2011.

[17] Jin-Fa Lin, Y.T. Hwang, M.H.Sheu and C.C.Ho, "A Novel High-Speed and Energy Efficient10-Transistor Full Adder Design," IEEE Transactions on Circuits and Systems, vol. 54, no. 5pp.1050.1059, May 2007.

[18] Sung-Chuan Fang, Jyh-Ming Wang, and Wu-Shiung Feng, "A new direct design for three-input XORfunction on the transistor level," IEEE Trans. Circuits System I: Fundamental theory and Applications, vol. 43, no. 4, Apr. 1996.

[19] A. M. Shams, T. K. Darwish, and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOSfull adder cells," IEEE Trans. Very Large Scale Integration (VLSI) Systems, vol. 10, no. 1.

[20] S. Goel, M. E. Elgamel, M. A. Bayouni, and Y. Hanafy, "Design methodologies for highperformancenoise-tolerant XOR-XNOR circuits," IEEE Trans. Circuits and System. I, vol. 53, no. 4,Apr. 2006.

[21] Shiv Shankar Mishra, S. Wairya, R.K. Nagaria and S. Tiwari, "New design methodologies for highspeed low power XOR-XNOR circuits," World Academy of Science, Engineering and Technology,vol.55, pp.200-206, 2009.

[22] Manoj Kumar, Sandeep K. Arya and Sujata Pandey, "Low power CMOS full adder design with bodybiasing approach," Journal of Integrated Circuits and Systems, Brazil, vol. 6, no.1, pp.75-80, March2011.

[23] Manoj Kumar, Sujata Pandey and Sandeep K. Arya, "Design of CMOS Energy Efficient Single BitFull Adder," BookChapter of Communications in Computer and Information Science, SpringerVerlag Berlin Heidelberg, CCIS 169, pp. 159-168, Jul. 2011.

[24] Y.Tsividis, Mixed Analog-Digital VLSI devices and Technology, Singapore: McGraw Hill, 1996.

[25] Phillip E. Allen and Douglas R. Holberg, CMOS analog circuit design, Oxford University Press,2009.

[26] BehzadRazavi, Design of Analog CMOS Integrated Circuits, Tata McGraw Hill, 2002.