Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 03 March 2017

### Coherent Arbitration Scheme for Advanced Soc

K Sirisha #1, V Sulochana \*2

# P.G. Scholar in VLSI, \* Assistant Professor, Department of ECE

Priyadarshini Institute of Science & Technology for Women, Tenali, Andhrapradesh

### **Abstract**

A run of the mill System-on-Chip (SOC) plan is having a wide range of centers connected together with complex on chip bus correspondence architectures. This onarchitecture chip correspondence decides distinctive practical how these synchronize their centers exchange and information. AMBA has a pecking order of busses with Advance superior bus (AHB) that can be utilized to get associated with peripherals and APB (Advance elite Peripheral Bus) that can be associated with execution peripherals. Subsequently, all **AMBA** is the among correspondence architecture. AHB bus is utilized as a part of elite and high data transfer capacity framework as it has superior elements, similar to blast exchange, split exchange and pipelined operation. In AMBA framework, AHB ace is the principle segment that starts the read and composes exchanges. This paper, concentrates on plan of novel mediation conspire for the usage of AHB ace in Verilog HDL.

Keywords: AMBA, AHB, APB, AHB Master, SOC, Split exchange.

Keywords:

### I. INTRODUCTION

The Advanced Microcontroller Bus Architecture particular is an on-chip correspondence standard for outlining elite microcontrollers. A common System-onChip (SOC) outline contains various IP centers connected together with modern onchip bus correspondence architectures. These arrangements with an awesome effect on the system's execution. There numerous correspondence architectures utilized as a part of the business like AMBA, PI-bus, Core Connect, Wishbone, Avalon and so on. AMBA is a standard interface determination which ensures the similarity between various IP parts gave by plan merchants. **AMBA** various 2.0 particular characterizes three unique busses [1]:-

- Propelled elite Bus (AHB)

- Propelled System Bus (ASB)

- Propelled Peripheral Bus (APB)

An AMBA based installed microcontroller ordinarily comprises of a superior framework spine bus (AMBA AHB or ASB), which can keep up the outer memory transmission capacity. AHB bus gives a high-transmission capacity interface between various components which are included in the diverse exchanges. There is likewise an accessibility of the AHB to APB Bridge, which is utilized to get to low fringe gadgets on superior bus. APB Bridge is just the ace for APB bus [2]. This paper basically manages AMBA AHB bus and especially AHB ace. The paper is separated into three areas. To begin with area is Presentation that presents AHB framework, its components and a few signs related with

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 03 March 2017

AHB ace. Second segment has the portrayal identified with limited state intended for AHB ace. At long last the Third the consequences of segment contains actualizing the state machine in the Verilog equipment portrayal dialect.

Propelled elite Bus (AHB): AHB bus is another era of AMBA 2.0 detail, which was planned to bring up the prerequisites of superior synthesizable outlines. AHB is the new level of bus which sits above ASB and features required for high APB. The performance, high clock frequency systems are as follows [1]:

- Burst transfers (4/8/16 beat burst)

- Split transactions

- Bus master handover in single cycle

- Single clock edge operation

- ☐ Wider data bus configuration (8/16/32/64/128/256/512/1024 bits)

- Pipelined operation

An AMBA AHB configuration comprises of at least one bus masters (AHB underpins up to 16 masters), commonly a framework may contain at any rate the processor as an AHB master. Notwithstanding. **DMA** (Direct Memory Access) or DSP (Digital Signal Processor) can likewise be utilized as bus masters. The outer memory interfaces like SRAM, ROM, APB Bridge and diverse inward recollections are the regular AHB Some other peripherals in the slaves. framework may likewise be incorporated as AHB slaves. An AHB bus master has complex interface in AMBA and can start read/compose operations by giving address and control data in first clock cycle. Just a single bus master at one time is permitted to exchange the information on the bus and this choice is made by an Arbiter in the framework. An authority assumes a vital part in asset sharing. Authority may take this choice of giving access the bus to a specific master in view of various discretion plans like need insightful or round robin and so forth. A bus slave reacts to an operation inside a given address space extend gave by master. The bus slave motions back to the dynamic master with the achievement respect to disappointment of the information exchange [3].

AHB Operation: Before beginning the AMBA AHB exchange, the bus master must be allowed access to the bus. In this procedure as a matter of first importance master attests a demand flag to an authority. Presently the referee will show when the master will get the give of the bus. This choice of giving the entrance to bus is accomplished utilizing some assertion system like need based or round robin component and so forth. An allowed bus master then begins the AHB exchange by first driving an address and control signals. These address and control signals give data around an address, bearing and width of the exchange, burst exchange data if the exchange frames the part of the burst [1]. There are two unique types of burst exchanges that are permitted [1]:

- INCREMENTING: does not wrap at address limits

- WRAPPING: wrap at address limits Every exchange comprises of two stages as:-

- Address and control cycle stage

- Data stage

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X

Volume 04 Issue 03 March 2017

The address stage can't be broadened thus the slaves needs to test the address and control signals amid this stage as it were. Be that as it may, the information stage can be utilizing **HREADY** amplified HREADY = LOW embeds hold up states in the middle of exchange and HREADY = HIGH demonstrates the fruition of the exchange. In typical operation a master is permitted to finish every one of the information moves in a specific burst before a mediator concedes the entrance of bus to another master [1]. Diverse signs utilized by AHB masters are appeared in figure. Main segment in the AMBA framework is the master with complex interface that can start the read or compose exchange to any slave. So it is basic that master is legitimately intended for an AHB framework to work. What's more AHB master usage needs to bolster propel highlights like burst exchanges, split exchange, pipelined characterized operation the as in determination.

### **INDEX-BASED** II. ROUND **ROBIN ARBITER**

In this paper, we show another judge configuration called Index-based Round Robin (IRR) referee that utilizes a slightest as of late served need conspire and accomplish solid reasonableness discretion.

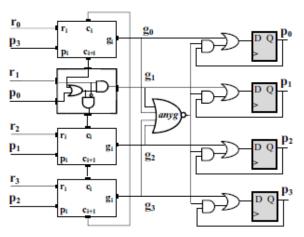

Fig.1 4-input RoR arbiter architecture The proposed authority has littler discretion delay, bring down chip territory and it additionally devours power when less contrasted with the previously mentioned judges. Before portraying the IRR authority architecture, we present an indistinguishable and basic yield in the referee outline

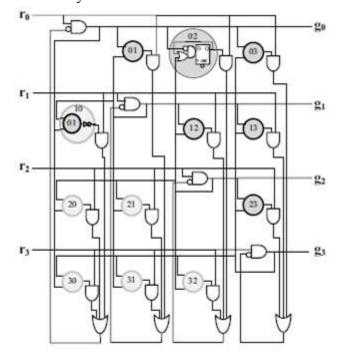

Fig.2 A 4-input Matrix arbiter

### A. Grant Index

### International Journal of Research

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 03 March 2017

Every one of the mediators have a vield cluster, concede whose width is the same as that of input width. Notwithstanding, in reasonable plans, the record of allow signs, g id is additionally created that is utilized to address the conceded ask for in some different parts, for example, control tables, multiplexers and recollections utilized as a part of NoC switches. At the point when a switch crossbar is made of multiplexers, the g id can be associated with determination port of multiplexer to switch the allowed input to the asked for yield port. The width of g id is the log2 of the width of allow. We utilized the g id as the primary yield of our proposed outline and because of lower width of g id, our referee configuration is littler and quicker when contrasted with different authorities. Because of the basic utilization of g id in NoC plan, we consider every one of the authorities shrouded in this paper to produce both concede and g id as yields.

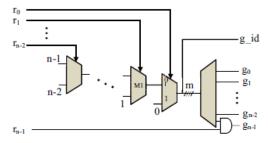

### B. Fixed Priority Arbiter

need Our settled authority is more straightforward and temperate as represented in Figure 8. The need of solicitations is linear and in the rising request where r0 has the most astounding need. The record of initially affirmed demand is changed to the yield as the list of give, g id. At that point the g id is decoded to make the concede The last demand, rn-1 has a signals. streamlined circuit where as opposed to being multiplexed like different solicitations. it is **ANDed** bv gn-1. Consequently, in the event that that lone rn-1 is high, then just gn-1 turns out to be high.

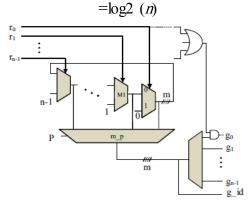

### C. Variable Priority Arbiter

In the event that the g id yield of the settled need mediator of Figure 3 is associated with the last multiplexer, each demand acts as it has the most noteworthy need through climbing request of the circle. For instance, for four solicitations (r0, r1, r2 and r3) the yield of multiplexer, M1 creates a record where r1 has the most astounding need then r2, r3, and r0. In this manner, by further multiplexing of these yields, we can pick an input as the most astounding need ask for as appeared in Figure 4. For instance, when P=1, the yield of multiplexer M1 is chosen and the demand, r1 has the most astounding need. On account of no demand declared, or r0 is stated, the g id issue a similar esteem (i.e. zero). To isolate these two conditions, ORing of solicitations, any r is ANDed with the g0 so that when every one of the solicitations are zero, every one of the stipends will get to be distinctly zero.

Fig. 3 *n*-input fixed priority arbiter, where m

### International Journal of Research

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 03 March 2017

Fig. 4 *n*-input variable priority arbiter **III. RESULTS**

Figure 4 AHB Master SINGLE burst (hburst = 000) compose operation waveforms After the fruition of this limited state machine, any equipment portrayal dialect can be utilized to execute it and checked for usefulness rightness. In this Paper, the state machine is actualized in Verilog HDL dialect and XILINX recreation instrument is utilized to mimic the plan and create the waveforms. The Figure 4 as appeared above shows single burst composes exchange operation with size of the exchange equivalent to 32 bit. At the point when the demand is conceded to the master, begins the exchange by giving location and the control data. The estimation of hburst = 000, shows single burst exchange and hwrite = 1 demonstrates compose exchange. htrans esteem is 10 for exchange showing non the successive exchange. Hresp = 00, demonstrates OK reaction from the slave indicating slave is prepared to get information. Hsize = 010 demonstrating word exchange.

### IV. CONCLUSION

AMBA has kept on giving best answers for SOC interconnects since years. AMBA master is the principle indispensable part of the framework. Thus, outlining it with productive strategy will prompt to territory and timing effective plan of the full framework on chip. This paper plans proficient limited satiate machine outline for AMBA AHB master.

### **REFERENCES**

[1] AMBA Specification Rev 2.0. ARM Ltd., 1999.

- [2] "AMBA Design Kit revision r3p0", Technical Reference Manual, ARM Inc.

- [3] "AHB Example AMBA System", Technical Reference Manual, ARM Inc.

- [4] Rohit Hardia, Prof.Jai Karan Singh, Prof.Mukesh Tiwari "Design And Simulation of a typical high performance AHB Reconfigurable Master For On-chip bus Architecture using Verilog HDL", International Conference on Communication Systems and Network Technologies, IEEE 2011.

- [5] Priyanka Gandhani, Charu Patel "Moving from AMBA AHB to AXI Bus in SoC Designs: A Comparative Study", 2011.