## **International Journal of Research**

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06

May 2017

# Improving the Throughput of the Multiplier Using Vibrant Transistors

#### 1. CHAVALI JAMEEMA, 2. K.CHANDRA RAO

<sup>1</sup>PG Scholar, Department of ECE, Priyadarshini Institute of Technology & Science For Women, Tenali - Vishakapatnam Road, Chintalapudi, Near Tenali, Guntur

<sup>2</sup> Assistant Professor, Department of ECE, Priyadarshini Institute of Technology & Science For Women, Tenali - Vishakapatnam Road, Chintalapudi, Near Tenali, Guntur

### **ABSTRACT:**

The general performance of those systems is dependent around the throughput from the multiplier. Meanwhile, the negative bias temperature instability effect happens whenever a pMOS transistor is under negative bias, growing the brink current from the pMOS transistor, and reducing multiplier speed. An identical phenomenon, positive bias temperature instability, happens when an nMOS transistor is under positive bias. Both effects degrade transistor speed, as well as in the lengthy term; the machine may fail because of timing violations. Digital multipliers are some of the most important arithmetic functional models. Therefore, you should design reliable high-performance multipliers. Within this paper, we advise a maturing-aware multiplier design having a novel adaptive hold logic circuit. The multiplier has the capacity to provide greater throughput with the variable latency and may adjust the AHL circuit to mitigate performance degradation that is a result of the maturing effect. Furthermore, the suggested architecture does apply to some column- or row-bypassing multiplier. The throughput of those programs is dependent on multipliers, and when the multipliers are extremely slow, the performance of entire circuits will disappear.

Keywords: Adaptive hold logic (AHL), negative bias temperature instability (NBTI), positive bias temperature instability (PBTI)

## I. INTRODUCTION

When these molecules diffuse away, interface traps remain. The accrued interface traps between plastic and also the gate oxide interface lead to elevated threshold current (VT), lowering the circuit switching speed.

In addition, negative bias temperature instability happens whenever a pMOS transistor is under negative bias. In cases like this, the interaction between inversion layer holes and hydrogen-passivized Si atoms breaks the Si-H bond produced

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06 May 2017

throughout the oxidation process, producing H or H2 molecules. Digital multipliers are some of the most important arithmetic functional models in lots of programs, like Fourier transform, discrete cosine transforms, and digital filtering. Once the biased current is taken away, overturn reaction happens, lowering the NBTI effect. reaction However, overturn doesn't eliminate the entire interface traps produced throughout the stress phase, and Vth is elevated within the lengthy term. Hence, you should design dependable a highperformance multiplier. The related impact on an nMOS transistor is positive bias temperature instability, which happens when an nMOS transistor is under positive bias. In comparison using the NBTI effect, the PBTI effect is a lot smaller sized oxide/polygene transistors, and for that reason is generally overlooked. However, for top-k/metal-gate nMOS transistors with significant charge trapping, the PBTI effect can't be overlooked [1]. A conventional approach to mitigate the maturing effect is overdesign, including things like guardbanding and gate oversizing however, this method can be quite pessimistic and area and power inefficient. To avert this problem, many NBTI-aware methodologies happen to be suggested. An NBTI-aware technology

mapping technique was suggested to be sure the performance from the circuit during its lifetime. NBTI-aware sleep transistor is built to lessen the aging effects on pMOS sleeptransistors, and also the lifetime stability from the power-gated circuits in mind was enhanced. Wu and Marculescu suggested some pot logic restructuring and pin reordering method, which is dependent on discovering functional symmetries transistor stacking effects. Additionally they suggested an NBTI optimization way in which considered path sensitization. Dynamic current scaling and the bodymaking techniques were suggested to lessen power or extend circuit existence. They, however, require circuit modification or don't provide optimization of specific circuits. Traditional circuits use critical path delay because the overall circuit clock cycle to be able to perform properly. However, the probability the critical pathways triggered is low. Generally, the road delay is shorter compared to critical path. Of these noncritical pathways, while using critical path delay because the overall cycle period can lead to significant timing waste. Hence, the variable-latency design was suggested to lessen the timing waste of traditional circuits. The variable-latency design divides the circuit into a double edged sword: 1)

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06

May 2017

shorter pathways and a pair of) longer pathways. Shorter pathways can execute properly in a single cycle, whereas longer pathways need two cycles to complete. When shorter pathways are triggered frequently, the typical latency of variablelatency designs is preferable to those of traditional designs. For instance, several variable-latency adders were suggested while using speculation technique with error recognition and recovery. A brief path activation function formula was suggested to enhance the precision from the hold logic and also to optimize the performance from the variable-latency circuit. An instruction scheduling formula was suggested to schedule the procedures on no uniform latency functional models and enhance the performance of Very Lengthy Instruction Word processors. Additionally, the critical pathways are split into two shorter pathways that may be unequal and also the clock cycle is placed towards the delay from the longer one [2]. These research designs could lessen the timing waste of traditional circuits to enhance performance, but they didn't think about the aging effect and may not adjust themselves throughout the runtime. A flexible-latency adder design that views the maturing effect was suggested. However, no variable-latency multiplier design that views

maturing effect and adjust the may dynamically continues to be done. Within this paper, we advise a maturing-aware reliable multiplier design having a novel adaptive hold logic circuit. The multiplier is dependent on the variable-latency technique and may adjust the AHL circuit to attain reliable operation drunk of NBTI and PBTI effects. To be precise, the contributions of the paper are summarized the following: novel variable-latency multiplier architecture by having an AHL circuit. The AHL circuit can decide if the input designs require a couple of cycles and may adjust the knowing criteria to make sure that there's minimum performance degradation after considerable aging happens comprehensive analysis and comparison from the multiplier's performance under different cycle periods to exhibit the potency of our suggested architecture a maturing-aware reliable multiplier design way in which is appropriate for big multipliers.

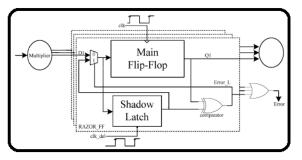

Fig.1.Circuit diagram of Razor Flip flop

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06

May 2017

## II. PROPOSED MODEL

International Journal of Research

Our suggested aging-aware multiplier architecture, including two m-bit inputs, one 2m-bit output, one column- or rowbypassing multiplier, 2m 1-bit Razor switchflops, as well as an AHL circuit. The inputs from the row-bypassing multiplier would be the symbols within the parentheses. Within the suggested architecture, the column- and multipliers row-bypassing could be examined by the amount of zeros either in the multiplicand or multiplication calculate if the operation requires one cycle or two cycles to accomplish. The suggested aging-aware reliable multiplier design, it introduces the general architecture and also the functions of every component as well as describes how you can design AHL that changes the circuit when significant aging happens. When input designs are random, the amount of zeros and ones within the multiplication and multiplicand follows an ordinary distribution. Hence, the 2 agingaware multipliers could be implemented using similar architecture, and also the difference backward and forward bypassing multipliers are based on the input signals from the AHL. Based on the bypassing selection within the columnar row-bypassing multiplier, the input signal from the AHL within the architecture using the column-

bypassing multiplier may be the multiplicand, whereas those of the rowbypassing multiplier be the may multiplication. Razor switch-flops may be used to identify. Single-bit Razor switchflop consists of a primary switch-flop, shadow latch, XOR gate, and mux. The primary switch-flop catches the execution result for that combination circuit utilizing a normal clock signal, and also the shadow latch catches the execution result utilizing a postponed clock signal, that is reduced compared to normal clock signal. When the locked little bit of the cisco kid latch differs from those of the primary switch-flop, what this means is the road delay of the present operation surpasses the cycle period, and also the primary switch-flop catches the wrong result [3]. If errors occur, the Razor switch-flop sets the mistake signal to at least one to inform the machine to execute the operation and inform the AHL circuit that the error has happened. We use Razor switch-flops to identify whether a surgical procedure that is regarded as a 1-cycle pattern can definitely finish inside a cycle. Otherwise, the procedure is executed with two cycles. Even though the execution may appear pricey, the total cost is low since the execution frequency is low. More particulars for that Razor switch-flop are available. The

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06 May 2017

AHL circuit consists of a maturing indicator, blocks, two knowing one mux, something D switch-flop. When the cycle period is simply too short, the column- or row-bypassing multiplier can't complete these procedures effectively, causing timing violations. These timing violations are going to be caught through the Razor switch-flops, which generate error signals. If errors happen frequently and exceed a predefined threshold, this means the circuit has endured significant timing degradation because of the aging effect, and also the aging indicator will output signal 1 otherwise, it'll output to point the maturing effect continues to be not significant, with no actions are essential. The maturing indicator signifies if the circuit has endured significant performance degradation because of the aging effect. The maturing indicator is implemented inside a simple counter that counts the amount of errors over some procedures and it is reset to zero in the finish of individuals procedures [4]. The multiplier array includes rows of carry save adder, by which each row consists of full adder cells. Each FA within the CSA array has two outputs: the sum bit goes lower and also the carry bit would go to the low left FA. The final row is really a ripple adder for carry propagation. The FAs within the AM will always be active no

matter input states. A column-bypassing multiplier is definitely a step up from the standard array multiplier. The AM is really a fast parallel AM. It may be observed that for that FAs in the foremost and third diagonals, two three input bits are: the carry bit from the upper right FA and also the partial product alibi. Therefore, the creation of the adders both in diagonals is, and also the output sum bit is just comparable to the 3rd bit, the sum creation of its upper FA. Hence, the FA is modified to include two tractate gates and something multiplexer. The multiplicand bit ai can be used the selector from the multiplexer to determine the creation of the FA, and ai may also be used because the selector from the tristate gate to show from the input road to the FA. If ai is, the inputs of FA are disabled, and also the sum bit of the present FA is equivalent to the sum bit from the upper FA, thus lowering the power use of the multiplier. A minimal-power row-bypassing multiplier can also be suggested to lessen the game power the AM. The whole process of the reduced-power row-bypassing multiplier is comparable to those of the reduced-power column-bypassing multiplier, however the selector from the multiplexers and also the tristate gates make use of the multiplication. The 2 inputs in the foremost and second

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06 May 2017

the process of recovery happens, lowering the Vth drift. Within this paper, we use 32nm high-k metal gate models.

## **III. CONCLUSION**

This paper suggested a maturing-aware variable-latency multiplier design using the AHL. The multiplier has the capacity to adjust the AHL to mitigate performance degradation because of elevated delay. The metal atoms is going to be progressively displaced after some time, and also the geometry from the wires can change. If your wire becomes narrower, the resistance and delay from the wire is going to be elevated, as well as in the finish, electro migration can lead to open circuits. This problem can also be more severe in advanced process technology because metal wires narrower, and alterations in the wire width may cause bigger resistance variations. That additionally towards the BTI effect that increases transistor delay, interconnect also offers its aging issue, that is known as electro migration. Electro migration happens once the current density is sufficient to result in the drift of metal ions across the direction of electron flow. Additionally, our suggested variable latency multipliers tight performance degradation variable latency multipliers tight on timing waste, but traditional multipliers have to

rows are for FAs. The inputs are bypassed to FAs within the second rows, and also the tristate gates switch off the input pathways towards the FAs. Therefore, no switching activities exist in the very first-row FAs in exchange, power consumption is reduced. However, the FAs should be mixed up in third row since the b3 isn't zero. More particulars for that row-bypassing multiplier can be found. The fundamental concept is to carry out a shorter path utilizing a shorter cycle and longer path using two cycles. Because most pathways execute inside a cycle period that's much smaller sized compared to critical path delay, the variablelatency design has smaller sized average latency [5]. Through simulation, it may be figured that the potential of the carry propagation delay being more than 5 is low. Hence, the cycle period is placed to five, and hold logic is put into inform the machine if the adder can complete the operation inside a cycle period. Another key observation would be that the path delay to have an operation is strongly associated with the amount of zeros within the multiplicands within the column-bypassing multiplier. Aging Model As pointed out, the NBTI effect happens whenever a pMOS transistor is under negative bias current, leading to Vth drift. Once the bias current is taken away,

Available at

https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06 May 2017

think about the degradation brought on by both BTI effect and electro migration and employ the worst situation delay because the cycle period. When the aging effects brought on by the BTI effect and electro migration are thought together, the delay and gratification degradation could be more significant. Fortunately, our suggested variable latency multipliers may be used drunk of both BTI effect and electro migration.

"Modeling and minimization of pMOS NBTI effect for robust nanometer design," in Proc. 43<sup>rd</sup> ACM/IEEE DAC, Aug. 2006, pp. 1047–1052.

[4] R. Vattikonda, W. Wang, and Y. Cao,

[5] D. Baneres, J. Cortadella, and M. Kishinevsky, "Variable-latency design by function speculation," in Proc. DATE, 2009, pp. 1704–1709.

### **REFERENCES**

[1] Y. Chen et al., "Variable-latency adder (VL-Adder) designs for low power and NBTI tolerance," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 18, no. 11, pp. 1621–1624, Nov. 2010.

[2] R. Vattikonda, W. Wang, and Y. Cao, "Modeling and minimization of pMOS NBTI effect for robust naometer design," in Proc. ACM/IEEE DAC, Jun. 2004, pp. 1047–1052.

[3] Y. Lee and T. Kim, "A fine-grained technique of NBTI-aware voltage scaling and body biasing for standard cell based designs," in Proc. ASPDAC, 2011, pp. 603–608.