p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06 May 2017

# Closed Loop Control of Renewable Source Fed Asymmetrical PWM Full Bridge Converter

V.Jagadeesh M-tech Student Scholar Department of Electrical & Electronics Engineering, VITAM College of Engineering, sontyam; Visakhapatnam (Dt); A.P, India.

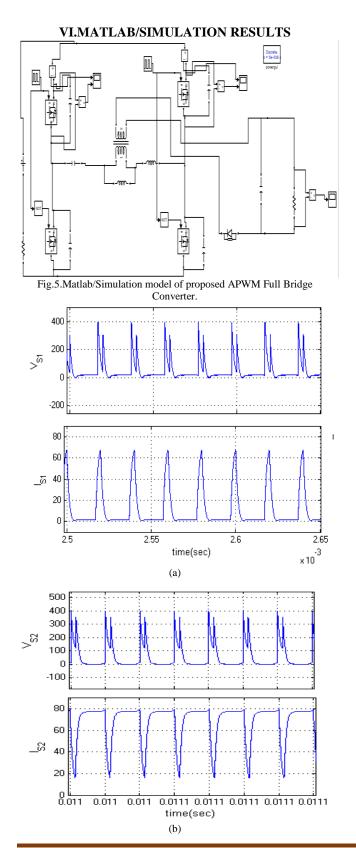

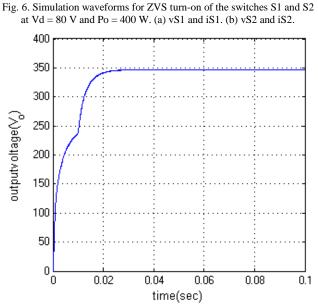

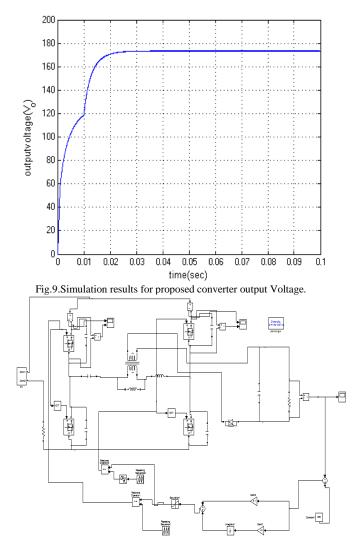

Abstract- This paper presented a closed loop control of asymmetrical PWM full bridge converter; Renewable energy and distributed generation are getting more and more popular, wind turbines, and fuel cells. The renewable energy sources need the power electronics interface to the utility grid because of different characteristics between the sources and the grid. No matter what renewable energy source is utilized, extended voltage and power output, less maintenance and higher fault tolerance, the asymmetrical PWM full bridge converter are good, for utility interface of various renewable energy sources. This dissertation proposes a new PWM converter topology and control scheme. Compared to traditional converter, they have enhanced system reliability to no shoot-through problems and lower switching loss with the help of using power closed loop control. The closed loop control, it theoretically eliminates the inherent current zero-crossing distortion of the single-unit asymmetrical type PWM full bridge converter. In addition, the closed loop control can greatly reduce the ripple current or cut down the size of passive components by increasing the equivalent switching frequency. An asymmetrical full bridge PWM technique is proposed for closed loop control of renewable energy The proposed approach is to cut down the sources. switching loss of power control. At the same time, this PWM full bridge leads to current ripple reduction, and thus reducing ripple-related loss in filter components. PWM with feedback controlling is employed for the voltage control of the system. A power management system is designed for the proposed system to manage power flow among different sources.

Index Terms—Asymmetrical pulse-width modulated (PWM), full-bridge converter, soft switching, Closed Loop Controller, PV System.

# I. INTRODUCTION

An asymmetrical full bridge boost DC/DC switching converter is proposed to improve renewable systems. Such a new step-up power converter in a PV system provides a low input current ripple injected into the photovoltaic generator, and at the same time provides a low voltage ripple to the load [1-2]. Low-ripple and high boosting conditions make this converter an ideal candidate for photovoltaic systems design, in particular for grid-connected applications. The converter circuitry is analyzed, and a design procedure is proposed in terms of Y. Naveen Kumar Assistant Professor Department of Electrical & Electronics Engineering, VITAM College of Engineering, sontyam; Visakhapatnam (Dt); A.P. India.

typical photovoltaic systems requirements [3-5]. Photovoltaic power systems are efficient alternatives to provide electrical energy providing redundancy for critical applications, energy generation, and the reduction of traditional energy generation that impacts the environment. Similarly, photovoltaic generators have been intensively used in residential applications and autonomous and portable applications. Photovoltaic systems require a power electronics interface to define their operating point at optimal conditions for any load. For that DC/DC and DC/AC converters are widely used [6-8]. The double-stage approach is widely accepted due to its application in distributed generation system based on multiple generators, as well as in stand-alone DC applications, where a single DC/DC converter is required [9-10].

The PV applications commonly adopt boosting converters for grid-connected applications due to the requirement of increasing the voltage to the grid connected inverter operating conditions. Other characteristics required in PV applications are a low current ripple injected to the PV and high conversion efficiency [11]. The current ripple magnitude is an important factor in the selection of power converters for PV applications because high current ripples produce an oscillation around the maximum power point (MPP) that reduces the energy extracted from the PV generator. So that most commonly employed converter is boost converter, but in such a boost converter, the current ripples injected to the PV generators depend on the inductor size, switching frequency, input capacitor, and high frequency power source impedance; therefore, in order to reduce the current ripple, it is necessary to increase the converter inductance or input capacitance [12-14]. This can be addressed by using an additional filter between the PV generator and the power converter, also increasing power losses, size, weight, cost, and the order of the system.

# **II. PHOTOVOLTAIC SYSTEM**

Photovoltaic (PV) is a method of generating electrical power by converting solar power into direct current electricity, using semiconductors that exhibit the

photovoltaic effect. Photovoltaic power generation employs solar panels composed of a number of solar cells containing a photovoltaic material. Materials now used for photovoltaic system include mono crystalline silicon, cadmium telluride, poly crystalline silicon and amorphous silicon. Due to the increased demand for different renewable energy sources, the manufacturing of solar cells and photovoltaic arrays has advanced considerably in recent years.

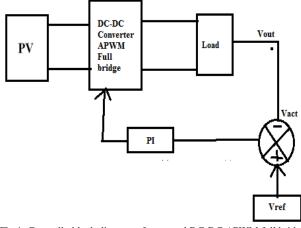

Fig.1. Generally block diagram of proposed DC-DC APWM full bridge Converter with Closed Loop.

(PV) cells are environmentally friendly once they are made but have some other drawbacks. They produce a low voltage that is not compatible with the electric grid and common appliances. This means that the power must be converted into a higher voltage and then inverted to an AC voltage. Also, the PV voltage is prone to fluctuations due to variables like shading and angle of the sun. One method used to produce a large DC voltage from PV modules is to put several in series. The power from the PV modules are put directly into a DC-AC inverter. This system does not require a DC-DC converter that is the power loss to this part of the system does not exist. There are however several large drawbacks. If there is any shading occurs on any of the PV modules the voltage will drop across the whole system and will possibly make the power produced by the rest of the modules unusable. This system also limits the control of the DC voltage going into the DC-AC inverter again putting limits to when the power from the PV can be used. Another method used is to dedicate a DC-DC converter and a AC-DC inverter [2] to each module. The power from the PV module is directed into a DC-DC converter that has high gain capabilities and then to a DC bus. It is then send to a DC-AC inverter and then to the grid or a load. This method makes shading less of an issue as each module has its own DC-DC converter. This however introduces new sources of power loss to the system. The DCDC converter is also

required to produce a large gain which can put strain on its components and also make the converter less efficient

# III ANALYSIS OF A PWM FULL-BRIDGE CONVERTER

# A. Circuit Configuration and Operation Principle

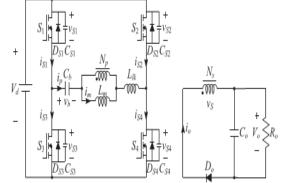

A circuit configuration of the highly efficient APWM full bridge converter for low input voltage range is shown in Fig.2. The configuration of the proposed converter is basically similar to that of the conventional full-bridge converter except for the dc blocking capacitor and the secondary side of the transformer. The primary side of the transformer consists of the primary winding turns  $N_p$ , the four switches, and the dc blocking capacitor  $C_b$ . The secondary side has the secondary winding  $N_s$ , the output diode  $D_o$ , and the output capacitor  $C_o$ .

Fig.2.Circuit diagram of the proposed APWM full-bridge converter.

To analyze the steady-state operation of the proposed APWM full-bridge converter, the following assumptions are made.

- 1) The transformer is modeled as an ideal transformer with the primary winding turns  $N_p$ , the secondary winding turns  $N_s$ , the magnetizing inductance  $L_m$ , and the leakage inductance  $L_{lk}$

- 2) All switches  $S_1$ - $S_4$  are considered as ideal switches except for their body diodes and output capacitors ( $C_{S1}$ = $C_{S2}$ = $C_{S3}$ = $C_{S4}$ = $C_{oss}$ ).

- 3) The dc blocking capacitor  $C_b$  and the output capacitor  $C_o$  are large enough to neglect the voltage ripple on it, so the voltages across  $C_b$  and  $C_o$  are constant.

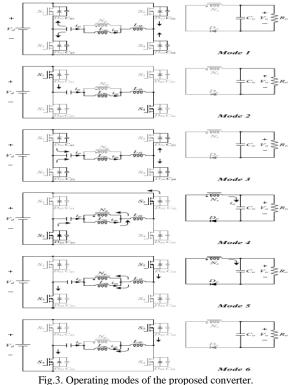

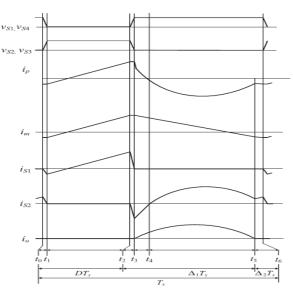

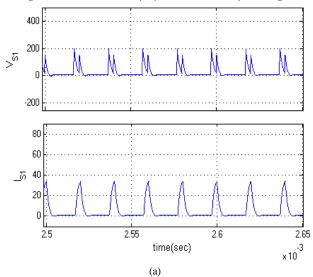

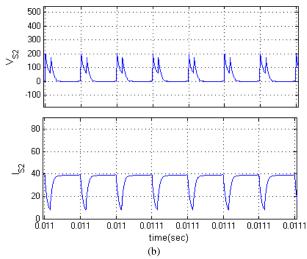

While the switch  $S_1$  ( $S_4$ ) operates with a duty ratio D, depending on the input voltage and load condition, the switch  $S_2$  ( $S_3$ ) operates with a duty ratio 1–D. In other words, the switches  $S_1$  ( $S_4$ ) and  $S_2$  ( $S_3$ ) are operated asymmetrically. Therefore, the circulating current loss of the primary side can be eliminated because the proposed converter has no freewheeling period. Fig. 3 represents the operating modes, and Fig.4 represents the theoretical waveforms of the proposed converter under a steady-state condition. The operation of the proposed converter can be divided into six modes during a switching period  $T_s$ .

**Mode 1** [ $t_0$ ,  $t_1$ ]: At  $t_0$ , the switches  $S_2$  and  $S_3$  are turned off. The primary current  $i_p$  discharges the output capacitances  $C_{S1}$  and  $C_{S4}$  of the switches  $S_1$  and  $S_4$  and charges the output capacitances  $C_{S2}$  and  $C_{S3}$  of switches  $S_2$ and  $S_3$ . The interval of this mode is very short and negligible because the output capacitances  $C_{oss}$  of the switches are very small. Thus, the primary current  $i_p$  and the magnetizing current  $i_m$  are regarded as constant value.

**Mode 2** [ $t_1$ ,  $t_2$ ]: At  $t_1$ , when the voltages  $v_{S1}$  and  $v_{S4}$  across the switches  $S_1$  and  $S_4$  become zero, the negative current flows through their body diodes  $D_{S1}$  and  $D_{S4}$ before the switches  $S_1$  and  $S_4$  are turned on. Then, ZVS operation is achieved with the turn-on of the switches  $S_1$  and  $S_4$ , and the resonance occurs between the dc blocking capacitor  $C_b$  and the primary inductor  $L_m + L_{lk}$  of the transformer, but resonance effect does not appear because the resonant period is much longer than one switching period  $T_s$ . Thus, by the difference between the voltages of the input and the dc blocking capacitor  $C_b$ , the direction of the primary current  $i_p$  is changed and kept almost linearly as follows:

$$i_p(t) = i_p(t_1) + \frac{V_d - V_b}{L_m + L_{lk}}(t - t_1)$$

(1)

Where  $V_d$  is the input voltage and  $V_b$  is the average voltage across the dc blocking capacitor  $C_b$ .

$C_{S1}$ ,  $C_{S4}$  of  $S_1$ ,  $S_4$  and discharges the output capacitances  $C_{S2}$ ,  $C_{S3}$  of  $S_2$ ,  $S_4$ . Similar to Mode 1, the primary current  $i_p$  and the magnetizing current  $i_m$  are regarded as constant value.

**Mode 4** [*t*<sub>3</sub>, *t*<sub>4</sub>]: At  $t_3$ , similar to Mode 2, ZVS turn-on of the switches  $S_2$  and  $S_3$  is achieved. The energy stored in the magnetizing inductance is delivered to the secondary side of transformer, and the voltage across the magnetizing inductance  $L_m$  is clamped by the reflected output voltage as

$$L_m \frac{di_m(t)}{dt} = -\frac{V_o}{n} \tag{2}$$

Where  $n=N_s/N_p$ . Because the difference between the primary current  $i_p$  and the magnetizing current  $i_m$  is reflected in the output current  $i_o$ , the magnetizing current  $i_m$  is decreased as

$$i_m(t) = i_p(t_3) - \frac{V_o}{nL_m}(t - t_3)$$

(3)

The resonance occurs between the dc blocking capacitor  $C_b$  and the leakage inductance  $L_{lk}$  of the transformer. The voltage across the leakage inductance  $L_{lk}$  of primary side is the difference between  $V_d + V_b$  and the reflected output voltage  $V_o/n$  from the secondary side. Thus, the state equations can be written as follows:

$$L_{lk}\frac{di_p(t)}{dt} = -V_d - V_b + \frac{V_o}{n} \tag{4}$$

$$C_b \frac{dv_b(t)}{dt} = i_p(t) \tag{5}$$

Solving (4) and (5), the primary current $i_p$  is

$$i_{p}(t) = i_{p}(t_{3}) \cos \omega_{r}(t - t_{3}) + \frac{V_{o}/n - V_{d} - V_{b}}{Z_{r}} \sin \omega_{r}(t - t_{3})$$

(6)

Where the resonant angular frequency  $\omega_r$  and the impedance  $Z_r$  of the resonant circuit are

$$Z_r = \sqrt{\frac{L_{lk}}{C_b}} \quad \omega_r = \frac{1}{\sqrt{L_{lk}C_b}} \tag{7}$$

**Mode 5** [ $t_4$ ,  $t_5$ ]: At  $t_4$ , the primary current  $i_p$  becomes zero and changes its direction. Also, the magnetizing current im changes its direction during this interval. The output current  $i_o$  approaches zero at the end of this mode with resonant characteristics. When the output current  $i_o$  becomes zero, this mode ends.

**Mode 6** [ $t_5$ ,  $t_6$ ]: At  $t_5$ , because the resonance launched in Mode 4 is ended, the output current  $i_o$  becomes zero. However, the output diode  $D_o$  is maintained to on-state until the switches  $S_2$  and  $S_3$  are turned off. During this

# **International Journal of Research**

Available at https://edupediapublications.org/journals

mode, the primary current $i_p$  is equal to the magnetizing current  $i_m$ . Thus, ZCS turn-off of the output diode  $D_o$  is achieved.

#### **B.** Steady-State Analysis

While the switches  $S_1$  and  $S_4$  operate with a duty ratio D, the difference between the input voltage  $V_d$  and the average voltage  $V_b$  of the dc blocking capacitor  $C_b$  is applied on the inductor of the transformer primary side. While the switches  $S_2$  and  $S_3$  operate with a duty ratio 1-D, the reflected output voltage  $V_o/n$  is applied on the inductor of the transformer primary side and the output diode  $D_o$  is turned-on. Since the resonant period of the resonant network is much longer than the dead-time duration, equations of the primary current  $i_p$  from (1) and (2) are derived as follows:

$$i_{p}(t_{3}) = i_{p}(t_{1}) + \frac{V_{d} - V_{b}}{L_{m} + L_{lk}} DT_{s}$$

$$i_{p}(t_{1}) = i_{p}(t_{3}) - \frac{V_{o}}{nL_{m}} (1 - D)T_{s}$$

(9)

From the resonance of the primary side in Modes 4 and 5, since the leakage inductance  $L_{lk}$  is much smaller than the magnetizing inductance  $L_m$ , the leakage inductance  $L_{lk}$  is negligible. Therefore, the following equation can be obtained:

$$V_d + V_b \simeq \frac{V_o}{n} \tag{10}$$

From (8) to (10), the voltage gain between the input voltage  $V_d$  and output voltage  $V_o$  is expressed as follows:

$$\frac{V_o}{V_d} \simeq \frac{L_m}{L_m + L_{lk}} 2nD \simeq 2nD \tag{11}$$

Because the leakage inductance  $L_{lk}$  is negligible, the average voltage  $V_b$  of the dc blocking capacitor  $C_b$  is expressed from (10) and (11) as shown in

$$V_b = V_d(2D - 1) \tag{12}$$

Due to the charge balance of the dc blocking capacitor  $C_b$ , the average value of the primary current  $I_p$  is zero in the steady state. Thus, the relation between the average values of the magnetizing current  $I_m$  and average output current  $I_o$  can be determined as follows:

$$I_m - I_p = I_m - \frac{1}{T_s} \int_0^{T_s} i_p(t) dt = nI_o.$$

(13)

From Fig.4, the average magnetizing current  $I_m$  can also be obtained by

$$I_m = \frac{i_p(t_1) + i_p(t_3)}{2}.$$

(14)

Fig.4.Theoretical waveforms of the proposed converter.

From (1), (13), and (14), the currents  $i_p(t_1)$  and ip  $(t_3)$  are given by

$$i_{p}(t_{1}) = nI_{o} - \frac{(1-D)T_{s}}{nL_{m}}V_{o}$$

$$i_{p}(t_{3}) = nI_{o} + \frac{(1-D)T_{s}}{nL_{m}}V_{o}$$

(15)

(16)

Using (13)-(16), the resonant current (6) can be represented by

$$i_{p}(t) = \left(nI_{o} + \frac{(1-D)T_{s}}{nL_{m}}V_{o}\right)\cos\omega_{r}(t-t_{3}) - \frac{V_{o}}{nL_{m}\omega_{r}}\sin\omega_{r}(t-t_{3}).$$

$$(17)$$

## IV SOFT-SWITCHING CONDITIONS

#### A. ZVS Condition of the Power Switches

For ZVS turn-on of  $S_1$  and  $S_4$ , the primary current  $i_p(t_1)$  should be negative before  $S_1$  and  $S_4$  are turned on. Thus, from (15), ZVS condition can be expressed as follows:

$$nI_o - \frac{(1-D)T_s}{nL_m}V_o < 0.$$

(18)

Equation (18) is arranged by the min–max theorem as

$$\frac{n^2 L_m I_{o,\max}}{V_o} = \frac{n^2 L_m}{R_{o,\min}} < (1 - D_{\max}) T_s$$

(19)

Where  $I_{o,max}$  is the maximum output current,  $R_{o,min} = V_o/I_{o,max}$  is the minimum output resistance, and  $D_{max}$  is the maximum duty ratio of the switches  $S_I$  and  $S_4$  under the minimum input voltage  $V_{d,min}$ . From (3.11),  $D_{max}$  can be described as

International Journal of Research Available at https://edupediapublications.org/journals

(20)

$$D_{\text{max}} \simeq \frac{V_o}{2nV_{d,\min}}.$$

According to the variations of the input voltage  $V_d$  and turn ratio, the duty ratio of the switches  $S_1$  and  $S_4$ . Thus, from (19) and (20), the magnetizing inductance  $L_m$  should be designed to satisfy ZVS condition as follows:

$$L_m < \left(1 - \frac{V_o}{2nV_{d,\min}}\right) T_s \cdot \frac{R_{o,\min}}{n^2} \tag{21}$$

Where  $T_s$  is a switching period. According to the variation of the duty ratio D, the critical magnetizing inductance value  $L_m$  to satisfy the ZVS turn-on condition of the switches The ZVS turn-on condition of the switches  $S_2$  and  $S_3$  can be expressed with the same manner of ZVS condition of the switches  $S_1$  and  $S_4$ . Thus, ZVS operation of  $S_2$  and  $S_3$  can be achieved when the primary current $i_p$  ( $t_3$ ) is positive. From (16), ZVS condition of  $S_2$  and  $S_3$  is expressed as follows:

$$nI_o + \frac{(1-D)T_s}{nL_m}V_o > 0.$$

(22)

The left side terms of (22) are always positive regardless of load variations. Therefore, ZVS operation of the switches  $S_2$  and  $S_3$  can always is satisfied.

Another ZVS turn-on operation requires a sufficient dead time between two switch pairs to absolutely discharge the voltage across the output capacitance  $C_{oss}$  of the switches. Because  $i_p(t_1) = i_m(t_1)$  is regarded as constant value during the dead time, the minimum dead time  $\Delta t_{dead}$  can be calculated as

$$\min\{|i_p(t_1)|, |i_p(t_3)|\} \ge 4C_{oss}\frac{dV_d}{dt}$$

(23)

From (15) and (16), the primary current  $i_p(t_3)$  is always larger than the absolute value of the primary current  $i_p(t_1)$ . Therefore, (23) can be simplified as

$$\Delta t_{dead} \ge \frac{C_{oss}V_d}{|i_p(t_1)|/4}.$$

(24)

The primary current  $i_p(t_l)$  should be negative for ZVS operation. Thus, (3.24) can be expressed as shown in

$$\Delta t_{dead} \ge \frac{4C_{oss}V_d}{\frac{(1-D)T_s}{nL_m}V_o - nI_o} \tag{25}$$

The minimum dead time  $\Delta t_{dead}$  should be considered in the practical design of the magnetizing inductance because  $\Delta t_{dead}$  is always smaller than  $(1-D_{max}) T_s$ .

#### V. ZCS Condition of the Output Diode

To achieve the ZCS turn-off condition of the output diode <sub>Do</sub>, the resonant angular frequency  $\omega$ r should be larger than the critical angular frequency  $\omega_{rc}$ . Because the critical condition is ip (Ts) =  $i_m(T_s)$  at  $\Delta_2 T_s = 0$  and  $D = D_{max}$ , the critical angular frequency  $\omega_{rc}$  can be described considering the negligible dead-time duration of the power switches as follows:

$$\left(\frac{n^2 L_m}{R_{o,\min}} + t_{S2,\min}\right) \cos\omega_{rc} t_{S2,\min}$$

$$-\frac{1}{\omega_{rc}} \sin\omega_{rc} t_{S2,\min} - \frac{n^2 L_m}{R_{o,\min}} + t_{S2,\min} = 0$$

(26)

Where  $t_{S2,min}$  is the minimum turn-on duration of the switches  $S_2$  and  $S_3$ . The magnetizing inductance  $L_m$  is generally designed for the magnetizing current  $i_m$  ( $t_1$ ) to be a small negative value to minimize the conduction loss of the converter. By this assumption, (26) can be obtained as follows:

$$\tan \omega_{rc} t_{S2,\min} \simeq \omega_{rc} \frac{n^2 L_m}{R_{o,\min}} + \omega_{rc} t_{S2,\min}$$

(27)

From (21), (27) is expressed as shown in

$$\tan \omega_{rc} t_{S2,\min} < 2\omega_{rc} t_{S2,\min} \tag{28}$$

Thus, the critical angular frequency  $\omega_{rc}$  can be calculated using a numerical method as shown in

$$\omega_{rc} \approx \frac{\pi + 1.462}{t_{S2,\min}} = \frac{\pi + 1.462}{(1 - D_{\max})T_s}$$

(29)

From (29), the dc blocking capacitance  $C_b$  must satisfy the following relation:

$$C_b \le \frac{1}{\omega_{rc}^2 L_{lk}} \tag{30}$$

According to the variation of the duty ratio D, the critical resonant capacitance  $C_b$  to satisfy the ZCS turn-off condition of the output diode  $D_o$ .

# **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06 May 2017

# **International Journal of Research**

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 06 May 2017

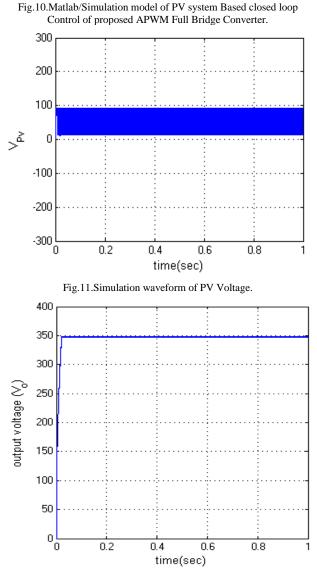

Fig.12.Output Voltage of Closed loop APWM full bridge Converter.

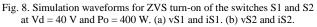

## **VII.CONCLUSION**

Renewable system using asymmetrical boost converter with PWM controlling is designed and analyzed. The converter was developed by breaking the symmetry of traditional boost converters. The Boost converter with Coupled Inductors is used here and for a given small input dc voltage, a high gain. Different high boost ratio dc-dc converter circuit were presented to show how to design low-cost and high-efficiency converters for renewable energy such as solar panel integration applications, fuel cell, uninterruptable power supplies and designed procedure has been developed and verified by simulation. All power switches operate under ZVS and output diode operates under ZCS without extra components. Also, all

power switches are clamped to the input voltage. Thus, the proposed converter has the structure to minimize power losses. These advantages make the proposed converter suitable for fluctuating input voltage on renewable energy conversion systems.Compared to traditional converter, they have enhanced system reliability to no shoot-through problems and lower switching loss with the help of using power closed loop control. The closed loop control, it theoretically eliminates the inherent current zero-crossing distortion of the single-unit asymmetrical type PWM full bridge converter. In addition, the closed loop control can greatly reduce the ripple current or cut down the size of passive components by increasing the equivalent switching frequency.

#### REFERENCES

[1] J. Zhang, H. Wu, X. Qin, and Y. Xing, "PWM plus secondary-side phase-shift controlled soft-switching full-bridge three-port converter for renewable power systems," IEEE Trans. Ind. Electron., vol. 62, no. 11, pp. 7061–7072, Nov. 2015.

[2] K. C. Tseng, J. Z. Chen, J. T. Lin, C. C. Huang, and T. H. Yen, "High step-up interleaved forward-flyback boost converter with three winding coupled inductors," IEEE Trans. Power Electron., vol. 30, no. 9, pp. 4696–4703, Sep. 2015.

[3] A. K. Rathore, A. K. S. Bhat, and R. Oruganti, "Analysis, design and experimental results of wide range ZVS active-clamped L-L type current fed dc/dc converter for fuel cells to utility interface," IEEE Trans. Ind. Electron., vol. 59, no. 1, pp. 473–485, Jan. 2012.

[4] A. I. Bratcu, I. Munteanu, S. Bacha, D. Picault, and B. Raison, "Cascaded dc–dc converter photovoltaic systems: Power optimization issues," IEEE Trans. Ind. Electron., vol. 58, no. 2, pp. 403–411, Feb. 2011.

[5] B. R. Lin and J. Y. Dong, "New zero-voltage switching DC–DC converter for renewable energy conversion systems," IET Power Electron., vol.5, no. 4, pp. 393–400, Apr. 2012.

[6] Y. Shin, C. Kim, and S. Han, "A pulse frequency modulated full bridge DC/DC converter with series boost capacitor," IEEE Trans. Ind. Electron., vol. 58, no. 11, pp. 5154–5162, Nov. 2011.

[7] I.-H. Cho, K. Cho, and G. Moon, "A new phase-shifted full-bridge converter with maximum duty operation for server power system," IEEE Trans. Power Electron., vol. 26, no. 12, pp. 3491–3500, Dec. 2011.

[8] Z. Chen, Q. Zhou, J. Xu, and X. Zhou, "Asymmetrical pulse-width modulated full-bridge secondary dual resonance DC–DC converter," J. Power Electron., vol. 14, no. 6, pp. 1224–1232, Nov. 2014.

[9] Z. Ye, P. K. Jain, and P. C. Sen, "A full-bridge resonant inverter with modified phase-shift modulation for high-frequency AC power distribution systems," IEEE Trans. Ind. Electron., vol. 4, no. 2, pp. 242–247, Oct. 2007.

[10] Y. C. Hsieh and C. S. Huang, "Li-ion battery charger based on digitally controlled phase-shifted full-bridge converter," IET Power Electron., vol. 5, no. 6, pp. 755–764, Oct. 2009.

[11] Y. Jang and M. M. Jovanovi' c, "A new family of full-bridge ZVS converters," IEEE Trans. Power Electron., vol. 19, no. 3, pp. 701–708, May 2004.

[12] S. H. Lee, C. Y. Park, J. M. Kwon, and B. H. Kwon, "Hybrid-type full-bridge DC-DC converter with high efficiency and wide input range," IEEE Trans. Power Electron, vol. 30, no. 8, pp. 4156–4164, Aug. 2015.

[13] B. R. Lin, J. Y. Dong, and J. J. Chen, "Analysis and implementation of a ZVS/ZCS DC–DC switching converter with voltage step-up," IEEE Trans. Ind. Electron., vol. 58, no. 7, pp. 2962–2971, Jul. 2011.

[14] H. Wu, P. Xu, and Y. Xing, "Series-input interleaved forward converter with a shared switching leg for wide input voltage range applications," IEEE Trans. Ind. Electron., vol. 60, no. 11, pp. 5029–5039, Nov. 2013.

# **AUTHOR'S DETAILS:**

V.JAGADEESH Received his B.Tech Degree in EEE from VITS College of Engineering, Sontyam, Visakhapatnam, A.P in 2015. At Present pursuing M.Tech in VITAM College of Engineering, Sontyam, Visakhapatnam, A.P, India.

Y.NAVEEN KUMAR Received his B.Tech Degree in EEE from Sai Prakash College of Engineering in 2007 and M.Tech in Reliability Engineering from IIT Kharagpur in 2009. At Present he is working as Assistant Professor in Department of EEE, VITAM College of Engineering

Sontyam, Anandapurm, Visakhapatnam, A.P, India.