Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

### An Efficient VLSI Architecture of a Clock-gating Turbo Decoder

P Priyanka, P.G.STUDENT, Kakinada Institute of Engineering and Technology M Devi Satya Priya, Asst.prof, Kakinada Institute of Engineering and Technology

### **Abstracts**

Wireless sensor network can be considered to be energy constrained wireless scenarios, since the sensors are operated for extended periods of time, while relying on batteries that are small, lightweight and inexpensive. The conventional turbo decoder architecture requires high chip area and hence high power consumption. This motivated the proposed system to design the decoder architecture with high throughput, less decoding iteration and less memory requirement. Clock gating is a technique that can be used to control the power dissipated by clock net. The proposed work is implemented using clock gating technique in order to reduce the power consumption. The previous turbo decoder architectures uses optimal-log based algorithm which has the complexity about 75% and hence leads to time and energy consumption due to sequential operations. Where as the proposed architecture uses the fundamental Add Compare Select (ACS) operation. Due to the parallel processing operation of ACS blocks the proposed architecture tend to have low processing steps, so that low transmission energy and less complexity about 71%. The proposed work implementation has a throughput of 1.03 Mb/s, memory requirement of 128 Kbps, power consumption of about 0.016(mV) and requires 0.010(A) of current. Comparing to the optimal-log based algorithm in the proposed lookup table based architecture the complexity is reduced by 4% and by implementing the clock-gating technique the power consumption is reduced by 38%.

Keywords— ACS block, Clock gating technique, Lookup table architectures, Throughput, Transmission energy.

### 1. INTRODUCTION

VLSI technology defined the edge of the ASIC business, which accelerated the push of powerful embedded systems in to adorable products. A Wireless Sensor Network is spatially distributed autonomous to monitor physical or environmental conditions in order to send their data through the network to a

main location. But, designing the decoder on the receiver side encounters many challenges like algorithm complexity, large silicon area, high power consumption and low throughput. The proposed work is concentrated on designing the parallel turbo decoder which fits for the Wireless Sensor network applications. Turbo codes are on the verge of finding their way in numerous cutting edge applications

# ®

### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

like cellular communications and satellite communications. A turbo decoder is composed of modules that work in an iterative scheme. Some alternative algorithms exist for the algorithm incorporated in these decoder modules. Recent Application-Specific Integrated Circuit (ASIC) based decoder architectures have been designed [1] for achieving a high transmission throughput, rather than for low transmission energy. This addresses design and implementation aspects of parallel turbo decoders that reach the 326.4 Mb/s peak data-rate using multiple soft-input soft-output decoders that operate in parallel.

The Error-Control Coding (ECC) implemented in Wireless Sensor Networks (WSN), to determine the energy efficiency of the specific ECC implementations in WSN are been proposed [2]. ECC provides coding gain, resulting in transmission energy savings, at the cost of added decoder power consumption but is not an error-control code, as there is no encoding. C.Schlegel (2011) defined the physical layer (PHY) and Medium Access Control (MAC) sub layer specifications for less data rate wireless connectivity with fixed, portable, and moving devices with no battery very limited battery consumption requirements. The energy consumption of Amplitude Shift Key(ASK) is (i.e.14.013 mJ) less than Offset Quadrature Phase Shift Key(OQPSK) (i.e. 15.401 mJ) but due to its high sensitivity to noise this modulation

scheme is rejected and OQPSK is chosen[3]. A modified version of the BCJR algorithm, that has redesigned vigorously is also used [4]. There are several simplified versions of the Maximum A posteriori Probability (MAP) algorithm, namely the log-MAP and the maxlog-MAP algorithms. But in this case power consumption is high and it is sensitive to signal that produces more noise. J.M.Mathana (2014) presents VLSI architecture for an efficient turbo decoder using sliding window method. The speed of the implementedarchitecture improved is bv modifying the value of the branch metrics [5]. But this method occupies a large amount of chip area.A low-complexity ACS compare and select) architecture is introduced in WSN decoder design. The entire decoder architecture is coded using Verilog HDL and it is synthesized using Xilinx EDA with Spartan 3E FPGA[6]. But this design is said to be more complicated and requires more cost because of large usage of components. A flexible and efficient VLSI architecture to solve the memory conflict problem for highly turbo decoders targeting parallel standard 3G or 4G wireless communication systems is been proposed [7].But this method achieves a high throughput only when the clock rate is high it doesn't support for low clock rate. Guido Masera (2013) proposes a VLSI decoding architecture for concatenated convolution codes. (i) the possibility to switch on-the-fly from the Universal Mobile

## ₹® (R)

### **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

Telecommunication System (UMTS) turbo decoder to the WiMax duo-binary turbo decoder with a limited resources (ii) the design of a parallel, collision free Wireless Max decoder architecture [8].But this method doesn't achieve a better memory space, it uses a very large memory space.

This motivates the employment of the lookup table based algorithms in energy-constrained scenarios, since it approximates the optimal Log more closely than the Max-Log [9] and therefore does not suffer from the associated coding gain degradation. By this survey it is understandable that, no lookup table based ASICs have been specifically designed for the energy constrained scenarios. Previous lookup table based turbo decoder designs were developed as a part of the drive for higher throughputs, processing although throughputs have since been eclipsed by the Max-Log architectures. This opens the door for a new generation of LUT based ASICs that exchange processing throughput for energy efficiency. Taking all these points in to account, the proposed work motivates to make the decoder architecture energy efficient. This work introduces the clock gating technique in decoder architecture. By using the clock gating technique the power consumed by the unused gates during the decoding process can be eliminated. The proposed work organizes as follows. The conventional LUT based architecture is discussed in section 2. Section 3

deals with the proposed decoder architecture and its algorithm. Section 4 describes about the results and discussions of the work. Section 5 deals with the conclusion and future work.

### 2. CONVENTIONAL LOOKUP TABLE BASED ARCHITECTURE

The existing system design, consist of the Lookup table log based architecture into its most functional add compare select (ACS) operations and perform them using a novel low-complexity ACS unit. The proposed work also produces the simulation for energy efficiency, and power reduction [10]. The Max-Log algorithm [9] appears to demonstrate itself to both high-throughput scenarios, as well as to the above mentioned energy constrained scenarios. The low turbo decoder energy consumption is implied by Max-Log algorithm [10] which achieves complexity. The low-complexity is achieved at the cost of reducing the coding gain by 0.5 dB compared to the optimal Log algorithm increasing the required transmission energy by 10%. This disadvantage of the Max-Log outweighs that it is attractively complexity, by optimizing the overall energy consumption of sensor nodes that are separated by long distance.

### 2.1 Turbo coding

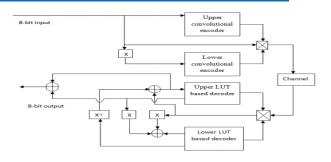

A turbo encoder consists of a parallel linking of two relatively low constraint length

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

convolution codes as depicted in figure 1. A pseudo random interleaver separates these two component codes (ENC1 and ENC2). The size of the interleaver determines the performance of the code, which is better for larger values of N. The turbo code operates as a block code transforming the input bits into output bits that are transmitted. For every new input block, the encoder is said to start in a known initial state. In order to have an end state, some extra input bits, called tail bits are generated. Generally this is done only for ENC1. This method is extended and tail bits are added after the interleaver also, in order to force ENC2 in a known end state. This scheme is referred as full termination [11]. Another option is to force both the encoders to its known end state is to use precursor bits as in. Both schemes reduce the throughput a little, but improve the decoding performance and allow the optimization of the decoder module.

### 2.2 Decoder Setup

A maximum of the turbo decoder would be prohibitively complex. The iterative decoding scheme is a clever solution for this problem. Both of the decoder modules (DEC1 andDEC2) produces an increasingly better correction term which is appropriately deinterleaved and used as a priori information by the next module. The other inputs of a decoding module are the log ratios of the received symbols,

FIG.1: TURBO ENCODER AND DECODER SCHEME.

Turbo decoder architecture uses 3rd Generation Partnership Project (3GPP) and Universal Mobile Telecommunication System (UMTS) standard as an example to introduce the typical turbo coding schemes. This algorithm includes convolution code algorithm and the SISO decoding algorithm.

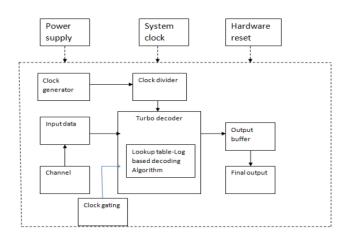

## 3. PROPOSED CLOCK GATING TURBO DECODER ARCHITECTURE

In the proposed system the lookup table log based architecture is designed with Clock gating technique which leads to reduction in power consumption and energy consumption. The circuit is converted into digital hardware

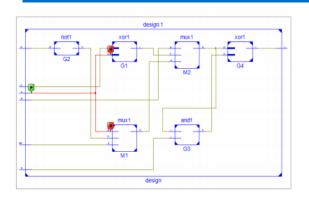

FIG.2: PROPOSED SYSTEM ARCHITECTURE.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

The proposed system consists of a novel architecture suits for the energy-constrained scenarios, which avoids the wastage of energy in the conventional architecture. The min work is to redesign the timing of the conventional architecture in a manner that allows the components to be efficiently merged. This produces an architecture comprising only a low number of lowcomplexity functional units, which are collectively capable of performing the entire algorithm. More wastage is avoided, since the critical paths of the functional units are naturally short and equally lengthened. This eliminates the requirement for additional hardware used for the purpose of managing.

There are two main advantages of inducing LUT based Log algorithm. Firstly, the original algorithm consists of many multiplication operations which lead to very complex circuits while implementing in hardware. algorithm avoids the multiplications by transforming the algorithm into the logarithmic domain, where multiplications become additions. Secondly, it values of soft decisions in the normal domain could have a very large dynamic range and theoretically unlimited, which leads to a large amount of memory space in practice. To transfer them to logarithmic domain reduces the dynamicrange of the soft decisions and consequently all the internal variables in the algorithm. Hence significantly this approach reduces

memory requirement to implement the algorithm. The conventional LUT-Log-BCJR architecture, which employs the slidingwindow technique to generate the LLR sequence, is the concatenation of equal-length sub-sequences. Each of these windows is generated separately, using a forward, a prebackward and a backward recursion. These three different recursions are performed concurrently for three different windows. When the forward recursion is performed for a window, particular one pair of corresponding prioriLLRs processed per clock cycle, in the ascending order of the bit index. The forward recursion of the LUT-Log-BCJR algorithm can be performed in two pipelined steps using the corresponding dedicated hardware components.

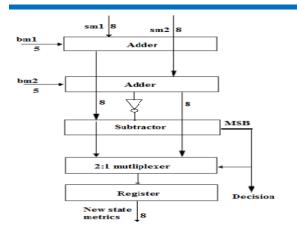

#### 3.1 ACS Unit

The goal of the add-compare-select unit is to add the branch metric for an edge in to its path metric of the present trellis state. This is done in order to create a new path metric for a next state in the next trellis stage. This metric is then compared to the computed path metric from the competitive path to determine the survivor for the next state. The ACS operation must be performed for at most Nmax present state path metrics for each trellis stage.

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

FIG.3: ACS UNIT

The novel low-gate-count ACS unit performs one ACS operation per clock cycle. The control signals to the ACS units are provided by the operational Code, which can be used to perform the functions of the block. Note that the operation codeapproximates the absolute difference between two operands. Its result is said to be equivalent. The second complement operand representation employs the fraction bits this is equivalent to decrementing the binary representation and subtraction. Note that a simpler ACS unit implementation is facilitated by this inaccuracy, which can be trivially canceled out during the calculation. More specifically, a calculation can be performed with the following four operations, which store intermediate results in the registers.

### 4. RESULTS AND DISCUSSIONS

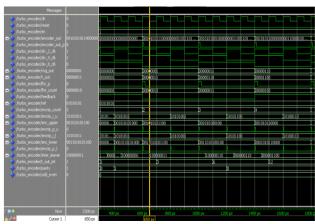

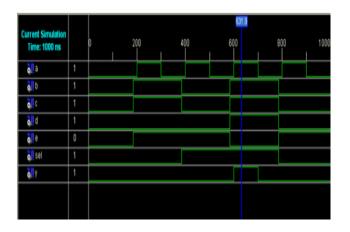

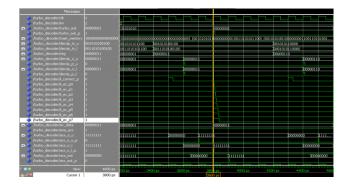

At the encoder side the 8-bit data is been generated with the help of Linear Feedback Shift Register, the obtained output is encrypted and finally sent through the

communication channel. For the purpose of encryption we use a constant 8-bit code to do the process of "AND" with the original bit. In this section the output waveform for 8-bit input data generation, counter and the clock divider circuit is been produced which can be further developed to an encoder of turbo code. The 8-bit input is generated with the help of linear feedback shift register (LFSR), which involves clock, reset and enable as inputs that produces 8-bit random output for the purpose of encryption. The RTL schematic and the output waveform of the LFSR are discussed in figure 7 and 8. In the proposed architecture the clock divider is used to distribute the clock signal to each and every block equally. By implementing this the waiting time of the block for the clock signal can be reduced. This includes clock and reset as input and the clock divided output signal. The RTL schematic (i.e) the internal circuit of the clock divider is discussed in the following figure 9 and figures 10 deals with the output waveform.

FIG.4: OUTPUT WAVEFORM OF TURBO ENCODER.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

FIG.5: RTL SCHEMATIC OF ACS BLOCK.

FIG.6: WAVEFORM OF ACS BLOCK.

FIG.7: WAVEFORM OF THE TURBO-DECODER.

### 5. CONCLUSION

In the present scenario wireless technologies play a vital role. The turbo decoder carries out some major applications such as satellite communication, mobile telephony, internet etc. Realization of turbo decoder algorithm in hardware encounters lots of challenges such as algorithm complexity, large silicon area, high power consumption and low throughput. Taking thesedrawbacks in to account the proposed lookup table log based architecture is designed in such a way that it supports high data rate, high throughput, high speed and reduced number of decoding iterations. This can adopt look-up table log based architecture technique to reduce the hardware complexity by 4% and by using clock-gating technique power consumption is reduced by 38%. This work implementation has the throughput of 1.03 Mb/s and memory requirement of 128 Kbits which makes the decoder fit for the present wireless network applications.

### 5.1 Future work

In synchronous digital circuits the clock net is responsible for significant part of power dissipation Clock gating reduces the unwanted switching on the parts of clock net by disabling the clock. Clock signals is said to be a great source of power dissipation because of high frequency and load. Clock signals do not perform any computation operation but mainly used for synchronization. Hence these signals are not carrying any information. So, by using clock gating one can save power by reducing unused clock activities inside the gated module. A review of some existing techniques available for clock gating is presented. Further more in this technique the data rate can be

Available at https://edupediapublications.org/journals

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

increased so that a better performance can be achieved. Generally turbo codes leads to more hardware complexity some other techniques can be implemented in future so that the complexity can be reduced.

#### REFERENCES

- [1] ChristophStuder, Christian Benkeser ,SandroBelfanti, and Qiuting, "Design and Implementation of a Parallel Turbo-Decoder ASIC for 3GPP-LT", IEEE journal of solid-state circuits 2011.

- [2] T.Wark, R.jurda, "Error Control Coding in Low-Power Wireless Sensor Networks: When is ECC Energy-Efficient" Proc. IEEE, vol98, pp. 1903-1917, Nov 2010.

- [3] C.Schlegel, and K.Iniewski, "Energy Efficiency of the IEEE 802.15.4 Standard in Wireless Sensor Networks: Modeling and Improvement Perspectives" IEEE 802.15.4 standard, 2011.

- [4] E. Boutillon, C. Douillard, and G. Montorsi "Iterative decoding of concatenated convolutional codes: Implementation issues", Proc. IEEE, vol. 95, no. 6, pp. 1201–1227, Jun 2007.

- [5] S.Badrinarayanan, J.M.Mathana and R.RaniHemamaliniKarthik, "Efficient VLSI architecture of SISO based Turbo decoder for wireless applications", International Journal of Advanced Research in Electrical, Electronics

and Instrumentation Engineering. Vol. 3, Issue 2, Feb 2014.

- [6] Dr.J.M.Mathana, S.Gunasekar, S.Jagadish and R.Karthik, "VLSI Architecture of High Performance Turbo Decoder for Wireless Sensor Networks", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. 3, Issue 4, Apr 2014.

- [7] Guohui Wang, HaoShen, YangSun, Joseph R. Cavallaro, Aida Vosoughi, and YuanbinGuo, "Parallel Interleaver Design for a High Throughput HSPA /LTE Multi-Standard Turbo Decoder", IEEE transactions on circuits and systems.vol.61, no.5, May 2014.

- [8] Maurizio Martina, Mario Nicola and Guido Maser, "A Flexible UMTS-WiMax Turbo DecoderArchitecture", IEEE transactions on circuits and systems.vol. 55 n. 4, pp.369-373. ISSN 1549-7747, 2013.

- [9] Z. He, P. Fortier, and S. Roy, "Highly-parallel decoding architectures for convolutional turbo codes", IEEE Trans. Very Large Scale Integr.(VLSI) Syst., vol. 14, no. 10, pp. 1063–8210, Oct 2006.

- [10] Liang Li, Robert G. Maunder, Bashir M. Al-Hashimi and LajosHanzo, "A Low-Complexity Turbo Decoder Architecture for EnergyEfficient Wireless Sensor Networks", IEEE transactions on very large scale

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

p-ISSN: 2348-6848 e-ISSN: 2348-795X Volume 04 Issue 07 June 2017

integration (vlsi) systems, vol. 21, no. 1, Jan 2013.

[11] Anitha.V, Dr.T.Menakadevi, "VLSI Architecture of a Clock-gating Turbo Encoder for Wireless Sensor Network Applications" IJISET - International Journal of Innovative Science, Engineering & Technology, Vol. 2, Issue 12,ISSN 2348 – 7968, Dec 2015.

[12] Hesham El Gamaland A. Roger Hammons, "Analyzing the Turbo Decoder Using the Gaussian Approximation", IEEE transactions on information theory, vol. 47, no. 2, Feb 2001.

[13] I.F.Akyildiz, W.Su,Y. Sankarasubramani, and E. Cayirc, "Wireless sensor networks: A survey", Comput. Netw.: Int. J. Comput.Telecommun. Netw., vol. 52, pp. 292–422, 2008.

[14] Jagdish D. Kenel and Dr.Kishor D. "Iterative Decoding Kulat, Termination Schemes for Turbo Code Performance Optimization In Mobile Wi-Max Environment", International Journal Computer Science Issues, Vol. 10, Issue 4, No 1, ISSN: 1694-0784, July 2013.

M Devi Satya Priya received the B.Tech degree in Electronics and Communications from Kakinada Institute of Engineering and Technology for Women and awarded

M.Tech degree in VLSI from Kakinada Institute of Engineering and Technology. Her areas of interest include VLSI Design, HDI Design and Communication system.

P Priyanka pursuing M.Tech

VLSI SD in Kakinada Institute

of Engineering and

Technology. She received

Bachelor Degree in

Department of Electronics

and Communication Engineering from Sri Sai Aditya Institute of Science and Technology.