e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

## Design And Implementation Of Fault Tolerant Fft's For Reconfigurable Caches Using Parseval Checks

<sup>1</sup>Cheedella.V L N Jagadeesh Kumar & Dr. J. Narendra Babu <sup>1</sup>p.G Scholar, Dept. Of Ece, *Sai Tirumala* Nvr Engineering College, Jonnalagadda, Guntur, A.P, India. <sup>2</sup>professor & H.O.D, Dept. Of Ece, *Sai Tirumala* Nvr Engineering College, Guntur, A.P, India

**ABSTRACT:** A low complexity and error tolerant design has more demand in the signal processing systems. Algorithmic Based Fault Tolerance (ABFT) technique utilizes the algorithmic properties for detecting and correcting the errors. FFTs are the key building blocks in many communication and signal processing systems. Various protection schemes have been proposed to detect and correct the errors in FFT. Parseval or Sum of squares check is one of the protection scheme which is widely used. It is common to find various blocks in parallel. Newly, a technique that utilizes fact to implement Fault Tolerance on parallel filters has been proposed. This technique is first applied for protecting FFT. Hence, two improved protection schemes are proposed and evaluated. These schemes combine the use of double error correction codes and parseval checks. Further, these proposed schemes are reducing the implementation cost of production.

Index terms: Error Correction Codes (ECC), Fast Fourier Transforms (FFTs), Soft Errors.

#### 1. INTRODUCTION

In Communication and Signal processing systems the complexity of the circuits increases. This is made feasible by the scaling of CMOS technology. Scaling means the transistor operates with low voltages and

more sensitive to the errors which are caused by the noise and manufacturing

variations. Soft errors can change the logical value of a circuit node. This creates a temporary error that can affect the operation of a system. Various techniques are used to verify the soft errors. These techniques include the particular manufacturing processes for Integrated Circuits like Silicon On Chip (SOC). Other option is to design basic circuit blocks for minimizing the probability of soft errors. Hence, it is possible to add redundancy for detecting and correcting the errors at the system level.

Another example is to use Triple Modular Redundancy (TMR). This technique triples a block and votes among three outputs for detecting and correcting the errors. So the main issue is that they require a large overhead in terms of circuit implementation. However, another approach is to use algorithmic properties to detect/correct errors. This is frequently mentioned as Algorithmic Based Fault Tolerance (ABFT). It can reduce the overhead required for protecting a circuit.

Signal processing and communication circuits are well accommodating for ABFT because these circuits have regular structures and many algorithmic properties. Various ABFT techniques are proposed for

# R

## **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

protecting the basic blocks. Several works are considered to protect the digital filters. The protection of FFT is also extensively studied. Signal processing systems become more complex and it is to find various filters and FFTs which are operating in parallel. For example, Multiple-Input Multiple-Output (MIMO) communication system. Hence, these parallel filters or FFTs generates an opportunity for implementing the ABFT technique.

#### **II.LITERATURE SURVEY**

A single Error Correction Hamming Code is proposed. The original system contains four FFT modules and three redundant modules are added for detecting and correcting the errors. The inputs to the redundant modules are linear combination of inputs. They are used to check linear combinations of the outputs. In this technique, the overheads are lower than TMR as the number of redundant FFTs is related to the logarithm of the number of original FFTs. Let us take example, for protecting the four FFTs three redundant FFTs are needed and to protect eleven FFTs, four redundant FFTs are needed. Hence, it shows that decreasing the overheads with the number of FFTs.

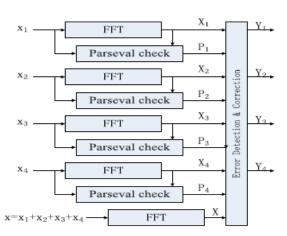

Fig 1.Parity SOS fault tolerant parallel FFTs.

Sum of Squares (SOSs) check is one of the techniques to protect the FFT. This technique is based on the Parseval theorem that states that the SOSs of the inputs to the FFT are equal to the SOSs of the outputs of the FFT excluding a scaling factor. This relationship can be used for detecting the errors with low overhead for each input or output sample.

SOS check can be combined with the ECC for reducing the protection overhead for the parallel FFTs. Hence SOS check only detects the errors and ECC should implement the correction. This can be achieved by using a single parity bit for all FFTs. The combination of a parity FFT and the SOS check can reduces the number of additional FFTs. This scheme will be referred as parity-SOS.

## **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

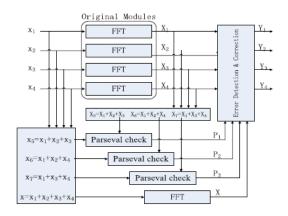

Fig 2. Parity SOS-ECC fault tolerant parallel FFTs.

An additional parity FFT is used for correcting the errors in Parity-SOS scheme. This technique is shown in above fig 2. The main advantage is to reduce the number of SOS checks needed. This scheme is referred as parity-SOS-ECC technique. Hence, final observation is that ECC scheme can detect all the errors which exceed a threshold and SOS can detect most errors. Therefore, fault injection experiments to be done for determining the percentage of errors which are actually corrected.

## **III.PROPOSED SYSTEM**

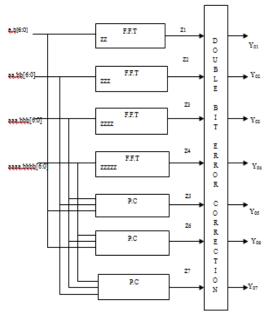

Recently, a new scheme is existed which is based on the Error Correction Codes (ECC). In this technique, each filter can be equivalent of a bit and by using addition parity check bits can be computed. The operation of this technique is the output of the sum of the several inputs is the sum of the individual outputs. So, this is valid for any linear operation.

Fig 3. Parallel FFT protection using ECCs.

It is assumed that there is only a double error on the system at any given point in time. There are three main contributions. They are

- 1) Error Correction Code is assessed to protect the parallel FFTs which show its effectiveness in terms of overhead and protection effectiveness.

- 2) A new technique is proposed based on the use of Parseval or sum of squares (SOSs) checks combined with parity FFT.

- 3) A new technique is proposed on which the ECC is used on the SOS checks instead of the FFTs.

This scheme is evaluated by using FPGA implementations to assess the protection overhead. The protection overhead can be reduced by combining the use of ECCs and parseval checks.

#### IV.RESULTS

## **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

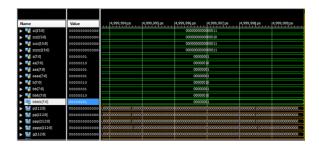

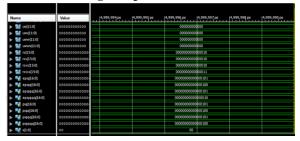

Fig 4. Input waveform

Fig 5. Output waveform V.CONCLUSION

In this paper, the protection of parallel FFTs implementation opposed the soft errors has been studied. Two techniques have been proposed and evaluated. These techniques are based on combining an existing ECC approach with the traditional SOS check. The SOS checks are used for detecting and locating the errors and a simple parity FFT is used for correction. The proposed techniques have been evaluated both in terms of implementation complexity and error detection capabilities. The results show that the second technique, which uses a parity FFT and a set of SOS checks that form an ECC, provides the best results in terms of implementation complexity. In the parity-SOS scheme and the parity-SOS-ECC scheme the fault coverage is 99.9% when the tolerance level for SOS check is 1.

- [1] N. Kanekawa, E. H. Ibe, T. Suga, and Y. Uematsu, Dependability in Electronic Systems: Mitigation of Hardware Failures, Soft Errors, and Electro-Magnetic Disturbances. New York, NY, USA: Springer-Verlag, 2010.

- [2] R. Baumann, "Soft errors in advanced computer systems," IEEE Des. Test Comput., vol. 22, no. 3, pp. 258–266, May/Jun. 2005.

- [3] M. Nicolaidis, "Design for soft error mitigation," IEEE Trans. Device Mater. Rel., vol. 5, no. 3, pp. 405–418, Sep. 2005.

- [4] A. L. N. Reddy and P. Banerjee, "Algorithm-based fault detection for signal processing applications," IEEE Trans. Comput., vol. 39, no. 10, pp. 1304–1308, Oct. 1990.

- [5] T. Hitana and A. K. Deb, "Bridging concurrent and non-concurrent error detection in FIR filters," in Proc. Norchip Conf., Nov. 2004, pp. 75–78.

- [6] S. Pontarelli, G. C. Cardarilli, M. Re, and A. Salsano, "Totally fault tolerant RNS based FIR filters," in Proc. 14th IEEE Int. On-Line Test Symp. (IOLTS), Jul. 2008, pp. 192–194.

- [7] B. Shim and N. R. Shanbhag, "Energy-efficient soft error-tolerant digital signal processing," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 4, pp. 336–348, Apr. 2006.

- [8] Z. Gao, W. Yang, X. Chen, M. Zhao and J. Wang, "Fault missing rate analysis of the arithmetic residue codes based fault-tolerant FIR filter design," in Proc. IEEE IOLTS, 2012, pp. 130–133.

- [9] B. Shim and N. Shanbhag, "Energy-efficient soft error-tolerant digital signal processing," IEEE Trans. Very Large Scale Integr. Syst., vol. 14, no. 4, pp. 336–348, Apr. 2006.

- [10] Y.-H. Huang, "High-efficiency soft-error-tolerant digital signal processing using fine-grain subword-detection processing," IEEE Trans. Very Large Scale Integr. Syst., vol. 18, no 2, pp. 291–304, Feb. 2010.

- [11] P. Reviriego, C. J. Bleakley, and J. A. Maestro, "Structural DMR: A technique for implementation of soft-error-tolerant FIR filters," IEEE Trans. Circuits Syst. II: Exp. Briefs, vol. 58, no. 8, pp. 512–516, Aug. 2011.

### **VI.REFERENCES**