Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

# ANFIS Controller based Voltage Controlled DSTATCOM Using External Inductor

S. K. Sameer<sup>1</sup>, PG Scholar, Department of EEE, SHREE Institute of Technical Education, Gopalapuram, Tirupati, A.P., India

Y. Peraiah<sup>2</sup>, M. Tech (PE), Department of EEE, SHREE Institute of Technical Education, Gopalapuram, Tirupati, A.P., India

ABSTRACT—this project proposes the Design of External Inductor for Improving Performance of DST ATCOM with ANFIS for better Voltage regulation & harmonic reduction. A DST ACOM is used for load voltage regulation and its performance mostly is contingent upon the feeder impedance and its nature (resistive, inductive, stiff, non st iff). On the other hand, a study for investigating voltage regulation performance of DSTATCOM with ANFIS depending upon network parameters is not well defined. This paper aims to provide a comprehensive study of design, operation, and flexible ANFIS control of a DSTATCOM operating in voltage control mode. A detailed analysis of the voltage regulation capability of DSTAT COM under various feeder impedances is presented. Then, a benchmark design procedure to compute the value of external inductor is presented. A dy namic reference load voltage generation scheme is also developed, which allows DST ATCOM to compensate load reactive power during normal operation, in addition to providing voltage support during disturbances. Simulation results validate the effective ness of the proposed ANFIS scheme.

Index Terms—Distribution static compensator (DSTATCOM), power factor, power quality (PQ), voltage control, ANFIS controller.

### I. INTRODUCTION

Large electric drives and utility applications require advanced power electronics converter to meet the high power demands. The evolution of power electronic devices, nonlinear loads, and unbalanced loads has degraded the power quality in the power distribution network. The distribution static compensator is a shunt active filter, which injects currents into the point of common coupling (PCC) (the common point where load, source, and DSTATCOM are connected) such that the harmonic filtering, power factor correction, and load balancing can be achieved. In practice, the presence of feeder impedance and nonlinear loads distorts the terminal voltage (PCC) and source currents. The load compensation using state feedback control of DSTATCOM with shunt filter capacitor gives better results. The switching frequency components in the terminal voltages and source currents are eliminated by using state feedback control of shunt filter capacitor. In this situation, DSTATCOM should operate in CCM. However, due to grid faults, source voltage (stiff or non-stiff) can change at any time and then VCM operation is required. DST AT COM regulates the load voltage by indirectly regulating the voltage across the feeder impedance. When a load is connected to nearly a stiff source, feeder impedance will be negligible. Faults in a widespread power system as well as switching of sizably voluminous loads engender voltage perturbances such as sag and swell in a distribution system. These power quality (PQ) quandaries significantly degrade the performance of sensitive loads like process-control industry, electronics equipment, adjustable drives, etc.

Power quality is one of the most consequential aspects concerned by utility and residential customer, especially when it becomes a very sensitive issue for industrial consumer. Power quality betokens the faculty to receive pristine electrical voltage sinusoidal waveform at distribution point. It is conspicuous that everyone will aim to gain the excellent quality in every situation no matter in which aspect, and power quality should not be omitted. Power quality quandaries are not incipient issues in a electrical power system and every electrical utilizer might want to minimize their effect on electrical equipment so that the highest possible power quality could be obtained by all of the users.

The transmutations of the voltage supplied even for very short period of time, which were not authentically mostly taken attention by public, is now very sumptuous due to their cause of infelicitous operation and shut down situation in manufacturing plants. For the purport of getting the highest efficiency in engenderment besides for sustaining of the most plausible operating cost, electrical customers were now agog for the high power quality. For instance, perturbances like voltage sag, which was introduced by the higher fault on the network, will influence more number of customer victims. Ergo, an opportune study and tenaciousness about the puissance quality perturbances should be conducted solemnly as well as the extenuation manners not only to consummate customers demand, but withal increase the reputation and quality of electrical power in our country.

In order to further understand the sophisticated power quality quandaries, the recordings of all perturbances are now done by installing the on-line power quality monitoring system. Besides that, sundry professional surveys had conducted in date. Hence, it is conspicuously that power quality perturbances are now became the very crucial topic for us to understand and study more. It signifies that the detection and mitigation of voltage sag in electrical power system are withal very paramount to achieve amelioration in power system so that their benefits could be experienced by people in whole country.

From decades to decades, power electronics have been introduced and developed further due to its economical and power preserving advantages. Flexible AC Transmission System (FACTS) are widely used to solve power quality perturbances and Distribution Static Compensator (DSTATCOM) is one of the members of FACTS contrivances family which is efficacious and flexible. Its function is akin to the utilization of synchronous transformer. In other words, DSTATCOM is an expeditious-respond reactive power source compensator, which can opportunely solve varies power perturbances with congruous controller designed, such as voltage sag, voltage swell, flicker, harmonic, and transient. It contains an injection transformer, a voltage source converter (VSC) and a PWM controller with concrete control scheme in order to perform its main function efficient and efficaciously. In this thesis, the function of DST AT COM in voltage mitigation was mainly be discussed and it is one of the most paramount function of D-STATCOM contrivances.

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

Conventionally, static var compensator (SVC) is utilized to regulate load voltage, compensate reactive current, and amend transient stability. However, the SVC causes quandaries like harmonic current injection in the system, harmonic amplification, and possible resonance with the source impedance. Distribution static compensator (DSTATCOM) has been proposed to surmount the inhibitions of SVC [3]–[9]. A DSTATCOM is one of the most efficacious solutions to regulate the load voltage. It provides load voltage regulation by supplying fundamental reactive current into source.

However, most of the conventional DSTAT COMs utilized for voltage regulation consider highly inductive and/or significantly astronomically immense feeder impedance. This is conventionally erroneous in a distribution system where feeder impedance used to be resistive in nature. In this scenario, the DSTAT COM will have diminutive voltage regulation capability. Another consequential is-sue is the generation of reference load voltage. In conventional DSTAT COM application for voltage regulation, reference load voltage is set at 1.0 per unit (p.u.). At this load voltage, voltage-source inverter (VSI) always exchanges reactive power with the source with leading power factor. This causes continuous power losses in the feeder and VSI. Additionally, a conventional DSTATCOM requires high-current rating VSI to provide voltage support. This high-current requisite increases the potency rating of the VSI and engenders more losses in the switches as well as in the feeder.

The voltage regulation performance of DSTATCOM mainly depends upon the feeder impedance and its nature (resistive, inductive, stiff, and nonstiff). For voltage control mode (VCM) operation of DSTATCOM and/or grid-connected inverters, the conception of inserting an external inductor in line has been reported. However, in these schemes, only the concept has been introduced leaving ample scope for further investigation and insight into the design details.

The focus of this paper is to provide a detailed design procedure for culling the external inductor which satiates several practical constraints, sanction DSTATCOM to regulate load voltage in stiff as well as resistive feeder, reduce the current requisite for mitigation of sag, and reduce the system losses. With coordinated control of the load fundamental current, terminal voltage, and voltage across the external inductor, a dynamic reference load voltage generation scheme is presented. This scheme ascertains unity power factor (UPF) operation during mundane operation and maintains load voltage constant during voltage perturbances. Detailed simulation and experimental results are included to verify the DSTATCOM performance.

### II. DSTATCOM IN THE POWER DISTRIBUTION SYSTEM

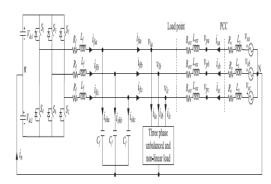

Fig. 1 shows the power circuit diagram of the DST AT COM topology connected in the distribution system.  $L_s$  and  $R_s$  are source inductance and resistance, respectively. An external inductance  $L_{\rm ext}$  is included in series between load and source points. This inductor helps DST AT COM to achieve load voltage regulation capability even in worst grid conditions, i.e., resistive or stiff grid. From IEEE-519 standard, point of commoncoupling (PCC) should be the point which is accessible to both the utility and the customer for direct measurement [20]. Therefore, the PCC is the point where  $L_{\rm ext}$  is connected to the source. The DST AT COM is connected at the point where load and

Lext are connected. The DSTATCOM uses a three-phase four-wire VSI. A passive LC filter is connected in each phase to filter out high-frequency switching components. Voltages across dc capacitors, Vdc1 and Vdc2, are maintained at a reference value of Vdcref.

Fig. 1.Three-phase equivalent circuit of DSTATCOM topology in the distribution system.

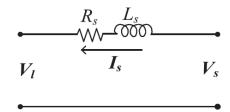

Fig. 2.Equivalent source-load model without considering external inductor.

# III. EFFECT OF FEEDER IMPEDANCE ON VOLTAGE REGULATION

To demonstrate the effect of feeder impedance on voltage regulation performance, an equivalent source-load model without considering external inductor is shown in Fig. 2. The current in the circuit is given

$$I_s = \frac{V_s - V_l}{Z_s} \tag{1}$$

where  $V s = V s \angle \delta$ ,  $V I = V \angle 0$ ,  $I s = I s \angle \phi$ , and  $Z s = Z s \angle \theta s$ , with V s, V I, I s, Z s,  $\delta$ ,  $\phi$ , and  $\theta s$  are rms source voltage, rms load voltage, rms source current, feeder impedance, load angle, power factor angle, and feeder impedance angle, respectively. The three-phase average load power (P h) is expressed as

$$P_l = \text{Real} \left[ 3 \, \boldsymbol{V}_l \boldsymbol{I}_s^{\ *} \right]. \tag{2}$$

Substituting V and Isinto (2), the load active power is

$$P_l = \frac{3V_l^2}{Z_s} \left[ \frac{V_s}{V_l} \cos(\theta_s - \delta) - \cos \theta_s \right].$$

(3)

Rearranging (3), expression for  $\delta$ is computed as follows:

$$\delta = \theta_s - \cos^{-1} \left[ \frac{V_l}{V_s} \left( \cos \theta_s + \frac{P_l Z_s}{3 V_l^2} \right) \right]. \tag{4}$$

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

For power transfer from source to load with stable operation in an inductive feeder,  $\delta$ must be positive and less than 90 °. Also, all the terms of the second part of (4), i.e., inside  $\cos -1$ , are amplitude and will always be positive. Therefore, the value of the second part will be between "0" and " $\pi$ /2" for the entire operation of the load. Consequently, the load angle will lie between  $\theta$ sand ( $\theta$ s –  $\pi$ /2) under any load operation, and therefore, maximum possible load angle is  $\theta$ s. The vector expression for source voltage is given as follows:

$$Vs = VI + IsZs \angle (\theta s + \varphi)$$

(5)

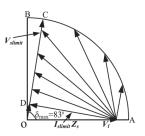

A DSTATCOM regulates the load voltage by injecting fundamental reactive current. To demonstrate the DSTATCOM voltage regulation capability at different supply voltages for different Rs/Xs, vector diagrams using (5) are drawn in Fig. 3. To draw these diagrams, load voltage VIs taken as reference phasor having the nominal value OA(1.0 p.u.). With aim of making V= V= 1.0 p.u., locus of Vswill be a semicircle of radius VI. Since the maximum possible load angle is  $90^\circ$  in an inductive feeder, phasor Vscan be anywhere inside curve OACBO. It can be seen that the value of  $\theta$ s+  $\varphi$ must be greater than  $90^\circ$  for zero voltage regulation. Additionally, it is possible only when power factor is leading at the load terminal as  $\theta$ scannot be more than  $90^\circ$ .

Fig. 3. Voltage regulation performance curve of DSTATCOM at different Rs/Xs. (a) For Rs/Xs=1. (b) For  $Rs/Xs=\sqrt{3}$ . (c) For Rs/Xs=3.73

Fig. 3(a) shows the limiting case when Rs/Xs=1, i.e.,  $\theta s=45 \circ$ . From (4), the maximum possible load angle is  $45 \circ$ . The maximum value of angle,  $\theta s+\varphi$ , can be  $135 \circ$  when  $\varphi$  is  $90 \circ$ . Hence, the limiting source current phasor OE, which is denoted by Islimit, will lead the load voltage by  $90 \circ$ . Lines OC and AB show the limiting vectors of Vs and IsZs, respectively, with Das the intersection point. Hence, area under ACDA shows the operating region of DSTATCOM for voltage regulation. The point D has a limiting value of Vs limit  $SS = 10.00 \circ 10.00 \circ$

Fig. 3(b) considers case when  $Rs/Xs=\sqrt{3}$ , i.e.,  $\theta s=30$ °. The area under ACDA shrinks, which shows that with the increase in Rs/Xs from the limiting value, the voltage regulation capability decreases. In this case, the limiting values of Vs limit and IsZs are found to be 0.866 and 0.5 p.u., respectively. Here, maximum possible voltage regulation is 13.4%. However, due to high-current requirement; a practical DST AT COM can provide very small voltage regulation.

Voltage regulation performance curves for more resistive grid, i.e.,  $\theta s=15$ °, as shown in Fig. 3(c), can be drawn similarly. Here, area under *ACDA* is negligible. For this case, hardly any voltage regulation is possible. Therefore, more the feeder is resistive in nature,

lesser will be the voltage regulation capability. Therefore, it is inferred that the voltage regulation capability of DST ATCOM in a distribution system mainly depends upon the feeder impedance. Due to resistive nature of feeder in a distribution system, DST ATCOM voltage regulation capability is limited. Moreover, very high current is required to mitigate small voltage disturbances, which results in higher rating of insulated-gate bipolar transistor switches as well as increased losses. One more point worth to be noted is that, in the resistive feeder, there will be some voltage drop in the line at nominal source voltage which the DST ATCOM may not be able compensate to maintain load voltage at 1.0 p.u. even with an ideal VSI.

# IV. SELECTION OF EXTERNAL INDUCTOR FOR VOLTAGE REGULATION IMPROVEMENT AND RATING REDUCTION

This section presents a generalized procedure to select external inductor for improvement in DSTATCOM voltage regulation capability while reducing the current rating of VSI. Fig. 4 shows single-phase equivalent DSTATCOM circuit diagram in distribution system. With balanced voltages, source current will be

$$I_{s} = \frac{V_{s} \angle \delta - V_{l} \angle 0}{\left(R_{s} + R_{\text{ext}}\right) + j\left(X_{s} + X_{\text{ext}}\right)} = \frac{V_{s} \angle \delta - V_{l} \angle 0}{R_{\text{sef}} + jX_{\text{sef}}} \tag{6}$$

where Rsef = Rs+ Rext and Xsef = Xs+ Xext are effective feeder resistance and reactance, respectively. Rext is equivalent series resistance (ESR) of external inductor, and will be small. With  $\theta$ sef =  $\tan -1 X$ sef Rsef and Rsef = R2 sef + R3 sef as effective impedance angle and effective feeder impedance, respectively, the imaginary component of Rsis given as

$$I_s^{im} = \frac{V_l \sin \theta_{\text{sef}} + V_s \sin \left(\delta - \theta_{\text{sef}}\right)}{Z_{\text{sef}}}.$$

(7)

With the addition of external impedance, the effective feeder impedance becomes predominantly inductive. Hence, Zsef $\approx X$ sef. Therefore, approximated  $Iim\ s$  will be

$$I_s^{im} = \frac{V_l \sin \theta_{\text{sef}} + V_s \sin \left(\delta - \theta_{\text{sef}}\right)}{X_{\text{sef}}}.$$

(8)

DSTATCOM Power rating (Svsi) is given as follows [21]:

$$S_{\text{vsi}} = \sqrt{3} \, \frac{V_{\text{dc}}}{\sqrt{2}} \, I_{\text{vsi}} \tag{9}$$

Where Ivsi is the rms phase current rating of the VSI and Vdc is the voltage maintained at the dc capacitors. The DSTATCOM aims to inject harmonic and reactive current component of load currents. Suppose Iim I is the maximum rms reactive and harmonic current rating of the load; then, the value of compensator current used for voltage regulation (same as Iims) is obtained by subtracting Iim I from Ivsi and given as follows:

$$I = I_{\text{vsi}} - I_l^{im} = \frac{\sqrt{2}S_{\text{vsi}}}{\sqrt{3}V_{\text{dc}}} - I_l^{im}.$$

(10)

Comparing (8) and (10) while using the value of  $\delta$ from (4), the following expression is obtained:

$$X_{\text{sef}} = \frac{V_l \sin \theta_{\text{sef}} - V_s \sin \left[ \cos^{-1} \left[ \frac{V_l}{V_s} \left( \cos \theta_{\text{sef}} + \frac{P_l X_{\text{sef}}}{3 V_l^2} \right) \right] \right]}{\frac{\sqrt{2} S_{\text{sei}}}{\sqrt{3} V_{\text{de}}} - I_l^{im}}.$$

(11)

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

The above expression is used to compute the value of external inductor. A design example of external inductor, used for this study, is given in the next section.

### V. DESIGN EXAMPLE OF EXTERNAL INDUCTOR

Here, it is assumed that the considered DSTATCOM protects load from a voltage sag of 60%. Hence, source voltage  $V_s$ =0.6 p.u. is considered as worst case voltage disturbances. During voltage disturbances, the loads should remain operational while improving the DSTATCOM capability to mitigate the sag. Therefore, the load voltage during voltage sag is maintained at 0.9 p.u., which is sufficient for satisfactory operation of the load. In the present case, maximum required value of  $I_i^{im}$  is 10 A. With the system parameters given in Table I, the effective reactance after solving (11) is found to be 2.2  $\Omega$  ( $L_{sef}$  = 7 mH). Hence, value of external inductance,  $L_{ext}$ , will be 6.7 mH.

This external inductor is selected while satisfying the constraints such as maximum load power demand, rating of DSTATCOM, and amount of sag to be mitigated. In this design example, for base voltage and base power rating of  $400 \, \text{V}$  and  $10 \, \text{kVA}$ , respectively, the value of external inductance is  $0.13 \, \text{p.u.}$  Moreover, with a total inductance of 7 mH (external and actual grid inductance), the total impedance will be  $0.137 \, \text{p.u.}$  The short-circuit capacity of the line will be  $1/0.13 = 7.7 \, \text{p.u.}$ , which is sufficient for the satisfactory operation of the system. Additionally, a designer always has flexibility to find suitable value of  $L_{\text{ext}}$  if the constraints are modified or circuit conditions are changed. Moreover, the conventional DSTATCOM operated for achieving voltage regulation uses large feeder inductances [11], [13].

TABLE I SIMULATION PARAMETERS

| System quantities  | Values                                                                           |

|--------------------|----------------------------------------------------------------------------------|

| Source voltage     | 230 V rms L-N (1.0 p.u.), 50 Hz                                                  |

| Feeder impedance   | $R_s = 0.3 \Omega, L_s = 0.3 \mathrm{mH}, R_s/X_s = 3.185$                       |

| External impedance | $L_{\rm ext} = 6.7 \text{ mH}, R_{\rm ext} = 0.07 \Omega$                        |

| Linear load        | $Z_{la} = 30 + j62.8 \Omega, Z_{lb} = 40 + j78.5 \Omega,$                        |

|                    | $Z_{lc} = 50 + j50.24 \Omega$                                                    |

| Nonlinear load     | Three-phase rectifier supplying RL load of 50 $\Omega$                           |

|                    | and 200 mH                                                                       |

| VSI parameters     | $V_{\rm dc} = 520 \text{ V}, C_{\rm dc} = 2600 \mu\text{F}, L_f = 5 \text{ mH},$ |

|                    | $C_f = 20 \mu\text{F}, S_{\text{vsi}} = 30 \text{kVA}$                           |

| PI gains           | $K_{p\delta} = 8.5  e^{-7}, K_{i\delta} = 1.8  e^{-6}$                           |

With the external inductance while neglecting its ESR,  $R_s$  / $X_{sef}$  will be 0.13, i.e.,  $Q_{sef}$ = 83°. Voltage regulation performance curves of the DSTATCOM in this case are shown in Fig. 5, of the stable operating range OABO. Hence, introduction of external inductor greatly improves the DSTATCOM voltage regulation capability. Additionally, due to increased effective feeder impedance, the current requirement for sag mitigation also reduces. Moreover, if ESR of the external inductor is included, then the equivalent feeder impedance angle changes slightly (i.e., from 83 ° to 80.45 °) and has negligible effect on the expression obtained in (11) as well as the voltage regulation capability of the DSTATCOM.

$Fig.\,4. Voltage\,regulation\,per formance\,of\,DSTATCOM\,\,with\,external\,inductance.$

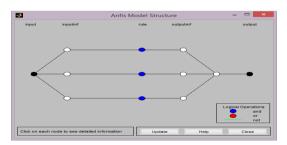

# VI. DESIGN OF ADAPTIVE NEURO-FUZZY CONTROLLER

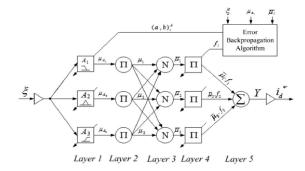

Adaptive neuro fuzzy inference system (ANFIS) integrates the best features of fuzzy systems and neural networks, and it has potential to capture the benefits of both in a single frame work. ANFIS is a kind of artificial neural network that is based on Takagi-sugeno fuzzy inference system, which is having one input an done output. Using a given data set, the toolbox function of ANFIS constructs a fuzzy inference system (FIS) where as the membership function parameters are tuned (adjusted) using a back propagation algorithm. In order to have an idea of optimized ANFIS architecture for proposed control, an initial data is generated from normal *PI* regulator and the data is saved in workspace of MATLAB. Then the ANFIS command window is opened by typing anfis editor in the main MATLAB window. Then the data previously saved in workspace is loaded in the ANFIS command window to generate an optimized ANFIS architecture as shown in Fig.3.

Figure. 4(a) Optimized ANFIS architecture suggested by MATLAB/anfiseditor.

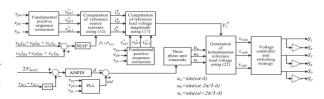

In Fig.4 shows schematic of the proposed ANFIS based control architecture. The node functions of each layer in the ANFIS architecture are described as follows:

Figure. 5 Schematic of the proposed ANFIS-based control architecture.

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

The error between reference dc-link voltage and actual dc-link voltage ( $\xi$ =V<sub>dc</sub>\*-V<sub>dc</sub>) is given to the neuro-fuzzy controller and the same error is used to tune the precondition and consequent parameters [10]. The control of dc-link voltage gives the active power current component (i<sub>d</sub>\*'), which is further modified to take in account of active current component injected from RES(i<sub>Ren</sub>). The node functions of each layer in ANFIS architecture are as described below:

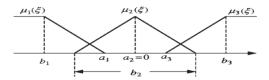

Layer 1: This layer is also known as fuzzification layer where each node is represented by square. Here, three membership functions are assigned to each input. The trapezoidal and triangular membership functions are used to reduce the computation burden as shown in Fig. 5. And the corresponding node equations are as given below:

$$\mu_{A1}(\varepsilon) = \frac{1}{\frac{\varepsilon - a_1}{b_1 - a_1}} \frac{\varepsilon \le b_1}{b_1 < \varepsilon < a_1}$$

$$0 \quad \varepsilon \ge a_1$$

$$\mu_{A2}(\varepsilon) = \frac{1 - \frac{\varepsilon - a_1}{0.5 b_2}}{0} \frac{|\varepsilon - a_2| \le 0.5 b_2}{|\varepsilon - a_2| \ge 0.5 b_2}$$

$$\mu_{A3}(\varepsilon) = \frac{\varepsilon - a_1}{b_1 - a_1} \frac{a_3 < \varepsilon < b_3}{1}$$

$$1 \quad \varepsilon \ge b_3$$

$$(12)$$

where the value of parameters  $(a_i, b_i)$  changes with the change in error and accordingly generates the linguistic value of each membership function. Parameters in this layer are referred as premise parameters or precondition parameters.

Figure. (6a) Fuzzy membership functions.

Layer 2: Every node in this layer is a circle labelled as  $\Pi$ . which multiplies the incoming signals and forwards it to next layer

$\mu_i = \mu_{Ai}(\varepsilon_1).\mu_{Bi}(\varepsilon_2)...$  ... i=1,2,3,... But in our case there is only one input, so this layer can be ignored and the output of first layer will directly pass to the third layer. Here, the output of each node represents the firing strength of a rule.

Layer 3: Every node in this layer is represented as circle. This layer calculates the normalized firing strength of each rule as given below:

$$\overline{\mu_l} = \frac{\mu_l}{\mu_1 + \mu_2 + \mu_2} \tag{13}$$

Layer 4: Every node in this layer is a node function

$$O_i = \overline{\mu}_i$$

$f_i = \overline{\mu}_i \left( a_0^i + a_1^i \varepsilon \right)$  i=1,2,3.

where the parameters  $(a_0^i, a_1^i)$  are tuned as the function of input  $(\xi)$ . The parameters in this layer are also referred as consequent parameters.

Layer 5: This layer is also called output layer which computes the output as given below. The output from this layer is multiplied with the normalizing factor to obtain the active power current component.

Fig. 6. Block diagram of the proposed flexible control strategy.

$$P_{\text{loss}} = \frac{1}{T} \int_{t_1 - T}^{t_1} \left( v_{la} i_{fta} + v_{lb} i_{ftb} + v_{lc} i_{ftc} \right) dt. \tag{14}$$

The reference source currents must be in phase with the respective fundamental positive-sequence PCC voltages for achieving UPF at the PCC. Instantaneous PCC voltage and reference source current in phase-*a* can be defined as follows:

$$v_{pa1}^{+} = \sqrt{2} V_{pa1}^{+} \sin(\omega t - \varphi_{pa1}^{+}), \ i_{sa}^{*} = \sqrt{2} I_{sa}^{*} \sin(\omega t - \varphi_{pa1}^{+})$$

(15)

where V+pa1 and  $\phi+pa1$  are rms voltage and angle of fundamental positive-sequence voltage in phase-a, respectively.  $I_{sa}$  is the rms reference source current obtained from (12). With external impedance, the expected load voltage is given as follows:

$$V_{la} = V_{pa1}^{+} - I_{sa}^{*} Z_{\text{ext}}.$$

(16)

From (15) and (16), the load voltage magnitude will be

$$V_{la} = \sqrt{\left[ \left( V_{pa1}^{+} \cos \varphi_{pa1}^{+} - I_{sa}^{*} Z_{\text{ext}} \cos \left( \theta_{ext} - \varphi_{pa1}^{+} \right) \right)^{2} + \left( V_{pa1}^{+} \sin \varphi_{pa1}^{+} - I_{sa}^{*} Z_{\text{ext}} \sin \left( \theta_{ext} - \varphi_{pa1}^{+} \right) \right)^{2} \right]}. (17)$$

With UPF at the PCC, the voltage across the external inductor will lead the PCC voltage by  $90^{\circ}$ . Neglecting ESR of external inductor, it can be observed that the voltage across external inductor improves the load voltage compared to the PCC voltage.

This highlights another advantage of external inductor where it helps in improving the load voltage. As long as Vla lies between 0.9 and 1.1 p.u., same voltage is used as reference terminal voltage (V\*I), i.e.,

if

$$V_{la} \in [0.9 - 1.1 \text{ p.u.}]$$

, then  $V_l^* = V_{la}$ . (18)

2) Operation During Sag: Voltage sag is considered when value of (18) is less than 0.9 p.u. To keep filter current minimum, the reference voltage is set to 0.9 p.u. Therefore,

$$V_l^* = 0.9 \text{ p.u.}$$

(19)

3) Operation During Swell: A voltage swell is considered when any of the PCC phase voltage exceeds 1.1 p.u. In this case, reference load voltage (V\*I) is set to 1.1 p.u., which results in minimum current injection. Therefore,

$$V_l^* = 1.1 \text{ p.u.}$$

(20)

B. Computation of Load Angle ( $\delta$ )

Available online: https://edupediapublications.org/journals/index.php/IJR/

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

Average real power at the PCC (Ppcc) is sum of average load power (PI) and VSI losses (Ploss). The real power Ppcc is taken from the source depending upon the angle between source and load voltages, i.e., load angle  $\delta$ . If DST AT COM dc bus capacitor voltage is regulated to a reference value, then in steady-state condition, Ploss is a constant value and forms a fraction of Ppcc. Consequently,  $\delta$ is also a constant value.

The dc-link voltage is regulated by generating a suitable value of  $\delta$ . The average voltage across dc capacitors (Vdc1 + Vdc2) is compared with a reference voltage and error is passed through a PI controller. Output of PI controller,  $\delta$ , is given as

$$\delta = K_{p\delta} e_{\text{vdc}} + K_{i\delta} \int e_{\text{vdc}} dt$$

(21)

Where vdc = 2 Vdcref –( Vdc1 + Vdc2 ) is the voltage error.  $Kp\delta$  and  $Ki\delta$  are proportional and integral gains, respectively.

### C. Generation of Instantaneous Reference Voltage

Selecting suitable reference load voltage magnitude and computing load angle  $\delta$ from (21), the three-phase balanced sinusoidal reference load voltages are given as follows:

$$v_{refa} = \sqrt{2} V_l^* \sin(\omega t - \delta)$$

$$v_{refb} = \sqrt{2} V_l^* \sin(\omega t - 2\pi/3 - \delta)$$

$$v_{refc} = \sqrt{2} V_l^* \sin(\omega t + 2\pi/3 - \delta).$$

(22)

These voltages are realized by the VSI using a predictive voltage controller [23].

### VII. MATLAB/SIMULINK RESULTS

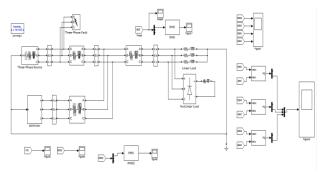

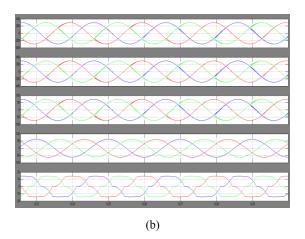

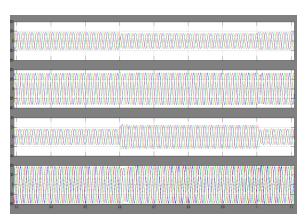

The control scheme is implemented using PSCAD software. Simulation parameters are given in Table I. fig 7(a) show the MATLAB/SIMULINK Model of the Proposed ANFIS based DSTATCOM. Fig. 7(b) shows the Terminal voltages and source currents before compensation are plotted. Distorted and unbalanced source currents flowing through the feeder make terminal voltages unbalanced and distorted. Three conditions, namely, nominal operation, operation during sag, and operation during load change are compared between the traditional and proposed method. In the traditional method, the reference voltage is 1.0 p.u. whereas in the proposed method used to find the reference voltage.

Fig 7(a)

Fig. 7(a) Simulink model of the proposed ANFIS based DSTATCOM (b) PCC voltages, Load Voltages, Source currents & Filter Currents Load Currents using the traditional method.

### A. Nominal Operation

Initially, the traditional method is considered. Fig. 7(b),(a)–(c) shows the regulated terminal voltages and corresponding source currents in phases. These waveforms are balanced and sinusoidal. However, source currents lead respective terminal voltages which show that the compensator supplies reactive current to the source to overcome feeder drop, in addition to supplying load reactive and harmonic currents. Fig. 9

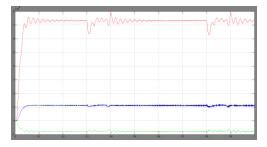

Fig 8 Reactive power of the Load , PCC & DSATCOM

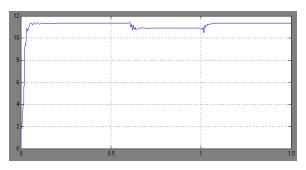

Fig. 9. (a) Voltage at the dc bus.

shows the dc bus voltage regulated at a nominal voltage of 1300 V. Fig. 9 shows the load angle settled around 8.50. Using the proposed method, terminal voltages and source currents in phases, , and are shown in Fig. 10(a)–(c), respectively. It can be seen that the respective terminal voltages and source currents are in phase with each other, in addition to being balanced and sinusoidal. Therefore, UPF is achieved

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

at the load terminal. For the considered system, waveforms of load reactive power (Ql), compensator reactive power (Qc), and reactive power at the PCC (Qpcc) in the traditional and proposed

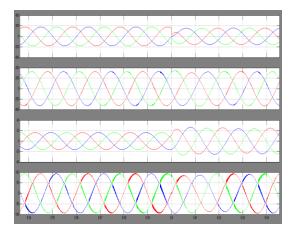

Fig. 10. Terminal voltages and source currents using the proposed method.

In the traditional method, the compensator needs to overcome voltage drop across the feeder by supplying reactive power into the source. As shown in Fig.8, reactive power that is supplied by the compensator and has a value of 4.7 kVAr is significantly more than the load reactive power demand of 2.8 kVAr. This additional reactive power of 1.9 kVAr goes into the source.

This confirms that significant reactive current flows along the feeder in the traditional method. However, in the proposed method, UPF is achieved at the PCC by maintaining suitable voltage magnitude. Thus, the reactive power supplied by the compensator is the same as that of the load reactive power demand. Consequently, reactive power exchanged by the source at the PCC is zero. Fig. 11 shows the source rms currents in phase for the traditional and proposed methods, respectively. The source current has decreased from 11.35 to 10.5 A in the proposed method. Consequently, it reduces the ohmic losses in the feeder.

Fig. 11. Phase-source rms currents Proposed method.

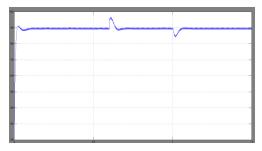

Fig. 11 shows the compensator rms currents in phase- for the traditional and proposed methods, respectively. The current has decreased from 8.4 to 5.2 A in Voltage at the dc bus and Compensator rms current in the proposed method. Fig 12 shows Source voltages, terminal voltages, voltage at dc bus and compensator rms current in proposed method.

Fig12 (a) Source voltages. (b) Terminal voltages. (c) Voltage at the dc bus. (d)

Compensator rms current in the proposed method.

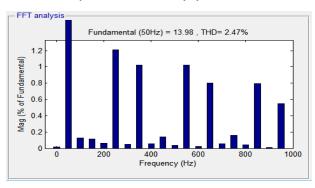

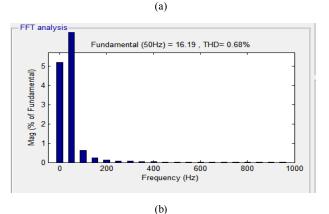

Fig 13 THD values of the Source Currents using (a) Traditional Method (b)Proposed ANFS based DATCTOM

Fig 13. (a), (b) shows THD values of the source currents using a traditional method and proposed method i.e. ANFIS based controller. In traditional method THD values of the source currents showing 2.47%,in proposed method by using ANFIS based controller THD values of the source currents is 0.68%. So by using ANFIS based controller the total harmonic distortion will be reduced and it smoothens the waveforms by reducing harmonics.

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 10 September 2017

#### VIII CONCLUSION

This paper proposes another calculation to create reference voltage for a Distributed static compensator (DSTATCOM) with ANFIS Controller working in voltage control mode. The proposed plan displays a few points of interest contrasted with customary ANFIS controller based DSTATCOM where the reference voltage is subjectively taken as 1.0 p.u. The proposed ANFIS controller guarantees that Unity Power Factor (UPF) is accomplished at the heap terminal along with superficial operation, which is unrealistic in the conventional strategy. Likewise, the compensator infuses lower harmonics and, subsequently, lessens misfortunes in the feeder and voltage-source inverter. Further, a sparing in the rating of DST AT COM is accomplished which expands its ability to moderate voltage list. About UPF is kept up, while managing voltage at the heap terminal, amid burden change. With these elements, this plan permits DST AT COM with ANFIS Controller to handle power quality issues, consonant power, Voltage adjusting, and voltage regulation taking into the heap prerequisite. Reproduction MATLAB/SIMULINK results are introduced to exhibit the adequacy of the proposed ANFIS Controller.

#### REFERENCES

- [1] Chandan Kumar and Marco Liserre Design of External Inductor for Improving Performance of Voltage-Controlled DSTATCOM, Year. 2016, Volume: 63, Issue: 8

- [2] S. Ostroznik, P. Bajec, and P. Zajec, "A study of a hybrid filter," *IEEE Trans. Ind. Electron.*, vol. 57, no. 3, pp. 935–942, Mar. 2010.

- [3] C. Kumar and M. Mishra, "A voltage-controlled DSTAT COM for powerquality improvement," *IEEE Trans. Power Del.*, vol. 29, no. 3, pp. 1499–1507, Jun. 2014.

- [4] Q. Liu, L. Peng, Y. Kang, S. Tang, D. Wu, and Y. Qi, "A novel design and optimization method of an LCL filter for a shunt active power filter," *IEEE Trans. Ind. Electron.*, vol. 61, no. 8, pp. 4000–4010, Aug. 2014.

- [5] T. Aziz, M. Hossain, T. Saha, and N. Mithulananthan, "VAR planning with tuning of STATCOM in a DG integrated industrial system," *IEEE Trans. Power Del.*, vol. 28, no. 2, pp. 875–885, Apr. 2013.

- [6] S. Karanki, N. Geddada, M. K. Mishra, and B. Kumar, "A DST AT COM topology with reduced dc-link voltage rating for load compensation with nonstiff source," *IEEE Trans. Power Electron*, vol. 27, no. 3, pp. 1201–1211, Mar. 2012.

- [7] M. Aredes, J. Hafner, and K. Heumann, "Three-phase four-wire shunt active filter control strategies," *IEEE Trans. Power Electron.*, vol. 12, no. 2, pp. 311–318, Mar. 1997.

- [8] B. Singh, K. Al-Haddad, and A. Chandra, "A new control approach to three-phase active filter for harmonics and reactive power compensation," *IEEE Trans. Power Syst.*, vol. 13, no. 1, pp. 133–138, Feb. 1998.

- [9] S. Narula, B. Singh, and G. Bhuvaneswari, "Improved powerqualitybased welding power supply with overcurrent handling

capability," *IEEE Trans. Power Electron.*, vol. 31, no. 4, pp. 2850–2859, Apr. 2016.

- [10] H. Fujita and H. Akagi, "Voltage-regulation performance of a shunt active filter intended for installation on a power distribution system," *IEEE Trans. Power Electron.*, vol. 22, no. 3, pp. 1046–1053, May 2007.

- [11] R. Gupta, A. Ghosh, and A. Joshi, "Performance comparison of VSC based shunt and series compensators used for load voltage control in distribution systems," *IEEE Trans. Power Del.*, vol. 26, no. 1, pp. 268–278, Jan. 2011.

- [12] M. K. Mishra, A. Ghosh, and A. Joshi, "Operation of a DST AT COM in voltage control mode," *IEEE Trans. Power Del.*, vol. 18, no. 1, pp. 258–264, Jan. 2003.

- [13] A. Jain, K. Joshi, A. Behal, and N. Mohan, "Voltage regulation with ST AT COMs: modeling, control and results," *IEEE Trans. Power Del.*, vol. 21, no. 2, pp. 726–735, Apr. 2006.

- [14] B. Singh and G. Kasal, "Solid state voltage and frequency controller for a standalone wind power generating system," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp. 1170–1177, May 2008.

- [15] B. Singh, S. Murthy, and S. Gupta, "Analysis and design of statcom based voltage regulator for self-excited induction generators," *IEEE Trans. Energy Conver.*, vol. 19, no. 4, pp. 783–790, Dec. 2004.

- [16] L. Asiminoaei, R. Teodorescu, F. Blaabjerg, and U. Borup, "Implementation and test of an online embedded grid impedance estimation technique for PV inverters," *IEEE Trans. Ind. Electron.*, vol. 52, no. 4, pp. 1136–1144, Aug. 2005.

- [17] J. He and Y.W. Li, "Hybrid voltage and current control approach for DGgrid interfacing converters with LCL filters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 1797–1809, May 2013.

- [18] C. Kumar and M. Mishra, "A multifunctional DSTATCOM operating under stiffsource," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3131–3136, Jul. 2014.

- [19] J. Vasquez, R. Mastromauro, J. Guerrero, and M. Liserre, "Voltage support provided by a droop-controlled multifunctional inverter," *IEEE Trans. Ind. Electron.*, vol. 56, no. 11, pp. 4510–4519, Nov. 2009.

- [20] IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems, IEEE Std 519-1992, Apr. 1993, pp. 1–112.

Mr.S.K.Sameer is Completed his B.Tech in Department of EEE in Siddharth institute of engg.,and technology in 2013 and now pursuing his Master of Technology in Power Systems, EEE Department, SHREE Institute Technical Education, Gopalapuram, Tirupati,Andhra Pradesh, India. Interests in Power

Generation, Distribution and Transmission.

Mr.Y.Peraiah is currently working as an Assistant Professorin EEE department in SHREE Institute of Technical Education, Gopalapuram, Tirupati, and Andhra Pradesh, India.