# R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

### Design for Testability of Sleep Convention Logic for memory applications

Humera Zainab<sup>1</sup>, P. Anuradha<sup>2</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, SR Engineering College, Warangal, Telangana, India <sup>2</sup>Department of Electronics and Communication Engineering, SR Engineering College, Warangal, Telangana, India

#### **ABSTRACT:**

Non-volatile memory, NVM storage is a type of computer memory that can retrieve stored information even after having been power off. Flash memory is the type of this memory.here we are using flash memory.these memory is used for floating type transistors. The commodity memory is a high performancememory and embedded memories alone memories these are used for flash which has rapid growth when we go in the integrated chip. The flash memories have been Testedusing Conventional tests they are usually ad hoc. This is the procedure for testing which is expanded for certain designs. There is very much posibility of failure modes in this memories, automatic test equipment (ATE) is a test which is complicated and commonly seen. Production column and row address bit cell as basic design in SRAM. There will may be occurrence of sa0 and sa1 faults in anychip design, these faults will be overcome by using row, column address cells. we are making perfect location to store the data and making no cross sections of SRAMS. Extending of every cell checking for memory array and it gives verification of memory location. The row and column address buffer are used for picking the memory location. By comparing with previous method we used for the above two modules it gives accurate selection for memory location of cell check operation.

#### Keyword:

Design for Testability, Multithreshold Null Convention Logic, Null Convention Logic, Sleep Convention Logic.

#### 1. INTRODUCTION

The important role play of SRAM is increased in applications of soc. The Statius is giving the total area of chip exceeded 50% by SRAM. As Reported by development of 6T-SRAM cells using the standard CMOS processes as (3.87um2 for 0.18um1 and 1.87um2 for 0.13um technology node) and these cells are most suited for using inSOC(system on chip) to the requirement of high-density and performanceand also vastly manufactured.

For making sure that their reliability and robustness and manufacturability, are the normal PCM structures of test are not adequate to monitor high density SRAM process, so that because of specific interactions in between SRAM process and design.normally PCMs are havingmuch generic nature and are kept for supportfor process module of robust development.so that, the structures here are not regularly allow us for testing the power of

choosen design of SRAM rule of environment for specifically Static RAM. This structure is not much suited for providing response of SRAM chips. The layer features of SRAM are very much complex.

DFT is important in this system on chip design and semiconductor industry so that it is essential to reduce testtime, increase the quality of test. and decrease the amount associated with applying and the tests are generated here to the NCL (null convention logic) circuit.No Designfor testability method is developing for the SCL (sleep convention logic) circuits. The current NCL specific DFT techniquescan not be once used for circuitbecause of thestructural changes made by introduction of the sleepmechanism known as power-gating technique. The main purpose of the project is for analyzing the types of faults sa0 and salpresent in the sleep convention logicpipeline introduce a full scan testmethod whichprovides a fully testinganalises at very less ammount that is at cost of the areaoverheard that is get by proposing the scan technique.

### II.DESCRIPTION OF THE TESTING STRUCTURES

The parameters of electrical things are using to prove the good conditions of our Static RAM designs it also Measures the current which is leaked and the arrangement of inter and intra-layer,the measuring of resistance is used for integrity testing connections,theSRAM features to the monitor, and makingnecessarychanges from targets, beta ratio, the evaluation of static noise margin for designing of Static RAM's functional robustness.

The design for testing should be sensitive so that it should check the process of therandom and systamatic occurrences of any weakness of cell memory.this may also used to changing the transistors of SRAM for accuracies, beta ratios and static noise under the SRAM area. Hence, in this test chip of qualification of SRAM, SRAM is testing the structures of SRAM have been designed by us so that for ensuring the SRAM cell in good condition and the SRAM features.

#### International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

Despite of these applications, adoptation ofsleep convention logic in industryis on many factors, developmentofnew NCLlogic style. The purpose of research is to propose comprehensiveDFT method for Sleep Conventional Logic.The DFT method is basing on scan design, this isvery famous in industry, this is providing for full testing. The testingis done for every certain cell in SCL,the efficiencyis proved. Atlast the following contributions are done.

- 1) The sa0 and sa1 in certainSCL pipeline is analized here.

- 2) A scan-based design for testability method isproposed and by considering the faults.

- 3) This method is compatible with thecurrent state and ATPG tools.

- 4) This design for testability is given to a number of Sleep Convention Logic circuits, and the result is shown in high test coverageat the low cost.

#### III. PROPOSED METHOD

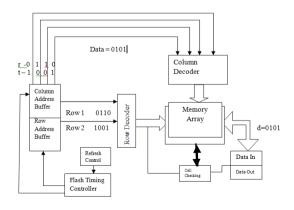

Fig 1 Proposed system

There is no cell checking operation in the existing system so that it may not verify the memory location twice.In this system There is single memory cell array so that to send the data in single

phase. There are the two problems in existing system, to overcome these two problems we are proposing a new architecture in this system.

The proposed system is consisting of refresh control, cell checking, memory array, flash timing controller, column address buffer, row address buffer, column decoder, row decoder, data in or data

The refresh controller and the flash controller will refresh all the data in the memory array location is refreshed. The column address buffer and row address buffer will send the buffer of address and it may be column or row. The address buffer is taken itself by their respective decoder, which means column address buffer is given to the column decoder and the buffer address is decoded.

The output of row and column decoder. This will select the memory location in the memory array. As the changing of row or column address buffer the decoder will be changing the memory location. The total memory location will call it as the memory array.

The cell checking blocks will check either to select the memory location array i.e. S=0 or 1. If S=0 then the memory location array one will be selected, and data is impend in the array memory location. Else S=1 the second array memory location will be selected and then the data impend in second memor location.

The date-in used for writing the data and data-out is used for reading the data memory array. By using this proposed system we are overcoming the checking of the memory array and the array of two memory locations.

#### IV.RESULTS AND DISCUSSIONS

The total output is shown in figure per the address of row and column the data is stored in that respective memory location shown below.

Fig 2 Technology Schematic

We are testing the faults in the chip by giving three inputs namely u,v,x and output is given as c.if the output is same as input then there is no faults in this chip and if the output is changed then there may occur the fault and the chip doesnot work properly.so as shown in the above result there are no faults as the output is same input so there is no faults present in my result.

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

#### V.CONCLUSION

As that here are number of failure modes for memories of flash. algorithms of testing that is (ATE)which is complicated are normally seen here. Production row address bit cell and column address bit cell for any weaknesses of method. There may be occurrence of sa0 and sa1 faults(stuck at faults) in any chip design, these faults are overcome by using row address cell and column address cells we make perfect location for storing the data and there is no cross sections of SRAMS. By extending the cell checking for memory array gives the verification of memory location. The column address buffer and the row address buffer are used to pick the memory location. By comparing with the previous method the above two modules gives the accurate selection of the memory location of the cell checking operation.

#### **VI.REFERENCE**

- [1] Ting-Jung Lin, Wei Zhang, and Niraj K. Jha, "SRAM-BasedNATURE: A Dynamically Reconfigurable FPGA Based on 10T Low-Power SRAMs" IEEE Trans. VLSI Systems, accepted for future inclusionin IEEE journal.

- [2] I. Kuon and J. Rose, "Measuring the gap between FPGAs and ASICs," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 26, no.2, pp. 203–215, Feb. 2007.

- [3] W. Zhang, N. K. Jha, and L. Shang, "A hybrid nano/CMOSdynamically reconfigurable system—Part I: Architecture," *ACM J.Emerg. Technol. Comput. Syst.*, vol. 5, no. 4, pp. 16.1–16.30, Nov. 2009.

- [4] A. DeHon, "Dynamically programmable gate arrays: A step towardincreased computational density," in *Proc. Canadian Wkshp. Field-Program. Devices*, 1996, pp. 47–54.

- [5] H. Noguchi, Y. Iguchi, H. Fujiwara, Y. Morita, K. Nii, H. Kawaguchi, and M. Yoshimoto, "A 10T non-precharge two-port SRAM for 74% power reduction in video processing," in *Proc. IEEE Comput. Soc.Annu. Symp. VLSI*, 2007, pp. 107–112.

- [6] Md. A. Khan, N. Miyamoto, R. Pantonial, K. Kotani, S. Sugawa, and T. Ohmi, "Improving multicontext execution speed on DRFPGAs," in *Proc. IEEE Asian Solid-State Circuits Conf.*, 2006, pp. 275–278.

- [7] S. Trimberger, D. Carberry, A. Johnson, and J. Wong, "A timemultiplexedFPGA," in *Proc. IEEE Symp. FPGAs for Custom Comput.Mach.*, 1997, pp. 22–28.

- [8] T. Fujii, K.-I.Furuta, M. Motomura, M. Nomura, M. Mizuno, K.-I.Anjo, K.Wakabayashi, Y. Hirota, Y.-E.Nakazawa, H. Ito, and M.Yamashina, "A dynamically reconfigurable

- logic engine with amulticontext/multi-mode unified-cell architecture," in *Proc. IEEE Int. Solid-State Circuits Conf.*, 1999, pp. 364–365.

- [9] Sapna Singh, NehaArora, MeenakshiSuthar and Neha Gupta(2012)"Performance Evaluation Of Different Sram Cell Structures AtDifferent Technologies", Proc. of International Journal of VLSI design & Communication Systems (VLSICS) Vol.3.

- [10] W. Zhang, L. Shang, and N. K. Jha, "A hybrid nano/CMOSdynamically reconfigurable system—Part II: Design optimization flow," *ACM J. Emerg. Technol. Comput. Syst.*, vol. 5, no. 3, pp. 13.1–13.31, Aug. 2009.

- [11] G. Lemieux and D. Lewis, "Circuit design of routing switches," in *Proc. Int. Symp. FPGA*, 2002, pp. 19–28.

- [12] Dr.Sanjay Sharma and ShyamAkashe (2011), "High Density Four-Transistor SRAM Cell With Low Power Consumption", *Proc. of Int. J.Comp. Tech. Appl.*, Vol 2, 1275-1282.

## R

#### **International Journal of Research**

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 13 October 2017

#### **BIBLIOGRAPHY OF AUTHORS**

Humera Zainab is pursuing Master of Technology in Electronic Design Technology in SR Engineering College, Warangal, Telangana. She has completed her B.Tech from Trinity Engineering College, Karimnagar, Telangana in 2015. Her areas of interests are VLSI, Digital Signal Processing and Computer Networks. She Published 1 Poster in ICRTEECT-2017.

P. Anuradha working as Senior assistant professor of Electronics and Communication Engineering, S R Engineering College, Warangal. She has 12 years of teaching experience. She has obtained B.Tech (ECE) Degree from National Institute of Science Technology Warangal, Andhra Pradesh, India in 2003 and M.Tech (Embedded systems) Degree from JNTUH, Andhra Pradesh, India in 2010. Pursuing her Ph.D under JNTUH. She is a member of IETE, and her research areas include VLSI, Signal processing, and Embedded Systems.