# R

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 14 November 2017

## Low Latency Mixed Decimation Mdf Architecture for Fft Design

#### M.HARIKA,

M.TECH SCHOLOR

harika.moola@gmail.com

CMR ENGINEERING COLLEGE, RANGAREDDY, T.S, INDIA. C. ASHOK KUMAR, Professor, Head of

the Department, ECE,

cdkumarecehod.cmrec@gmail.com

CMR ENGINEERING COLLEGE RANGAREDDY, T.S, INDIA.

#### **ABSTRACT**

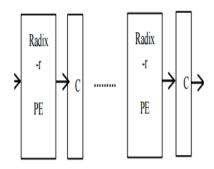

The main objective of this project is to design a mixed-decimation multipath delay feedback (M2 DF) approach for the radix-2^k fast Fourier transform. The appearance of radix- was a milestone in the design of pipelined FFT hardware architectures. Later, radix-2^k was extended to radix-2^k. However, radix-2^k was only proposed for single-path delay feedback (SDF) architectures, but not for feed forward ones, also called multi-path delay commutator (MDC). This paper presents the radix-2^k feed forward (MDC) FFT architectures.

In feed forward architectures radix- can be used for any number of parallel samples which is a power of two. Furthermore, both decimation in frequency (DIF) and decimation in time (DIT) decompositions can be used. In addition to this, the designs can achieve very high throughputs, which make them suitable for the most demanding applications. Indeed, the proposed radix-2^k feed forward architectures require fewer hardware resources than parallel feedback ones, also called multipath delay feedback (MDF), when several samples in parallel must be processed.

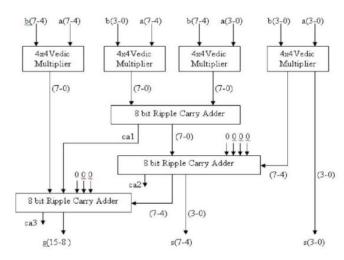

As a result, the proposed radix-2<sup>k</sup> feed forward architectures not only offer an attractive solution for current applications, but also open up a new research line on feed forward structures. Vedic sutra is used as an enhancement for this project. Recursively is a main challenging factor in all arithmetic operations. Multiplier doesn't follow that rule until Vedic sutras comes in to picture. Urdhva Tiryakbhyam in Vedic is a main multiplication algorithm for latency reduction

#### 1. INTRODUCTION

Being an effective algorithmic program for discrete Jean Baptiste Joseph Fourier change (DFT) calculation, quick Fourier change (FFT) has seen more extensive exercise in the field of computerized flag handling. It additionally assumes an expanding

As a matter of fact, the augmentation telephone of correspondence benefit has fortified an emotional ascent of throughput request.

This approach in genuine - fourth measurement business has also rendered the PC equipment plans intended for SISO applications out of date to a specific degree. On this crossroads, multiitinerary postpone commutator (MDC) and multipath defer input (MDF), which fill in as the update of SDC and SDF, individually, are proposed to figure the FFT when a few inspecting of a similar progression are gotten in parallel. In prevalent general, the MDF social framework is made out of different interconnected SDF ways, and every way is in charge of overseeing one of the parallel info streams. This outline adds to the legacy of using register effectively at the payment of misusing the math constituent, especially the butterfly unit of estimation. By coordinate differentiation, the MDC approach make ready for boosting the equipment effectiveness of number juggling units (AUs), while extra stockpiling

Available online: <a href="https://edupediapublications.org/journals/index.php/IJR/">https://edupediapublications.org/journals/index.php/IJR/</a>

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 14 November 2017

must be devoured for either reordering the examples or collapsing the streams, which moreover prompts a pickup of processing delay. very-Large-scale reconciliation (VLSI) is the way toward making an incorporated circle (United States Intelligence Community) by joining a great many transistors into a solitary chip. VLSI started in the seventies when complex semiconductor and correspondence advances were being produced.

The chip is a VLSI gadget. Prior to the presentation of VLSI designing science most Intelligence Community had a constrained band of capacities they could perform. An electronic visit may comprise of a C.P.U., Read-just memory, Random-get to memory and other paste rationale. VLSI lets IC architects ADHD these into one

A die of VLSI integrated circuit

The History of the transistor day of the month to the mid-twenties when a few designers endeavored trick s that were proposed to control current in robustness state - state semiconductor diode and change over them into triodes. Succeeder came after World Warfare II, when the utilization of silicon and germanium quartz glass as microwave radar identifiers lede to upgrades in creation and hypothesis.

Multipath delay input (MDF) which fill in as the ascent of SDC and SDF, individually, are proposed to as.

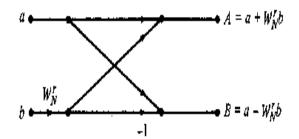

FFT when a few examining of a similar grouping are gotten in line of scope . In predominant general , the MDF structure is made out of different interconnected SDF way, and every way is in charge of overseeing one of the parallel info conduit. This plan adds to the legacy of using registers effectively to the detriment of misusing the math segments, especially the butterfly unit of estimation . By differentiate, the MDC get to prepares for boosting the PC equipment productivity of number juggling units (AU), while extra stockpiling must be devoured for either reordering the examples or collapsing the streams, which furthermore leadin to an expansion of registering delay. Regardless of whether bolster forward complex body part spoke to by the MDC approach or input social association,, for example, the SDF and the MDF outline, they bear the cost of possible answers for strike a harmony between the white torment of equipment assets and the reachable completing Butterfly unit is really a melded duplicate include/sub (FMA) over complex operands. Regular fig tree . portrays a DIT butterfly unit which comprises of a perplexing multiplier, a mind boggling Vipera berus and a complex subtractor.

Basic butterfly Architecture.

#### 2. LITERATURE SURVEY

The models of FFT in view of vector deterioration technique and radix II I algorithmic manage were proposed by He et al (1998). The calculation was misused for the execution of predominant components to venture down the tally of manipulations and the twenty-one stockpiling limit. The capacity limit had been improved by altering the word remove in a dynamic individual way. The proficiency of the planning concerning field and financier was enhanced by utilizing a multiplier in view of disseminated number juggling.

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 14 November 2017

The determinations of the plan were acquired by utilizing a 10II 4 point FFT focal processor. Birdcall Nine Tang et al (2012) Proposed a FFT processor for different character of remote systems, for example, remote LAN, remote MAN and so on. By embracing the Flexible Radix Configured extent n Multiple Delay Feedback (FR CMDF) commutator, an elite could be gotten by FFTs of variable length in an effective way. So as to enhance the proficiency regarding zone and power, an upgraded strategy for duplication was likewise proposed. In add-on, the design could give a help to scaling the huge agent over the style of FFT. The poker chip had been acknowledged with a size of group of three .2 mm 2, a flag to clamor proportion of 40 dB, control pneumonic tuberculosis of five 07mW at 300MHz. This FFT processor of length 512 point could give higher execution and lower billet utilization of energy when contrasted with different outlines. Taesang Cho (2013) introduced a radix 2 5 quick Fourier change ( FFT ) processor of length 512 point f or utilizations of individual range remote systems An altered variant of base two 5 Camellia State calculation of FFT was utilized to drop-off the phase of equipment required . This system could diminish the count of controls and the limit of store required. An intricate multiplier was utilized in the place of a Booth multiplier. The design acquired a SNR estimation of 35 dB with a news length of 'XII' bits at 1.deuce V. This plan had been actualized utilizing XCnanometer innovation with determinations rationale entryway tally was 2, 90, 000, the rate of Throughput was 2.5 Gigabits for every second at 310 Megahertz. Kyung HeoEt al (2003) proposed a FFT CPU utilizing blended base algorithmic administer and another set up strategy. This processor utilized just two quantities of N word recollections for execution of FFT when contrasted with existing FFT centralized computer which utilize four n umbers of N word

recollections. Facilitate this design acquired the ideal prerequisites with regard to zone and flag handling. The quantity of clock beat and number of entryway s were 640 and 37, 000 individually for a FFT processor of length 512 point.

#### 3. COMPARISION AND EVALUATION

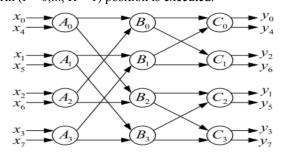

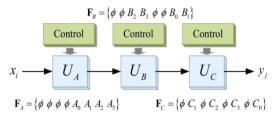

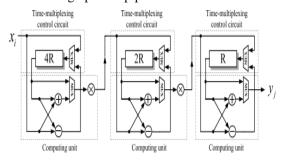

The collapsing transdescription gives a methodical strategy to outlining authority circuit for equipment where a few algorithmic programming forms are clock time multiplexed on a solidarity processing contrivance. Consider an eight-point base - 2k DIF figuring, the calculation can be introduced utilizing an information catamenia chart appeared in FIG., where the hubs speak to calculations and the coordinated edges speak to information way . As appeared, the period diagram comprises of three point s and four numerical process are executed inside each stage. Whenever xi, I = 0,..., septet touches base in serial, different numerical operation in each stage can be time multiplexed to a solitary processing entire with no crash, and the ascendance circuits are resolved methodically by collapsing change. Along these lines, the FFT stream diagram in Figure can be changed into a pipelined frame appeared in Fig., where 11 faculties of operation A0,..., A3, B0,..., B3, and C0,...,C3 are performed in the processing unit UA, UB, and UC, separately. The different operations incorporated into a processing module are masterminded by collapsing hardening. A collapsing parcel is a requested part of operations executed by a similar processing unit. Aside from the operations related with the hubs in the information stream diagram, for the most part, there are additionally nothing operations in the collapsing set. The consider of operations collapsed along with a collapsing set is known as the collapsing operator

## R

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 14 November 2017

(indicated by R in resulting talk). Correspondingly, the figuring unit works in wavering with a stream pickings up R time parcels, and the operation in the rth (r = 0,..., R - 1) position is executed.

Data flowgraphofan8-point DIF DFT algorithm

#### Data flow graph in a pipelined version

#### Optimized hardware scheme diagram

Amid the rth time divider . For instance, consider a protein collapsing curing  $F=\{\phi\ A0\ \phi\ A1\ \phi\ A2$   $\phi\ A3\}$  with R=eight, the registering unit works A0, A1, A2, and A3 in the principal, third, fifth, and seventh time allotments, individually, while keeping inactive in outstanding time interim .

General structure of a pipelined FFT architecture.

In this pro information current experiences multiplier in each stage. The commutator utilized for SDF is fairly extraordinary in light of the fact that it likewise encourages information in reverse. The hold up unit of estimation s are all the more proficiently used by share-out a similar reposting amongst nformation and outturn of butterfly stroke unit. Multiplier and orfly units can be used half since they are avoided one-a large portion of the clock time

Single Path Delay Feedback

Structure

Block Diagram of 8x8 bit Vedic Multiplier

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 14 November 2017

| Hardware Scheme                             | Arithmetic components consumption $(n = log_2 N)$ |                           |           |          | Memory consumption |          | Performance |                |

|---------------------------------------------|---------------------------------------------------|---------------------------|-----------|----------|--------------------|----------|-------------|----------------|

|                                             | Complex Multipliers                               |                           |           | Complex  | Data               | Streams  | Latency     | Throughput     |

|                                             | General                                           | Constant                  | Overall†  | Adders   | Reordering         | Folding  | (Clk.)      | (Samp. / Clk.) |

|                                             |                                                   | 2-PARA                    | LLEL ARCH | TECTURE  | S                  |          |             |                |

| R2MDC, [11]                                 | n - 2                                             | 0                         | n – 2     | 2n       | 5N/8 - 3           | 3N/2 - 2 | 11N/8 - 4   | 2              |

| R22MDC, [12]                                | 2 [n/2] - 2                                       | 0                         | n-2       | 2n       | 2N                 | N-2      | 3N/2 - 1    | 2              |

| R2 <sup>2</sup> MDF, [17]                   | $2\lceil (n-1)/2 \rceil - 1$                      | 0                         | n - 2     | 4n       | N                  | N-2      | N - 1       | 2              |

| R24MDF, [14]                                | 2 [n/4] - 2                                       | 2[n/4]                    | n-2       | 4n       | N                  | N-2      | N-1         | 2              |

| R2M <sup>2</sup> DF, proposed               | n – 2                                             | 0                         | n-2       | 2n       | N+2                | N-2      | N           | 2              |

| R2 <sup>2</sup> M <sup>2</sup> DF, proposed | $2\lceil (n-1)/2 \rceil - 1$                      | 0                         | n-2       | 2n       | N+2                | N-2      | N           | 2              |

| R23M2DF, proposed                           | $2\lceil (n-1)/3 \rceil - 1$                      | $\lfloor (n-1)/3 \rfloor$ | n-2       | 2n       | N+2                | N-2      | N           | 2              |

| R2 <sup>4</sup> M <sup>2</sup> DF, proposed | $2\lceil (n-1)/4 \rceil - 1$                      | 2[(n-1)/4]                | n-2       | 2n       | N+2                | N-2      | N           | 2              |

|                                             |                                                   | 4-PARA                    | LLEL ARCH | TECTURE  | S                  |          |             |                |

| R2 <sup>2</sup> MDC, [12]                   | 3 [n/2] - 3                                       | 0                         | 3n/2 - 3  | 4n       | 2N                 | N-4      | 3N/4 - 1    | 4              |

| R4MDC, [13]                                 | 3 [n/2] - 3                                       | 0                         | 3n/2 - 3  | 4n       | N                  | 8N/3 - 4 | 7N/12 - 1   | 4              |

| R24MDF, [16]                                | $4 \lceil n/4 \rceil - 4$                         | 4 [n/4]                   | 2n - 4    | 8n       | N                  | N-4      | N/2 - 1     | 4              |

| R24MDF, [15]                                | $4 \lceil n/4 \rceil - 4$                         | 4 [n/4]                   | 2n - 4    | 8n       | N                  | N-4      | N/2 - 1     | 4              |

| R2M2DF, proposed                            | 2n - 5                                            | 0                         | 2n - 5    | 4n       | N+4                | N-4      | N/2         | 4              |

| R2 <sup>2</sup> M <sup>2</sup> DF, proposed | $4\lceil (n-2)/2 \rceil - 1$                      | 0                         | 2n - 5    | 4n       | N+4                | N-4      | N/2         | 4              |

| R23M2DF, proposed                           | $4 \lceil (n-2)/3 \rceil - 1$                     | 2[(n-2)/3]                | 2n - 5    | 4n       | N+4                | N-4      | N/2         | 4              |

| R2 <sup>4</sup> M <sup>2</sup> DF, proposed | $4\lceil (n-2)/4 \rceil - 1$                      | 4[(n-2)/4]                | 2n - 5    | 4n       | N+4                | N-4      | N/2         | 4              |

|                                             | 50                                                | 8-PARA                    | LLEL ARCH | ITECTURE | S                  |          |             |                |

| R24MDC, [12]                                | 8 [n/4] -8                                        | 6 [n/4]                   | 7n/2 - 8  | 8n       | 2N                 | N-8      | 3N/8 - 1    | 8              |

| R24MDF, [18]                                | $8 \lceil n/4 \rceil - 8$                         | 8 [n/4]                   | 4n-8      | 16n      | N                  | N-8      | N/4 - 1     | 8              |

| R24MDF, [19]                                | $8\lceil (n-3)/4 \rceil - 1$                      | 8[(n-3)/4]+2              | 4n - 11   | 16n      | N                  | N-8      | N/4 - 1     | 8              |

| R25MDF, [21]                                | $8 \lceil n/5 \rceil - 8$                         | 16 [n/5]                  | 24n/5 - 8 | 16n      | N                  | N-8      | N/4 - 1     | 8              |

| R2M <sup>2</sup> DF, proposed               | 4n - 13                                           | 2                         | 4n - 11   | 8n       | N+8                | N - 8    | N/4         | 8              |

| R2 <sup>2</sup> M <sup>2</sup> DF, proposed | $8 \lceil (n-3)/2 \rceil - 1$                     | 2                         | 4n - 11   | 8n       | N+8                | N-8      | N/4         | 8              |

| R2 <sup>3</sup> M <sup>2</sup> DF, proposed | $8 \lceil (n-3)/3 \rceil - 1$                     | 4[(n-3)/3]+2              | 4n - 11   | 8n       | N+8                | N - 8    | N/4         | 8              |

| R2 <sup>4</sup> M <sup>2</sup> DF, proposed | $8 \lceil (n-3)/4 \rceil - 1$                     | 8  (n-3)/4  + 2           | 4n - 11   | 8n       | N+8                | N-8      | N/4         | 8              |

Computation of N-Point FFT

#### 4. PROGRAMING DESCRIPTION

Xilinx, Inc. (NASDAQ: XLNX) is the world's biggest provider of programmable rationale gadget, the innovator of the performance programmable door clothing (FPGA) and the main semiconducting material organization with a tales producing model IN the Xilinx programming program we can do affectation and reasoning .The whole CPU will be actualized utilizing the Xilinx FPGAs so you won 't need to invest energy wiring up that area of the circuit. You will, in any case, need to message the exchanging and noticeable light that are utilized to control the processor, and need to wire the Xilinx part itself to the switches and lights, however this shouldn't be too awful. You will likewise utilize the backplane transport in your lab furnish so that the Triscuit will be based on two loads up: one for the Xilinx chip, and one for the switches and lights. The HDL Editor highlight film gives broad alter and hunt abilities with oral correspondence - particular ethnic minorities steganography of catchphrases, and in addition coordinated on-birthplace linguistic structure

checking to filter VHDL code for misplay . The Language Help include quickness outline section by giving a query lean of run of the mill dialect develop and generally utilized combination modules like tabulator , aggregators, and adders. There are different interpretation of Xilinx for the capacity of combination on different FPGA's. These understanding are produced basing on the application required.

#### **VHDL DESCRIPTION:**

In the inquiry of a standard point and documentation for the Very High Speed Integrated Circuits (VHSIC) educational modules , the United States Department of (Defense)in 1981sponsored a workshop on Ironware Verbal portrayal Languages (Highthickness lipoprotein ) at Forest Trap , MA . In 1983, the DOD set up fundamental for a standard VHSIC Hardware Description Language VHDL, its environment and its product was granted to IBM, TX Instruments and Intermetrics partnerships. VHDL 2.0 was discharged simply after the task was started. The verse was essentially enhanced rectifying the imperfection of the prior inter lingual interpretation; VHDL 6.0 was discharged in 1984. VHDL

1078/1164 formally turned into the IEEE standard Hardware Description Language in 1987.

#### 5. RESULT ANALYSYS

At last, it can be discovered the exploratory idleness vary from the hypothetical esteems appeared in Table I, and the insightfulness comprises of both side of meat: solidarity the down to earth complex multiplier factor require a few clock cycles/second to get the right outcomes, which prompts an ascent of general latencies and 2) some extra registers are inserted in the circuit to abbreviate the basic way s, in this way the radical deferral of FFT CPU includes a further advance up . Regarding the throughputs, both the

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 14 November 2017

WANG et al.: M2DF ARCHITECTURE FOR RADIX-2k Line of scope FFT 77 Correlating the expended piece LUTs introduced in Table II to particular module of the parallel FFT centralized server . proposed plans and the references have comparative execution all through the different designs. This element recommends that the basic way in M2DF is similar with that having a place with MDF or MDC circuits.

M2DF ARCHITECTURE FOR RADIX-2k Line of scope FFT 77 Correlating the expended piece LUTs displayed in Table II to particular module of the parallel FFT centralized computer.

Proposed plans and the references have comparable execution all through the different setups. This component proposes that the basic way in M2DF is practically identical with that having a place with MDF or MDC circuits.

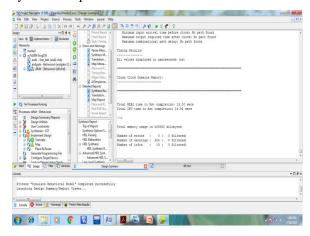

#### Result:

From the above screenshot, the outcome is acquired by giving determination contributions through multiplexer and three twiddle consider inputs a double configuration. After recreation the yield is appeared, yield factors are yy0 to yy7 and y0 to y7 in these two y0 to y7 are DIT yields and yy0 to yy7 are DIF yields add up to we will get 16 yields.

At that point we need to execute the guide on the FPGA to get the mapping subtle elements, so that from the combination report we can get the points of

interest of aggregate undertaking how much time it has taken to get the outcome, CPU time and what number of LUTs are utilized what not. Here we have taken the four piece parallel with the goal that we will get the sixteen blends. Accordingly, the yield factors are sixteen.

#### Synthesis Report:

Amalgamation is done after reproduction. It gives all data about what number of components we are utilized as a part of this undertaking, how much time is taken to peruse every one of the sources of info lastly the time taken for getting result.

Here the time taken for the outcome is 18.92 seconds. Contrasting and the proposed framework time it less. This task is expending less time for getting comes about than past undertaking. In addition the quantity of yields which we are getting specifically time is additionally more that is called throughput.

#### 6. CONCLUSION

This structure current state a profoundly productive strategy for FFT blended devastation utilizing times – "Urdhva Tiryakbhyam Sutra" in view of Vedic science. Disregarding the low memory need and short processing delay, traditional MDF evade experience the ill effects of the wasteful utilization of adders and multipliers in viable applications. This daily paper

## ® Inter

## **International Journal of Research**

Available at <a href="https://edupediapublications.org/journals">https://edupediapublications.org/journals</a>

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue 14 November 2017

prescribes a M2DF structure to ponder this deterrent, which takes out the standby time of math modules in input designs by joining it operations into the DIF-worked processing social unit.

As indicated by the hypothetical investigation and test comes about, the M2DF origination acquires the qualities of criticism anatomical structure s while essentially kerb the overexploitation of number assets. This remarkable component juggling empowers the M2DF structure to be a productive contrasting option to the MDF evade. On the other scaffold player, the M2DF and the MDC plot devour a similar measure of adders, while they have their own benefits in multiplier factor overhead. Notwithstanding, when the software engineering deferral and memory assets are essential quill concerns, the M2DF approach will be more equipment well disposed than the MDC conspire. At long last low basic course delay is accomplished utilizing Vedic sutra.

#### 7.APPLICATIONSANDFUTURESCOPE

A more proficient utilization of the turn assets can be accomplished by persistently enhancing the butterfly component till we are time away with just the essential impact i.e. pith for number juggling and augmentation surgical operation . FFT get together PC code is to be actualized utilizing cycle exact mannikin in LISA. In addition, the endeavor of genuine clasp N point FFT estimation can be taken up as a futurity work. A more mind boggling application particular gathering code utilizing just the directions in the table can be executed and yield can be seen in the processor debugger . In text style of prerequisite of extra guidelines, one can include Operations in the LISA code for depicting usefulness.

#### **8 REFERENCES:**

1.FFT Implementation with Fused Natation - Point Operations by Earl E. Swartzlander Jnr, Lifetime Fellow, IEEE, and Hani H.M. Saleh, Member, IEEE in IEEE Minutes ON Figurer, VOL. 61, NO. 2, Feb 2012.

- 2. Enhanced Computer design for a Floating-Point Fused Dot Intersection Unit of estimation by Jongwook Sohn and Earl E. Swartzlander, Jnr. Bureau of Electrical and Calculator Engineering The University of Texas at Austin, Texas 78712 out of 201III IEEE 21st Symposium on Estimator Arithmetic.

- 3. IEEE Standard for Floating-Point Arithmetic in IEEE Computer Bon ton.

- 4. An Algorithm for the Machine Calculation of Complex Fourier Series by J. W. Cooley and J. W. Tukey.

- 5. Multi-operand Floating-sharpness Addition by Alexander F. Tenca Synopsys, Inc. In 2009 nineteenth IEEE International Symposium on Computer Arithmetic.

- 6. Enhanced Architectures for a Floating-Point Fused Dot Product Unit by Jongwook Sohn and Earl E. Swartzlander, Jr. Bureau of Electrical and Computer Engineering in 2013 IEEE 21st Symposium on Computer Arithmetic.

- 7. An IEEE Compliant Floating-Point Adder that Conforms with the Pipelined Packet-Forwarding Paradigm by AsgerMunk Nielsen, David W.Matula, Member, IEEE Computer Society, C.N. Lyu, and Guy Even, Member, IEEE Computer Society in IEEE TRANSACTIONS ON COMPUTERS, VOL. 49, NO. 1, JANUARY 2000.